Изобретение относится к области автоматики и вычислительной техники.

Известны реверсивные счетчики, выполненные на потенциальных элементах, в которых использованы триггеры со счетным входом, общим для каналов «сложение и «вычитание, а цепи -поразрядного переноса управляются общей для счетчика схемой управления, например «триггером знака.

Такое построение схем счетчиков требует при переходе с режима «вычитание на режим «сложение и обратно выдерж,ки времени, необходимой для окончания переходных процессов ;В цепях поразрядного переноса. Это обстоятельство существенно снижает быстродействие реверсивных счетчиков.

Целью изобретения является создание реверсивного двоичного счетчика на потенциальных элементах «НЕ-ИЛИ, быстродействие которого определялось бы только разрешающей способностью триггера первого разряда и не зависело от чередования .режимов «сложение и «вычитание.

Указанная цель достигается тем, что в каждый каскад счетчика дополнительно включены инвертор и трехвходовой элемент «НЕ-ИЛИ на каждый из каналов «сложение и «вычитание.

и «вычитание, их выходы соединены с первыми входами элементов «НЕ-ИЛИ, вторые входы которых соединены с выходами «О и «1 триггера соответственно для каналов «сложение и «вычитание, а их третьи входы соединены с выходами тех элементов «НЕ-ИЛИ триггера, которые находятся в нулевом состоянии в интервалах времени между передними фронтами четных и задними фронтами нечетных входных импульсов для канала «сложение и передними фронтами нечетных и задними фронтами четных импульсов для канала «вычитание, при этом выходы дополнительных элементов «НЕ-ИЛИ являются выходами разряда по соответствующим каналам.

Такое построение схемы делает каскады независимыми один от другого, так что первые каскады могут работать на сложение, а в последних могут еще проходить импульсы по каналу «вычитание.

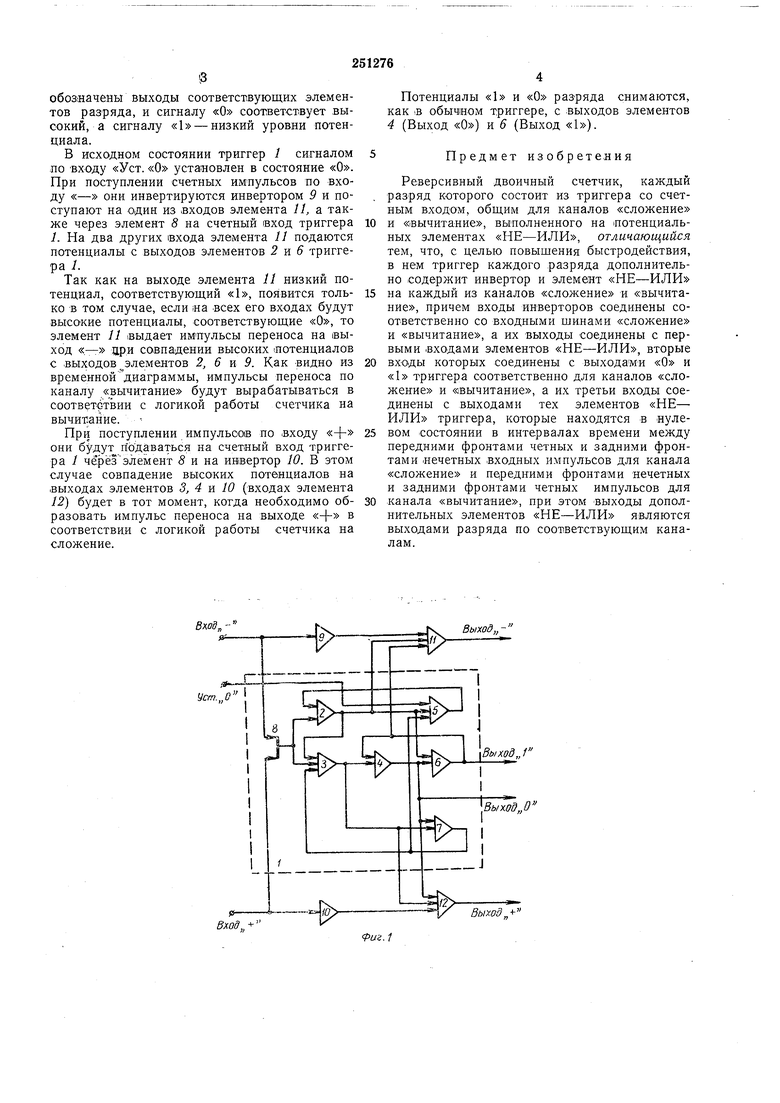

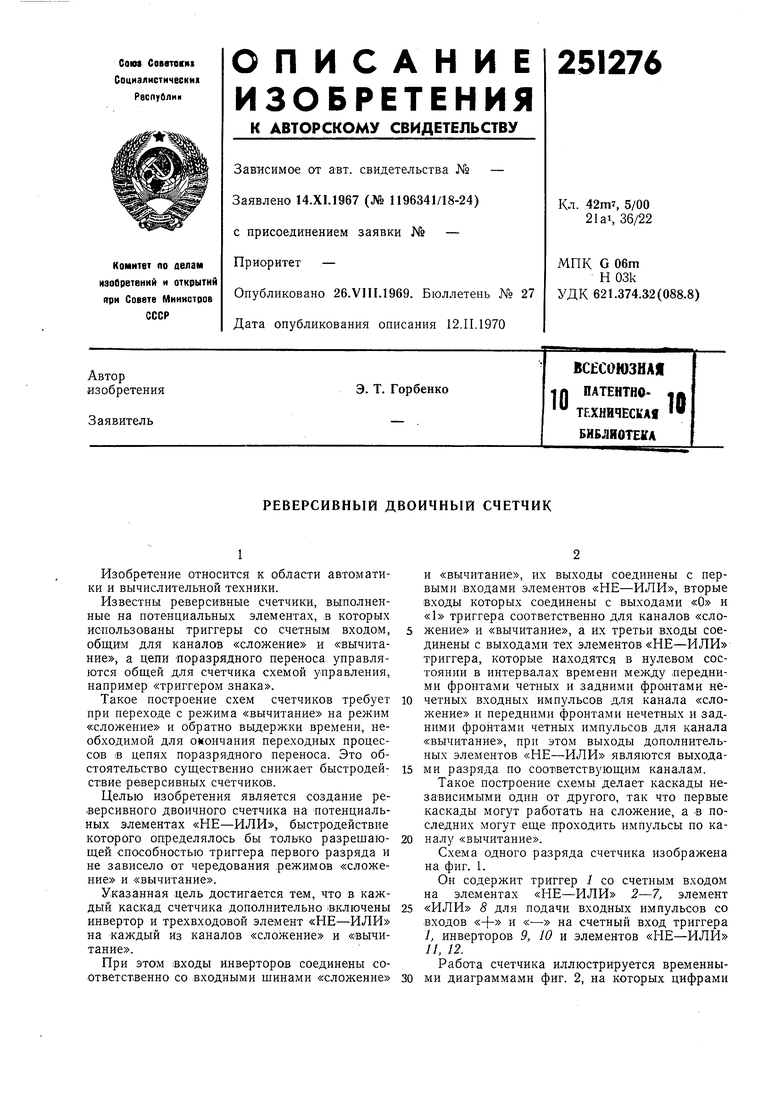

Схема одного разряда счетчика изображена на фиг. 1.

Он содержит триггер 1 со счетным входом на элементах «НЕ-ИЛИ 2-7, элемент

«ИЛИ 8 для подачи входных импульсов со

входов «-}- и «- на счетный вход триггера

/, инверторов 9, 10 и элементов «НЕ-ИЛИ

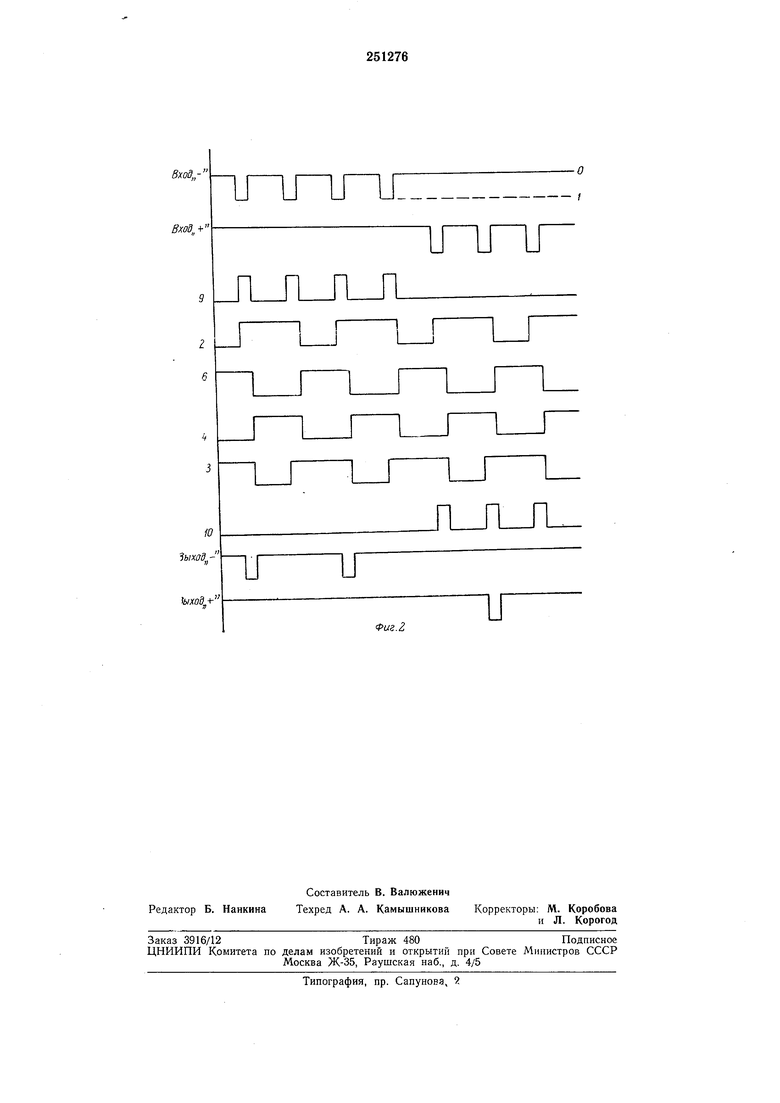

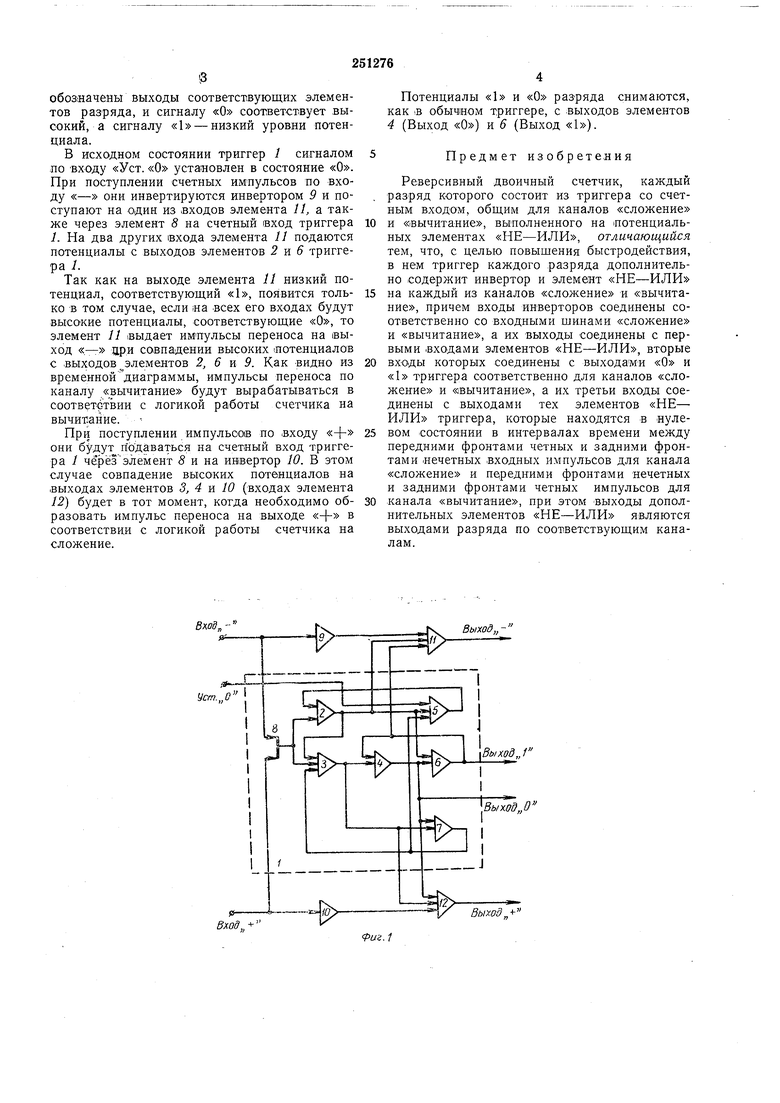

обозначены выходы соответствующих элементов разряда, и сигналу «О соответствует высокий, а сигналу «1 - низкий уровни потенциала.

В исходном состоянии триггер 1 сигналом по ВХОДУ «Уст. «О установлен в состояние «О. При поступлении счетных им пульсов по входу «- они инвертируются инвертором 9 и поступают на один из входов элемента 11, & также через элемент 8 на счетный 1вход триггера 1. На два других входа элемента // подаются потенциалы с выходов элементов 2 и триггера 1.

Так как на выходе элемента 11 низкий потенциал, соответствующий «1, появится только в том случае, если на всех его входах будут высокие потенциалы, соответствующие «О, то элемент 11 выдает импульсы переноса на выход «- ари совпадении высоких .потенциалов с выходов элементов 2, 6 и 9. Как видно из временной диаграммы, импульсы переноса по каналу «вычитание будут вырабатываться в соответствии с логикой работы счетчика на вычитание.

При поступлении импульсов по входу «4- они будут подаваться на счетный вход триггера / чфёз элемент 5 и на инвертор 10. В этом случае совпадение потенциалов на выходах элементов 3, 4 и 10 (входах элемента 12) будет в тот момент, когда необходимо образовать импульс переноса на выходе «+ в соответствии с логикой работы счетчика на сложение.

Потенциалы «1 и «О разряда снимаются, как iB обычном триггере, с выходов элементов 4 (Выход «О) и 6 (Выход «1).

Предмет изобретения

Реверсивный двоичный счетчик, каждый разряд которого состоит из триггера со счетным входом, общим для каналов «сложение и «вычитание, выполненного на потенциальных элементах «НЕ-ИЛИ, отличающийся тем, что, с целью повышения быстродействия, в нем триггер каждого разряда дополнительно содержит инвертор и элемент «НЕ-ИЛИ на каждый из каналов «сложение и «вычитание, причем входы инверторов соединены соответственно со входными шинами «сложение и «вычитание, а их выходы соединены с первыми входами элементов «НЕ-ИЛИ, вторые входы которых соединены с выходами «О и «1 триггера соответственно для каналов «сложение и «1вычитание, а их третьи входы соединены с выходами тех элементов «НЕ- ИЛИ триггера, которые находятся в нулевом состоянии в интервалах времени между передними фронтами четных и задними фронтами нечетных входных импульсов для канала «сложение и передними фронтами нечетных и задними фронтами четных импульсов для канала «вычитание, при этом выходы дополнительных элементов «НЕ-ИЛИ являются выходами разряда по соответствующим каналам.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Делитель частоты следования импульсов | 1987 |

|

SU1431069A1 |

| Устройство задержки импульсов | 1978 |

|

SU790205A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

| Устройство для контроля импульсных последовательностей | 1986 |

|

SU1338034A1 |

| Многоканальный регулятор температуры | 1991 |

|

SU1783495A1 |

Bxoff,. +

IX Выход -

ВтЗ„

О I

S.

Риг.2

Даты

1969-01-01—Публикация