Описываемое изобретение относится к области цифровой вычислительной техники.

Известны устройства для деления чисел без восстановления остатка со сдвигом остатка и частного влево, содержащие регистры делителя, делимого, остатка, два регистра частного и схему суммирования, построенные на потенциальных элементах. Педостаток известных устройств - значительный расход оборудования.

Предлагаемое устройство отличается тем, что в нем выходы регистра делителя и регистра делимого (остатка) соединены со схемой суммирования, выход регистра остатка соединен с входом регистра делимого (остатка) цепями сдвига на один разряд влево с инверсией, а выходы знаковых триггеров регистра частного соединены через две схемы «П, объединенные схемой «ИЛИ, с входом младшего разряда основного регистра частного.

Цель изобретения достигается тем, что в предлагаемом устройстве регистры делителя и делимого (остатка) соединены только со схемой суммирования, регистр.остатка соединен с регистром делимого (остатка) цепями сдвига влево и сдвига влево с инверсией, благодаря чему делитель всегда прибавляют к остатку, а в циклах вычитания инвертируют остаток.

Экономия оборудования достигается за счет того, что вместо преобразователя используется дополиительиая цепь сдвига с инверсией, а в системе потенциальных элементов ее осуществление значительно ироще, чем преобразователя, и требует меньшего оборудования.

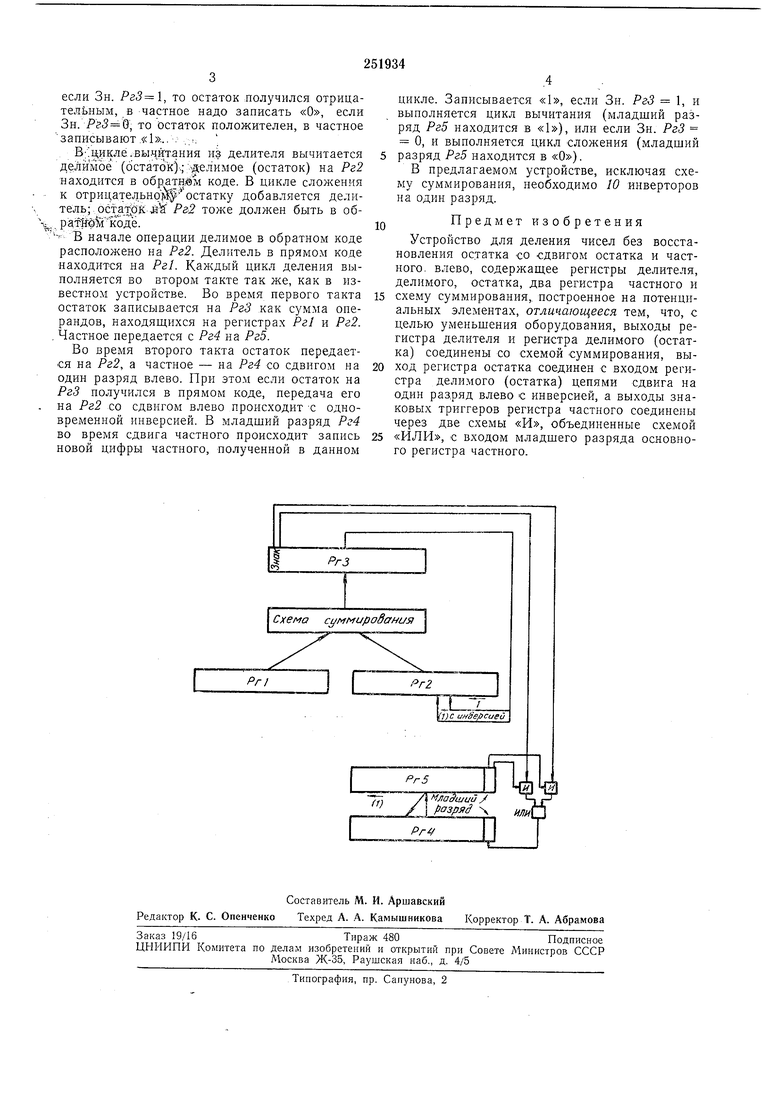

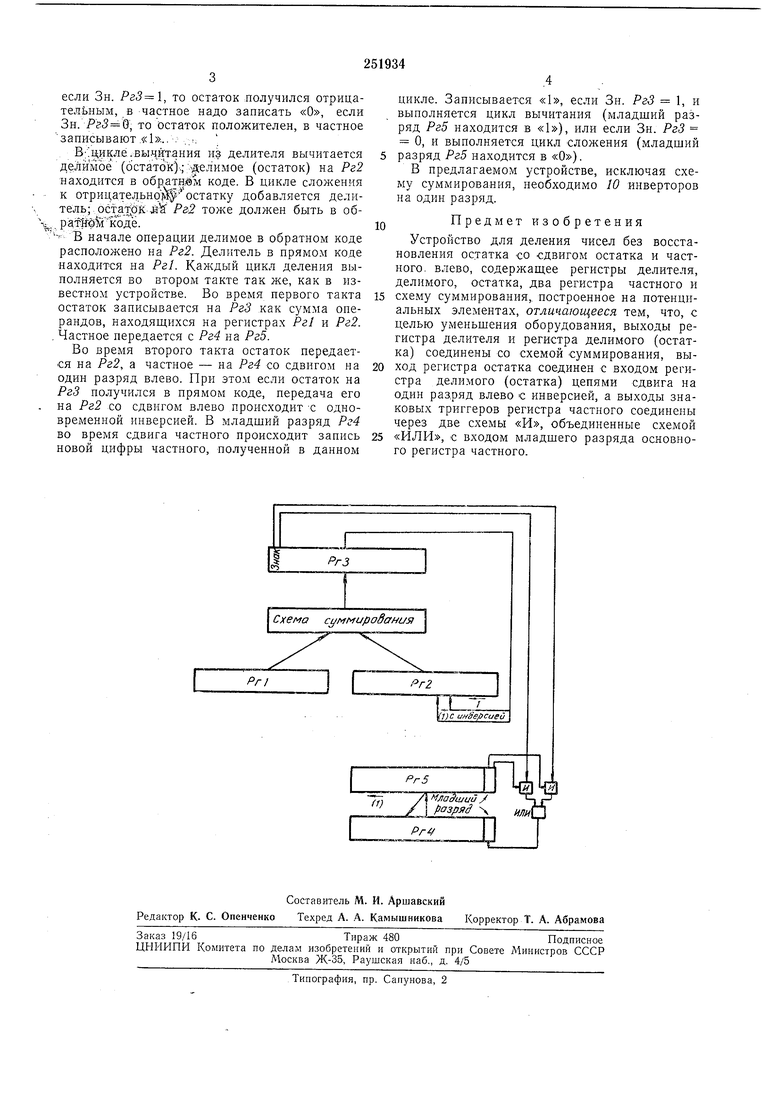

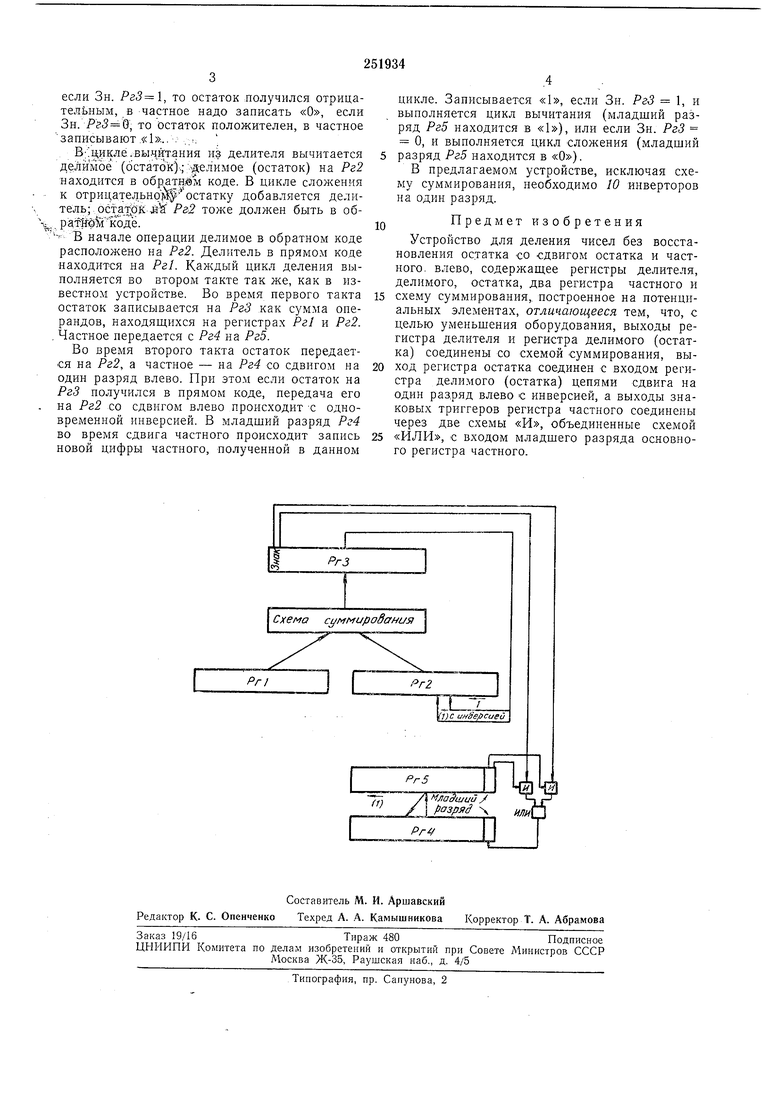

На чертеже даиа блок-схема предлагаемого устройства.

Она состоит из пяти регистров и схемы суммироваиия. И а схему суммирования заведены выходы регистров Рг1 и Рг2.

Выход регистров РгЗ соединен с входом регистра Рг2 цепями и сдвига на один разряд влево с инверсией. Выход Рг4 соединен с входом Рг5, а Рг5 - цепью сдвига на одии разряд влево с регистром Рг4.

Первым циклом всегда является цикл вычитания, причем во время вычитания из делителя вычитается делимое. Знак или код остатка,

иолученного из РгЗ, говорит о цифре частного: если Зн. РгЗ 1, то делимое по абсолютной величине больше делителя, в частное записывается «1, если Зн. РгЗ О, то делитель больше делимого, в частное записывается «О.

В цикле сложения суммируЕотся отрицательный остаток и положительный делитель. Остаток иредставляют обратным кодом на Рг2, делитель в прямом коде расположен на Рг1. Остаток снова записываются на РгЗ, по знаку

если Зн. , то остаток лолучился отрицательным, в частное надо записать «О, если Зн. , то остаток положителен, в частное записывают.«.... ..

В;;ц;икл,е.вычитания из делителя вычитается делимое (остаток).; д-елимое (остаток) на Рг2 находится в обратном коде. В цикле сложения к отрицательно / 5-остатку добавляется делитель; ,остах.оК йа РгЗ тоже должен быть в об., ратйёйкодё.

- В начале операции делимое в обратном коде расположено на Рг2. Делитель в прямом коде находится на Рг1. Каждый цикл деления выполняется во втором такте так же, как в известном устройстве. Во время первого такта остаток записывается на РгЗ как сумма операндов, находящихся на регистрах Pel и Рг2. . Частное передается с Рг4 на Рг5.

Во время второго такта остаток передается на Рг2, а частное - на Рг4 со сдвигом на один разряд влево. При этом если остаток на РгЗ получился в прямом коде, передача его

на Рг2 со сдвигом влево происходит С одновременной инверсией. В младший разряд Рг4 во время сдвига частного происходит запись новой цифры частного, полученной в данном

цикле. Записывается «1, если Зн. РгЗ 1, и выполняется цикл вычитания (младший разряд Рг5 находится в «1), или если Зн. РгЗ О, и выполняется цикл сложения (младший разряд Рг5 находится в «О).

В предлагаемом устройстве, исключая схему суммирования, необходимо 10 инверторов на один разряд.

Предмет изобретения

Устройство для деления чисел без восстановления остатка со сдвигом остатка и частного, влево, содержащее регистры делителя, делимого, остатка, два регистра частного и

схему суммирования,, построенное на потенциальных элементах, отличающееся тем, что, с целью уменьшения оборудования, выходы регистра делителя и регистра делимого (остатка) соединены со схемой суммирования, выход регистра остатка соединен с входом регистра делимого (остатка) цепями сдвига на один разряд влево с инверсией, а выходы знаковых триггеров регистра частного соединены через две схемы «И, объединенные схемой

«ИЛИ, с входом младшего разряда основного регистра частного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1746378A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Последовательное устройство для деления чисел в дополнительном коде | 1984 |

|

SU1182513A1 |

| Устройство для деления | 1980 |

|

SU898425A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

Авторы

Даты

1969-01-01—Публикация