Изобретение относится к области вычислительной техники.

Известны устройства для защиты от обращения по ложному адресу, содержащие схему сравнения, входы которой соединены с выходами регистра, дешифратор кода адреса и логические схемы «И и «ИЛИ.

Однако такие устройства сложны, так как, кроме указанных элементов, содержат наконитель.

Предложенное устройство отличается от известных тем, что для упрощения устройства в нем одни входы всех схем «И соединены с выходами дещифратора кода адреса, другие входы соединены с источниками сигналов нуля и единицы, а выходы схем «И через схемы «ИЛИ соединены со входами схемы сравнения.

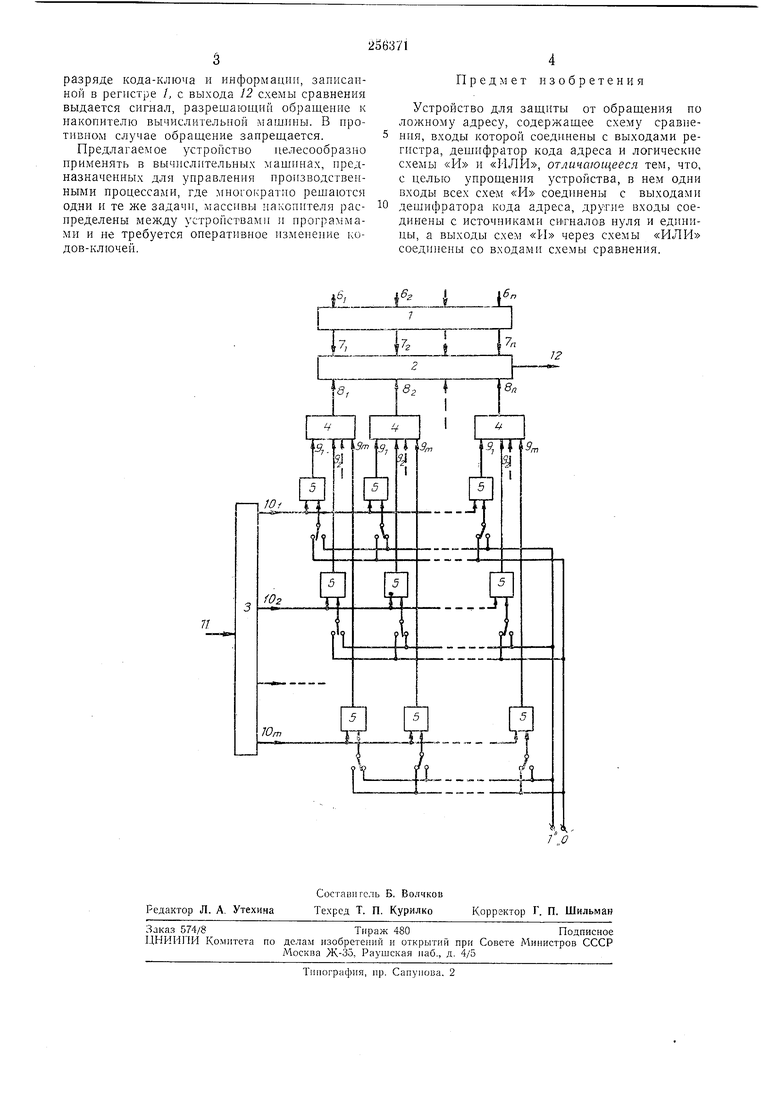

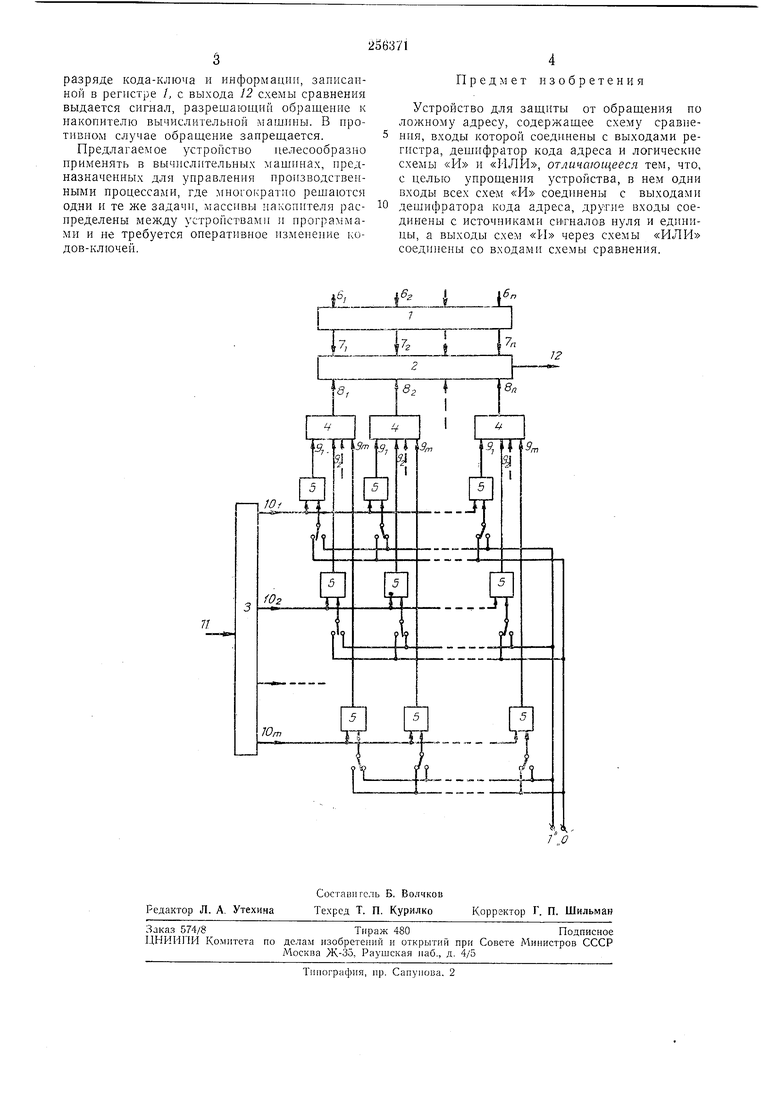

На чертеже дана схема предлагаемого устройства защиты.

Оно содержит разрядный накопительный регистр 1, схему сравнения 2, дешифратор 3 адреса, собирательные схемы 4 и двухкодовые схемы совпадения 5.

К одним входам схемы сравнения 2 подключены выходы 7i-f 7„ регистра /, а к другим - выходы 81 + 8„ собирательных схем 4. На входы каждой собирательной схемы 4 подключены выходы 9i , схем совпадения 5, относящихся к одному разряду. К одному из .входов схем

совпадения 5 подключается одна из т выходных щин W дещифратора адреса 3, (где т- число массивов накоиителя вычислительной мащины), а к другому входу схем совиадения 5 через коммутирующий элемент или запаянным монтажом подаются выходы от источника сигиалов «i или источника сигналов «О. Посредством коммутирующих элементов или постоянного монтажа набирается код-ключ,

соответствующий определенному массиву накопителя вычислительной машины. Для каждого кода-ключа отводится один горизонтальный ряд схем совпадения 5.

Перед обращением (лли серией сбраи1.ен1п)

подается сигнал «1 на вход 6 регистра / в разряд, соответствующий определенному устройству (группе устройств) или определенной программе (группе программ), которые будут обращаться к накопителю вычислительной мащины.

При обращении адрес информацнп одновременно с подачей в накоиитель вычислительной машины подается на вход И дешифратора адреса 3. При этом появляется сигнал на одно11

из шин 10 дещифратора адреса 3, соответствующей номеру массива, в котором находится данная ииформация. Этот сигнал разрещаег передачу кода-ключа данного массива на входы 8 схемы сравнения 2. разряде кода-ключа и информации, записанной в регистре /, с выхода 12 схемы сравнения выдается сигнал, разрешаюидий обращение к накопителю вычислительной машииы. В иротивном случае обращение занрещается. Предлагаемое устройство целесообразно применять в выч 1слительных мащннах, предназначенных для управления производственными процессами, где многократно рещаются одни и те же задачи, массивы накопителя раснределены между устройствами и программами и не требуется оперативиое изменение кодов-ключей. Предмет изобретения Устройство для защиты от обращения по ложному адресу, содержащее схему сравнения, входы которой соединены с выходами регистра, дещифратор кода адреса и логические схемы «И и «ИЛИ, отличающееся тем, что, с целью упрощения устройства, в нем одни входы всех схем «И соединены с выходами дешифратора кода адреса, другие входы соединены с источниками сигналов нуля и единицы, а выходы схем «И через схемы «ИЛИ соединены со входами схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1986 |

|

SU1336102A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| ШАГОВЫЙ ГРАФОПОСТРОИТЕЛЬ | 1970 |

|

SU267216A1 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Устройство для вывода информации | 1974 |

|

SU526879A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280456A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1280455A1 |

Авторы

Даты

1969-01-01—Публикация