Изобретение относится к вычислительной технике и может быть использовано при обмене информацией в многопроцессорных вычислительных системах.

Цель изобретения - повышение надежности устройства.

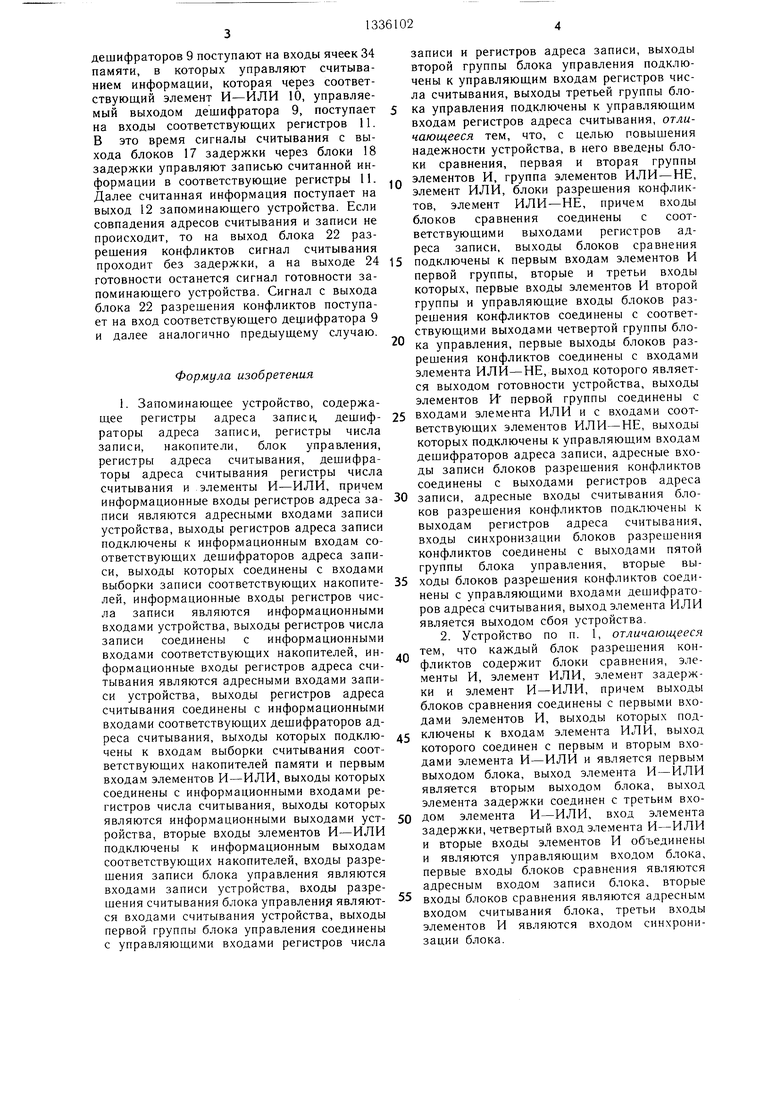

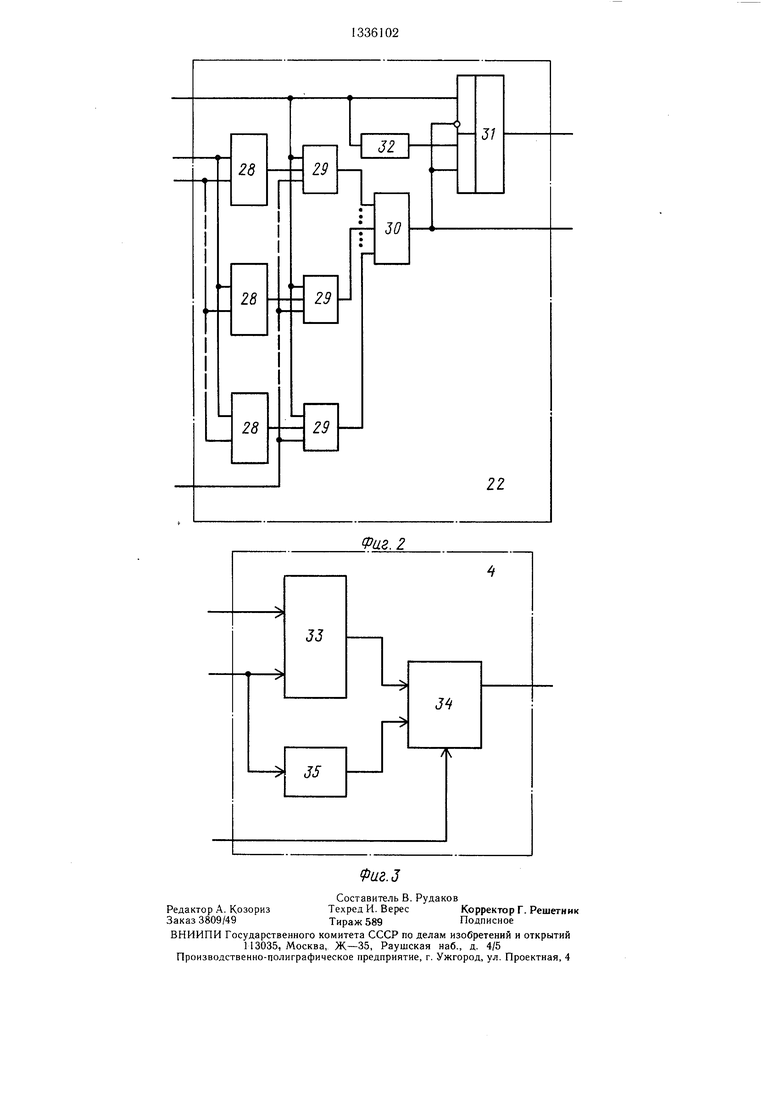

На фиг. 1 приведена структурная схема запоминающего устройства; на фиг. 2 - структурная схема блока разрешения конфликтов; на фиг. 3 - структурная схема накопителя.

Запоминающее устройство (фиг. 1) содержит регистры 1 адреса записи, информационные входы которых являются адресными входами 2 записи устройства, дешифраторы 3 адреса записи, накопители 4, регистры 5 числа записи, информационные входы которых являются информационными входами 6 устройства, регистры 7 адреса считывания, информационные входы которых являются адресными входами 8 считывания, дешифраторы 9 адреса считывания, элементы И - ИЛИ 10, регистры 11 числа считывания, выходы которых являются информационными выходами 12 устройства, блок 13 управления, входы разрешения записи и считывания которого являются соответственно входами записи 14 и считывания 15 устройства. Блок управления содержит блоки 16-18 задержки.

Устройство также содержит блоки 19 сравнения, первую 20 и вторую 21 группы элементов И, блоки 22 разрешения конфликтов, элемент ИЛИ - НЕ 23, выход которого является выходом 24 готовности устройства, элемент ИЛИ 25, выход которого является выходом 26 сбоя устройства, и группу элементов ИЛИ-НЕ 27.

Каждый блок 22 разрешения конфликтов (фиг. 2) содержит блоки 28 сравнения, элементы И 29, элемент ИЛИ 30, элемент И-ИЛИ 31 и элемент 32 задержки.

Каждый накопитель 4 (фиг. 3 содержит элемент И-ИЛИ 33, ячейку 34 памяти и элемент ИЛИ 35.

Запоминающее устройство является мно- говходовым и предназначено для оперативного обмена между абонентами и для хранения системных массивов и таблиц в многопроцессорных вычислительных системах.

Запись информации в устройство осуществляется следующим образом. Абоненты- источники по входам 2 подают адресные коды на входы регистров 1, а коды чисел по входам 6 - на входы регистров 5. Эти коды сопровождаются соответствующими сигналами записи, поступающими от блока 13. Кроме этого, сигналы записи поступают на входы блоков 22 разрешения конфликтов для определения конфликтов при одновременной записи и считывания по одному и тому же адресу и на соответствующие входы элементов И 20. В блоках 19 производится попарное сравнение каждого с каждым адресом записи. Если одновременно приходят сигналы записи от i-ro и j-ro абонентов по одному адресу, то на ij-м блоке 19 вырабатывается сигнал совпадения, который поступает на ij-й элемент И 20 и далее на ij-e входы i-ro и j-ro элементов ИЛИ-НЕ 27, выходы которых блокируют на i-M и J-M элементах И 21 сигналы с i-ro и j-ro выходов элементов 16 задержки на

управление дещифратором 3. Кроме того, с i-ro и j-ro элементов И 20 сигналы поступают на элемент ИЛИ 25, выход которого является выходом 26 сбоя устройства. Если одновременной -записи с несколь5 ких направлений по одному и тому же адресу нет, то элементы ИЛИ-НЕ 27 раз- рещают прохождение сигналов с выходов блока 13 управления на управляющие входы дещифраторов 3. Сигналы с выходов выбранных выходов дешифраторов 3 посту0 пают на входы накопителей 4, в которых управляют прохождением числа через элемент И-ИЛИ 33 с выходов регистров на числовой вход ячейки 34 памяти, а через элемент ИЛИ 35 устанавливают в ней режим записи.

Чтение информации осуществляется следующим образом.

Абоненты-приемники по входам 8 подают коды адреса на входы регистров 7. Эти коды сопровождаются соответствующими сигQ налами считывания, поступающими из блока 13. Сигналы считывания через блоки 17 задержки поступают на входы блока 22 раз- рещения конфликтов, в которых на блоках 28 производится сравнение одного адреса считывания, поступающего с выходов регисте ров 7, со всеми адресами записи. При совпадении адресов считывания и записи и одновременном обращении к накопителям 4 по записи и считыванию на одно.м из элементов И 29 появится сигнал, который через элемент ИЛИ 30 скоммутирует эле0 мент И-ИЛИ 31 таким образом, что на его выходе сигнал считывания появится задержанным на один цикл обращения к накопителю 4.

Кроме того, сигналы с выходов элемента ИЛИ 30 поступают на элемент ИЛИ-НЕ 23, выход которого является выходом 24 готовности запоминающего устройства. При обнаружении конфликта на выходе 24 готовности устанавливается низкий уровень, который запрещает обращение от

Q абонентов-источников на один цикл обращения к накопителю 4.

Таким образом, в конфликтной ситуации обращение на запись в накопителе 4 проходит без задержки, а обращение на считывание и разрешение обращений от або5 нентов-источников задерживается на один цикл обращения к накопителю 4. Выход эле.мента И-ИЛИ 31 откроет соответствующий дешифратор 9. Сигналы с выходов

дешифраторов 9 поступают на входы ячеек 34 памяти, в которых управляют считыванием информации, которая через соответствующий элемент И-ИЛИ 10, управляемый выходом дешифратора 9, поступает на входы соответствующих регистров 11. В это время сигналы считывания с выхода блоков 17 задержки через блоки 18 задержки управляют записью считанной информации в соответствующие регистры 11. Далее считанная информация поступает на выход 12 запоминающего устройства. Если совпадения адресов считывания и записи не происходит, то на выход блока 22 разрешения конфликтов сигнал считывания проходит без задержки, а на выходе 24 готовности останется сигнал готовности запоминающего устройства. Сигнал с выхода блока 22 разрешения конфликтов поступает на вход соответствующего дещифратора 9 и далее аналогично предыущему случаю.

Формула изобретения

1. Запоминающее устройство, содержащее регистры адреса записи, дешифраторы адреса записи, регистры числа записи, накопители, блок управления, регистры адреса считывания, дешифраторы адреса считывания регистры числа считывания и элементы И-ИЛИ, причем информационные входы регистров адреса записи являются адресными входами записи устройства, выходы регистров адреса записи подключены к информационным входам соответствующих дешифраторов адреса записи, выходы которых соединены с входами выборки записи соответствующих накопителей, информационные входы регистров числа записи являются информационными входами устройства, выходы регистров числа записи соединены с информационными входами соответствующих накопителей, информационные входы регистров адреса считывания являются адресными входами записи устройства, выходы регистров адреса считывания соединены с информационными входами соответствующих дешифраторов адреса считывания, выходы которых подключены к входам выборки считывания соответствующих накопителей памяти и первым входам элементов И-ИЛИ, выходы которых соединены с информационными входами регистров числа считывания, выходы которых являются информационными выходами устройства, вторые входы элементов И-ИЛИ подключены к информационным выходам соответствующих накопителей, входы разрешения записи блока управления являются входами записи устройства, входы разрешения считывания блока управления являются входами считывания устройства, выходы первой группы блока управления соединены с управляющими входами регистров числа

записи и регистров адреса записи, выходы второй группы блока управления подключены к управляющим входам регистров числа считывания, выходы третьей группы блока управления подключены к управляющим входам регистров адреса считывания, отли- чающееся тем, что, с целью повышения надежности устройства, в него введены блоки сравнения, первая и вторая группы

Q элементов И, группа элементов ИЛИ-НЕ, элемент ИЛИ, блоки разрешения конфликтов, элемент ИЛИ-НЕ, причем входы блоков сравнения соединены с соответствующими выходами регистров адреса записи, выходы блоков сравнения

5 подключены к первым входам элементов И первой группы, вторые и третьи входы которых, первые входы элементов И второй группы и управляющие входы блоков разрешения конфликтов соединены с соответствующими выходами четвертой группы бло ка управления, первые выходы блоков раз- рещения конфликтов соединены с входами элемента ИЛИ-НЕ, выход которого является выходом готовности устройства, выходы элементов И первой группы соединены с

5 входами элемента ИЛИ и с входами соответствующих элементов ИЛИ-НЕ, выходы которых подключены к управляющим входам дешифраторов адреса записи, адресные входы записи блоков разрешения конфликтов соединены с выходами регистров адреса

0 записи, адресные входы считывания блоков разрешения конфликтов подключены к выходам регистров адреса считывания, входы синхронизации блоков разрешения конфликтов соединены с выходами пятой группы блока управления, вторые вы5 ходы блоков разрешения конфликтов соединены с управляющими входами дешифраторов адреса считывания, выход элемента ИЛИ является выходом сбоя устройства.

2. Устройство по п. 1, отличающееся тем, что каждый блок разрешения конфликтов содержит блоки сравнения, элементы И, элемент ИЛИ, элемент задержки и элемент И-ИЛИ, причем выходы блоков сравнения соединены с первыми входами элементов И, выходы которых под5 ключены к входам элемента ИЛИ, выход которого соединен с первым и вторым входами элемента И-ИЛИ и является первым выходом блока, выход элемента И-ИЛИ является вторым выходом блока, выход элемента задержки соединен с третьим вхо0 дом элемента И-ИЛИ, вход элемента задержки, четвертый вход элемента И-ИЛИ и вторые входы элементов И объединены и являются управляющим входом блока, первые входы блоков сравнения являются адресным входом записи блока, вторые

5 входы блоков сравнения являются адресным входом считывания блока, третьи входы элементов И являются входом синхронизации блока.

0

Фиг.г

Фаг. J

Составитель В. Рудаков

Техред И. ВересКорректор Г. Решетник

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Редактор А. Козориз Заказ 3809/49

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1336118A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Вычислительная система | 1989 |

|

SU1734101A1 |

| Запоминающее устройство | 1989 |

|

SU1695382A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU942140A1 |

| Устройство для сопряжения вычислительной машины с объектами управления | 1979 |

|

SU1040482A1 |

| Устройство для параллельной передачи информации | 1990 |

|

SU1795465A1 |

| Графическое запоминающее устройство | 1989 |

|

SU1667154A1 |

Изобретение относится к вычислительной технике и может быть использовано при обмене информацией в многопроцессорных вычислительных системах. Цель изобретения - повышение надежности устройства. Запоминающее устройство содержит регистры 1 адреса записи, накопители 4, регистры 5 числа записи, регистры 7 адреса, дешифраторы 9 адреса считывания, элементы И-ИЛИ 10, регистры 11 числа считывания, блок 13 управления, блоки 19 сравнения, первую 20 и вторую 21 группы элементов И, блоки 22 разрешения конфликтов, элемент ИЛИ-НЕ 23, элемент ИЛИ 25 и группу элементов ИЛИ-НЕ 27. В устройстве производится выявление ошибок при одновременной записи чисел с нескольких направлений по одному и тому же адресу, выявление и устранение неправильного считывания чисел при одновременной записи и считывание информации по одному и тому же адресу. 1 з. п. ф-лы, 3 ил. i (Л со со С5 fus. I

| Запоминающее устройство современных ЭЦВМ./Под ред | |||

| А | |||

| А | |||

| Крупского | |||

| М.: Мир, 1968, с | |||

| ПАРОПЕРЕГРЕВАТЕЛЬ ДЛЯ ЛОКОМОБИЛЬНЫХ КОТЛОВ | 1912 |

|

SU277A1 |

| Запоминающее устройство | 1976 |

|

SU932567A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-14—Подача