1

Изобретение относится к вычислительной технике, в частности к постоянным запоминающим устройствам.

Цель изобретения - снижение потребляемой мощности и повышение надежности.

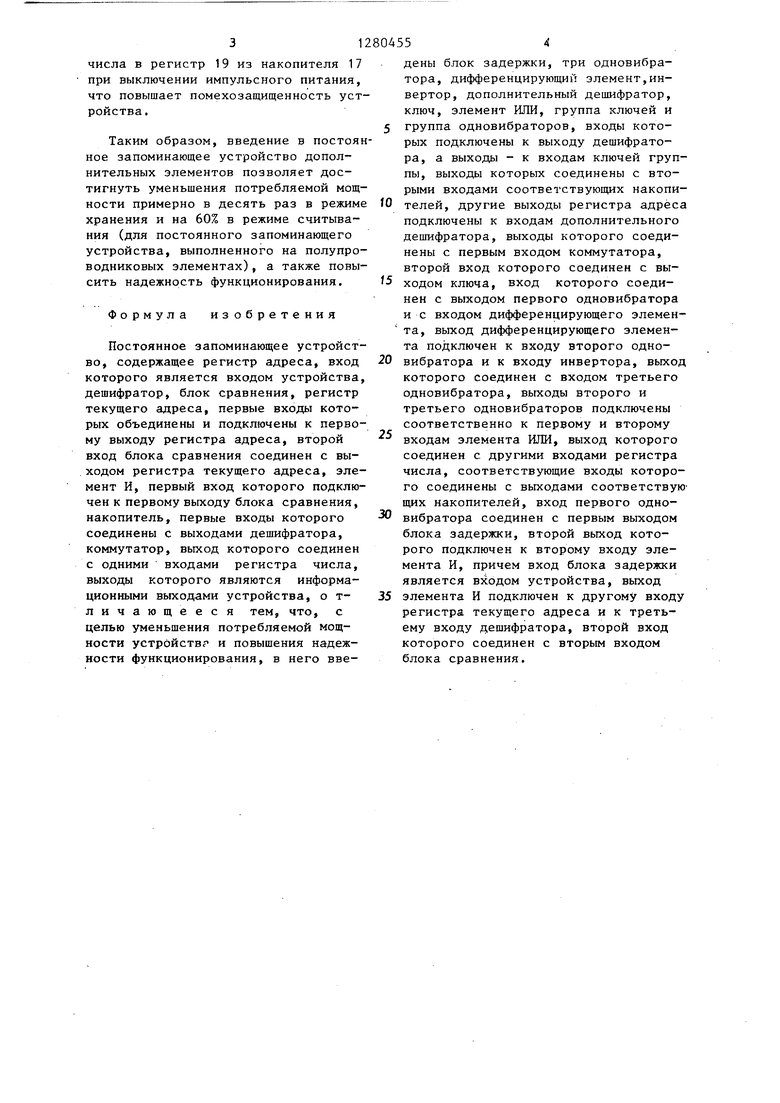

На чертеже приведена функциональная схема устройства.

Устройство содержит регистр адреса 1, регистр текущего адреса 2, блок сравнения 3, дещифратор 4, элемент 5 и; блок 6 задержки, первый одновибратор 7, ключ 8 (импульсного питания), дифференцирующий элемент 9, второй одновибратор 10, инвертор 11, третий одновибратор 12, элемент 13 ИЛИ, коммутатор 14, дополнительный дешифратор 15, группу одновиб- раторов 16, накопитель 17, группу ключей 18, регистр числа 19, вход регистра адреса 1 является входом устройства, выходы регистра числа 19 являются выходом устройства.

1

Устройство работает следующим образом.

На регистр адреса 1 в режиме считывания поступает код адреса числовой ячейки накопителя 17, а на иход блока задержки 6 - сигнал обращения к устройству.

С выходов регистра адреса 1 код старших разрядов подается на первый вход блока 3, входы дешифратора 4 и входы регистра 2, а код младших разрядов поступает на входы дополнительного дешифратора 15. На второй вход блока 3 подается код с выходов регистра текущего адреса 2.

Если при сравнении адресов, находящихся в старших разрядах регистра 1 и на регистре 2, будет получен сигнал равнозначности, то сигнал с второго выхода блока 3 поступает на второй управляющий вход дешифратора 4 и запрещает его работу. При этом не будет запущена группа одновибра- торов 16, группа ключей импульсного питания 18, а следовательно, не произойдет выборки чисел из накопителя 17. Таким образом, несмотря на обращение, питание накопителей будет отключено, что существенно уменьшает потребляемую накопителями 17 мощность в постоянном запоминающем устройстве, особенно в случае использования запоминающих элементов на полупроводниковой основе. В этом случае запускается первый одновибратор 7

тания и

вого регистра

fO

f5

2804352

по сигналу с блока задержки 6. Срабатывает ключ импульсного питания 8 и на коммутатор 14 подается импульс пи- адрес выбранной части числос дополнительного дешифратора 15. Информация, хранящаяся в одной из частей числового регистра 19, передается на выход устройства.

В случае несравнения кода, находящегося в старших разрядах регистра адреса 1 ci кодом адреса, хранящимся в регистре текущего адреса 2,ни второй вход дешифратора 4 не подается запрещающий сигнал с второго выхода блока сравнения 3, а на первый вход элемента 5 И с первого выхода блока сравнения 3 поступает разрешающий потенциал, на второй вход элемента 5 И поступает управляющий сигнал с блока 6. На выходе элемента 5 И появляется сигнал, который подается на вторые входы регистра 2 и третий вход дешифратора 4. За счет этого в регистр текущего адреса 2 записывается новый код адреса и происходит дешифрация старших разрядов .кЬда адреса в дешифраторе 4, после чего запускается группа одновибраторов 16 и группа ключей импульсного питания 18. На одни входы накопителя 17 поступает .код выбранной ячейки с дешифратора 4, а на другие входы накопителя 17 подаются импульсы напряжения питания с группы ключей импульсного питания 18.

20

25

30

35

Происходит обращение ко всем ячейкам накопителя 17 и считывание из

них информации. Чтобы не происходила запись в регистр 19 неправильной информации во время переходных процессов в накопителе 17 при включении импульсного питания, с помощью одновибратора 7 за счет ди(})фе- ренцирующего элемента 9 срабатывает одновибратор 10, который через элемент ИЛИ 13 запрещает прием, числа в регистр 19 из накопителя 17. Входные

цепи регистра 19 будут отключены от накопителя 17 и в моменты выключения импульсного питания за счет того, что в этом случае продифференцированный задний фронт управляющего сигнала, поступающего с одновибратора 7, подается на инвертор 11 и далее на запуск одновибратора 12.Выходной сигнал с одновибратора 12 через элемент ИЛИ 13 запрещает прием

числа в регистр 19 из накопителя 17 при выключении импульсного питания, что повышает помехозащищенность устройства.

Таким образом, введение в постоянное запоминающее устройство дополнительных элементов позволяет достигнуть уменьшения потребляемой мощности примерно в десять раз в режиме хранения и на 60% в режиме считывания (для постоянного запоминающего устройства, выполненного на полупроводниковых элементах), а также повысить надежность функционирования.

Формула изобретения

Постоянное запоминающее устройство, содержащее регистр адреса, вход которого является входом устройства, дешифратор, блок сравнения, регистр текущего адреса, первые входы которых объединены и подключены к первому выходу регистра адреса, второй вход блока сравнения соединен с выходом регистра текущего адреса, элемент И, первый вход которого подключен к первому выходу блока сравнения, накопитель, первые входы которого соединены с выходами дешифратора, коммутатор, выход которого соединен с одними входами регистра числа, выходы которого являются информационными выходами устройства, о т- личающееся тем, что, с целью уменьшения потребляемой мощности устройствг и повышения надежности функционирования, в него вве

O 5

5

0

5

0

дены блок задержки, три одновибра- тора, дифференцирующими элемент,инвертор, дополнительный дешифратор, ключ, элемент ИЛИ, группа ключей и группа одновибраторов, входы которых подключены к выходу дешифратора, а выходы - к входам ключей группы, выходы которых соединены с вторыми входами соответствующих накопителей, другие выходы регистра адреса подключены к входам дополнительного дешифратора, выходы которого соединены с первым входом коммутатора, второй вход которого соединен с выходом ключа, вход которого соединен с выходом первого одновибратора и с входом дифференцирующего элемента, выход дифференцирующего элемента подключен к входу второго одно- вибратора и к входу инвертора, выход которого соединен с входом третьего одновибратора, выходы второго и третьего одновибраторов подключены соответственно к первому и второму входам элемента ИЛИ, выход которого соединен с другими входами регистра числа, соответствующие входы которого соединены с выходами соответствую щих накопителей, вход первого одно- вибратора соединен с первым выходом блока задержки, второй выход которого подключен к второму входу элемента И, причем вход блока задержки является входом устройства, выход элемента И подключен к другому входу регистра текущего адреса и к третьему входу дешифратора, второй вход которого соединен с вторым входом блока сравнения.

Редактор Н. Горват

Составитель Л. Амусьева

Техред В.Кадар Корректор О. Луговая

Заказ 7057/46 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1984 |

|

SU1236553A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Устройство для контроля микросхем постоянной памяти | 1987 |

|

SU1478258A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Запоминающее устройство с защитой памяти | 1982 |

|

SU1019494A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1247949A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| ШАГОВЫЙ ГРАФОПОСТРОИТЕЛЬ | 1970 |

|

SU267216A1 |

Изобретение относится к вычислительной технике и может быть использовано, в частности, при создании постоянных запоминающих устройств. Целью изобретения является уменьшение потребляемой мощности и повышение надежности. Устройство содержит регистр адреса, регистр текущего адреса, блок сравнения, дешифраторы, основной и дополнительный блок задержки, одновибраторы, инвертор, элемент И, элемент ИЛИ, ключ, группу одновибраторов, накопитель, группу ключей, регистр числа. Введение группы одновибраторов, группы ключей, дополн 1тельного дешифратора, ключа и группы ключей обеспечивает отключение питания накопителя и коммутатора в режиме хранения,а в режиме считывания обеспечивает подачу питания только в момент несравнения информации, поступившей на регистр адреса, с информацией предыдущего обращения, хранящейся в регистре текущего адреса. 1 ил. (О to 00 о 4: СП сд

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| Машиностроение, 1974, с | |||

| Питательное приспособление к трепальным машинам для лубовых растений | 1922 |

|

SU201A1 |

| Долговременное запоминающее устройство | 1979 |

|

SU765878A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-30—Публикация

1985-06-28—Подача