Изобретение относится к области вычислительной техники, в частности к устройствам для табличной обработки даиных.

Известны диодно-матричные коммутаторы, в которых каждая строка матрицы, выполненной на диодах, подключена к управляющему ключу, через который подается питание только в выбранную строку в момент срабатывания.

Недостатком известных устройств является то, что быстродействие ограничено «аличием паразитных емкостей диодов и монтажа.

В -предлагаемом устройстве повышение быстродей:ствия достигается тем, что к -выходу коммутатора подсоединен управляемый ключ, форсирующий переходные процессы после окончания выходного сигнала.

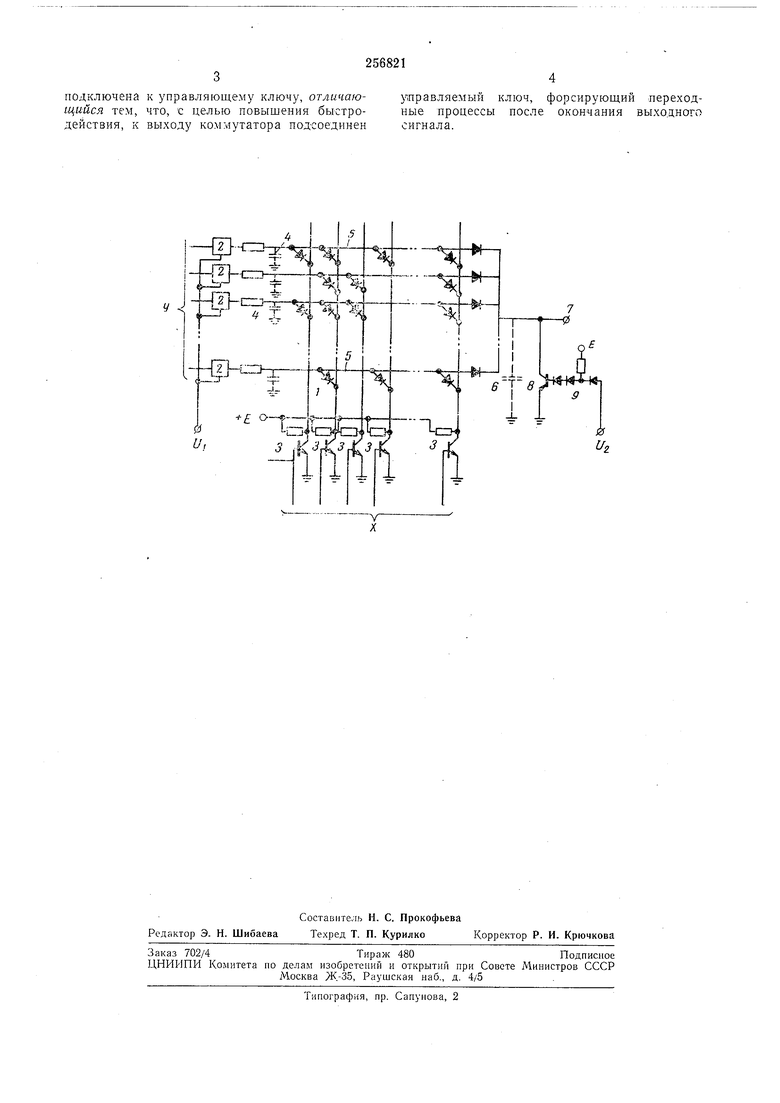

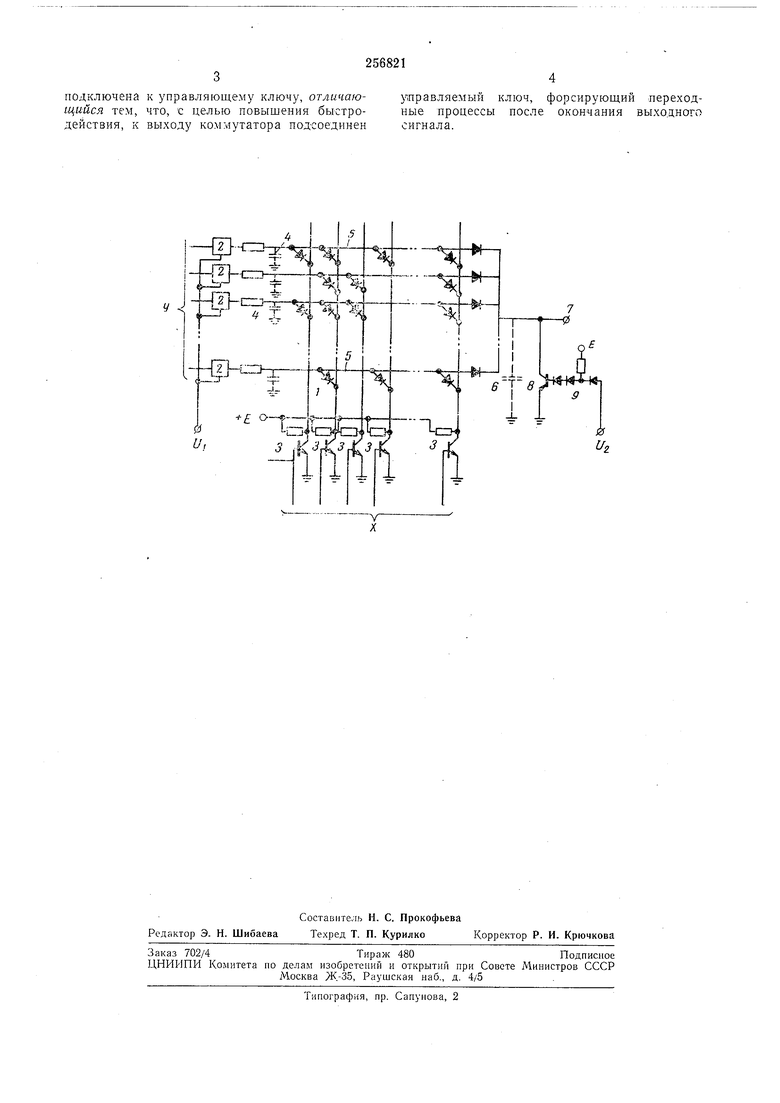

На чертеже приведена одна из возможных схем диодно-матричного коммутатора для табличной обработки данных, реализующего функцию установки в одиночное состояние одного из разрядов регистра выхода, на который записывается результат табл-ичной обработки операндов.

Устройство работает следующим образом.

На матрицу, содержащую диоды /, но координате У подается однорядовый код одного из операндов через ключи 2, управляемые по второму входу стробирующим импульсом t/i. Импульс Ui пройдет только через один ключ 2, на который поступает входной сигнал координаты Y.

По координате X второй операнд подается в виде инверсного однорядового кода на входы инверторов 3, при этом на всех выходах, кроме одного, будут высокие уровни напряжения. Быстродействие диодно-матричного комлгутатора определяется временем заряда эквивалентной паразитной емкости 4 каждой стро-ки матрицы 5 и временем разряда эквивалентной емкости 6 всей матрицы на выходе.

Для увеличения быстродействия днодноматричного коммутатора на выходе 7 матрицы подключен ключ, выполненный на транзисторе 8 и диодах 9 и стробируемый импульсом Uz. В качестве ключа может быть использован обычный инвертор. В момент действия им;пульса Lz происходит разряд емкости 6 через малое сопротивление открытого транзистора 8. Постоянная разряда в этом случае будет значительно меньще, чем при ОТСУТСТВИИ ключа.

25

Предмет изобретения

подключена к управляющему ключу, отличающийся тем, что, С целью повышения быстродействия, к выходу коммутатора подсоединен

управляемый ключ, форсирующий переходные процессы после окончания выходного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство | 1977 |

|

SU684613A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Каскадное устройство ортогонального типа для сдвигов многоразрядных операндов | 1989 |

|

SU1661757A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство для ввода информации | 1978 |

|

SU785864A1 |

| Матричный коммутатор | 1974 |

|

SU530459A1 |

и,

Даты

1969-01-01—Публикация