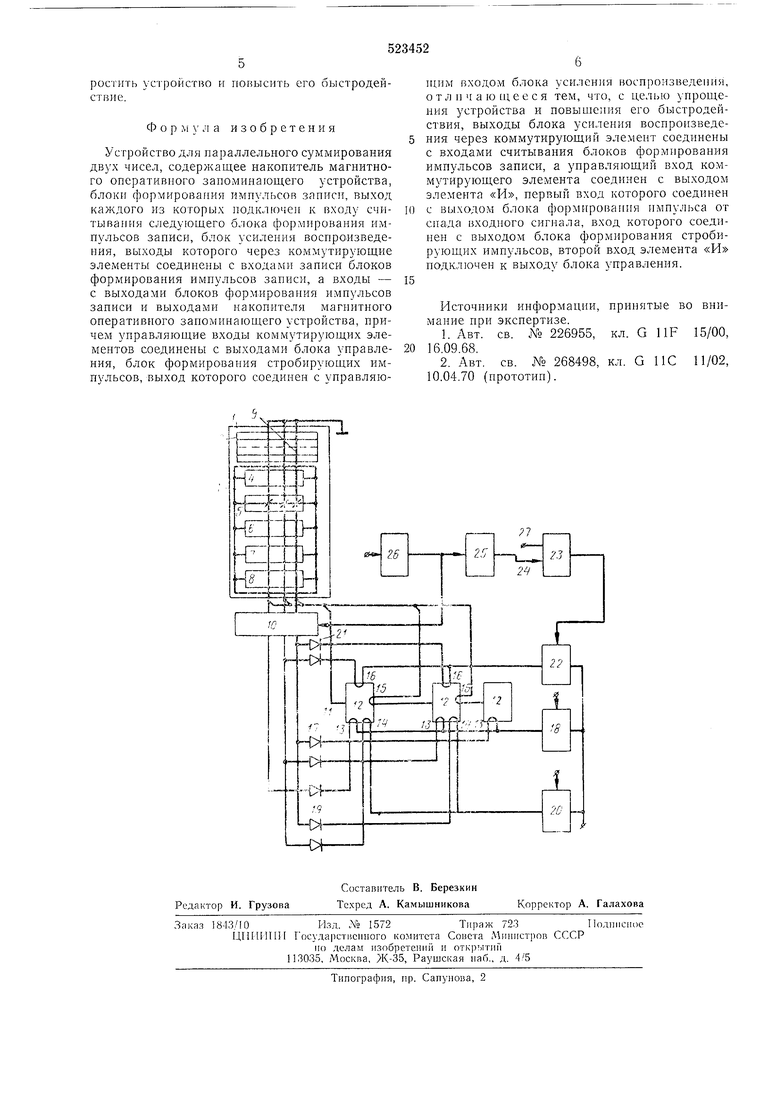

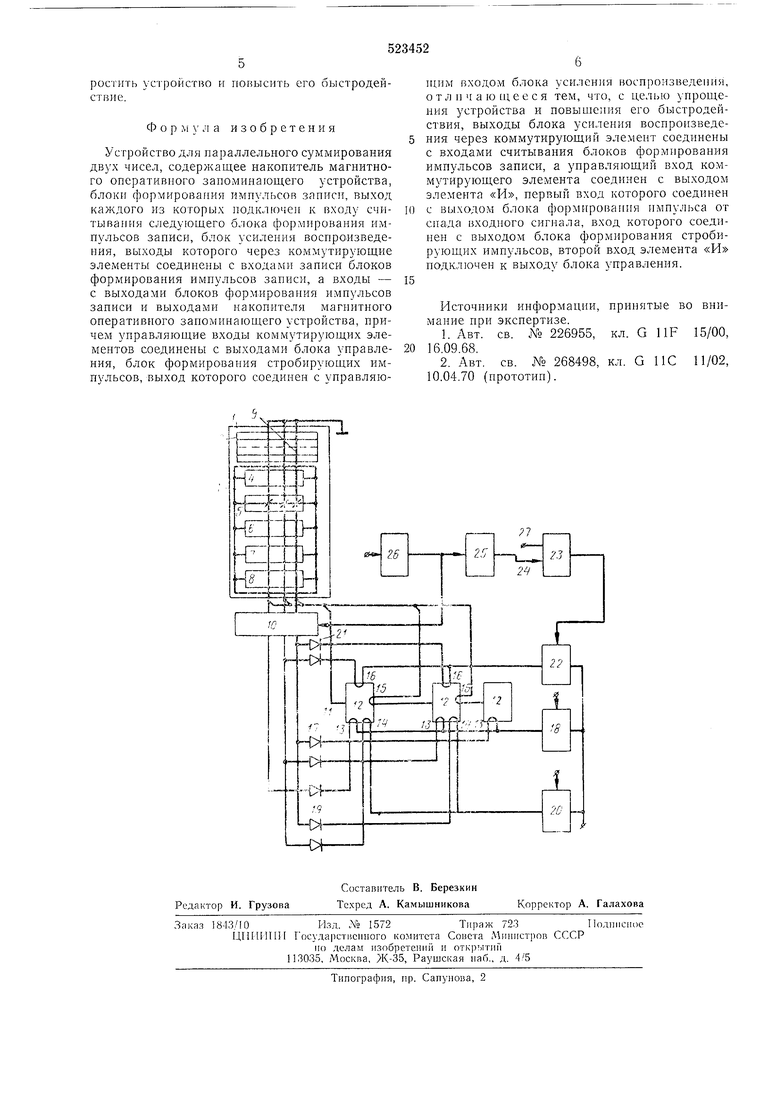

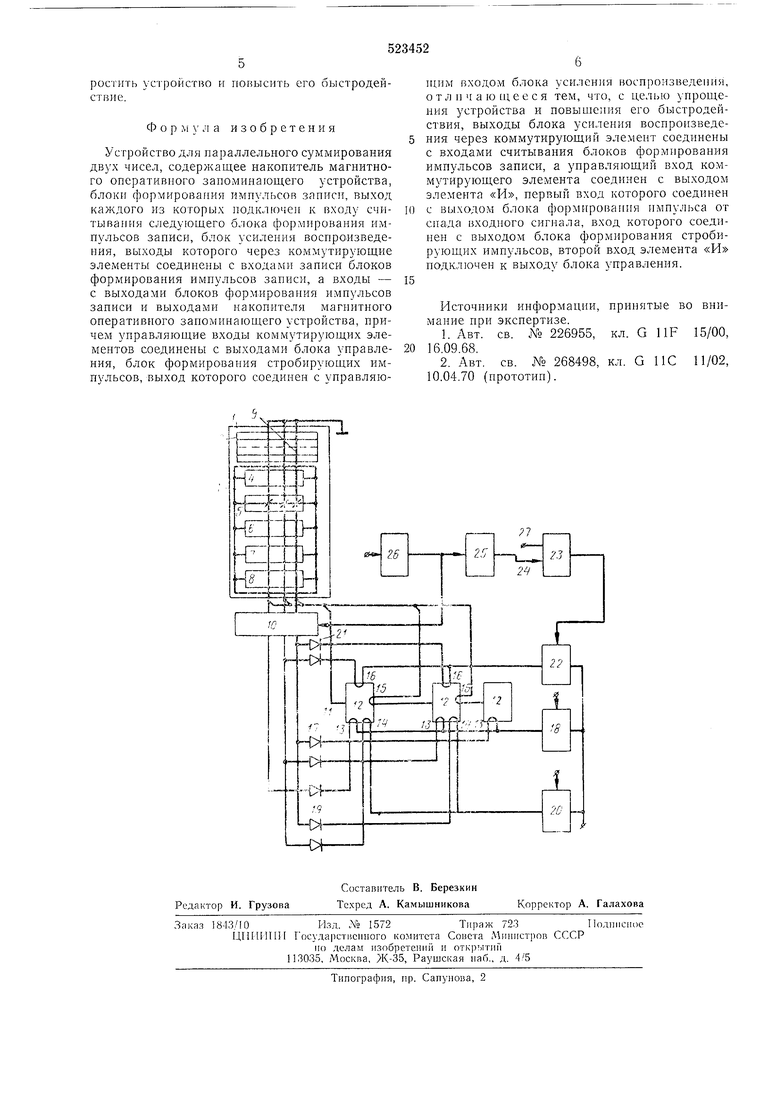

соединены к реверсивным ключам. В ячейках 4-8 выполняются поразрядные логические функцни «И, «ИЛИ, «ИЕ. Разрядные шины 9, общие для обоих блоков 2 и 3 накопителя МОЗУ, соединены с входа.мн блока 10 усиления воспроизведения, а таюке с выходами 11 блоков 12 формирования имнульсов записи. Блоки формирования импульсов записи выполняют также функцию регистра числа (регистра регенерации). В качестве таких блоков могут служить, например, магнитно-транзисторные элементы, использующие для запоминания магнитные сердечники с прямоугольной петлей гистерезиса. Блок формирования импульсов записи имеет входы записи 13, 14 и считывания 15, 16. Вход 13 блока 12 формирования импульсов записи i-ro разряда подключен через диод 17 к выходу i-ro разряда блока 10 усиления воспроизведения, а с другой стороны входы 13 всех разрядов - к коммутирующему элементу 18. Вход 14 f-ro разряда через диод 19 подсоединен к выходу (i-1)-го разряда блока 10, а с другой стороны входы 14 - коммутирующему элементу 20. Вход 16 считывания г-го разряда через диод 21 подключен к выходу (г-1)-го разряда блока 10, с другой стороны входы 16 - к коммутирующему элементу 22. Вход 15 блока формирования импульсов записи i-ro разряда соединеп с выходом 1 аналогичного блока (/-1)-го разряда. Управляющий вход коммутирующего элемента 22 связан с выходом элемента «И 23, вход 24 которого подключен к выходу блока 25формирования имнульса от спада входного сигнала, вход блока 25 - с выходом блока 26формирования стробирующих импульсов, соединенным также с управляющим входом блока 10 усиления воспроизведения. Управляющие входы коммутирующих элементов 18, 20, блока 26, а также вход 27 элемента «И 23 подсоединены к соответствующим выходам блока управления, не показанного на чертеже. Суммирование двух двоичных чисел в предлагаемом устройстве выполняется за пять обращений к МОЗУ по следующему алгоритму: ввод числа а в специально выделенные для выполнения логических операций линейки МОЗУ; ввод числа b в те же линейки с получением выражений вычисление слова переносов по формуле P/-M ()(«AVA);(1) вычисление 5; по формуле 5r----V AV«A,(2) где Si - предварительная сумма без учета переносов; вычисление суммы Ei по формуле E,, Рассмотрим работу предлагаемого устройства при образовании слова переносов по формуле (1) в третьем цикле обран1,ения к накопителю согласно приведенному алгоритму. Перед началом третьего цикла слово uiV Ь записано в ячейках 4 и 5 фуикционального блока 3 накопителя МОЗУ 1, а слово uibi в ячейках 6 и 7. В первом такте третьего цикла проводится считывание ячейки 4. Одновременно возбуждается блок 26 формирования стробирующих импульсов и открывается коммутирующий элемент 20. Поскольку на вход 27 элемента «И 23 сигнал не поступает, то элемент 22 остается невозбужденным. На выходах блока 10 усиления воспроизведения появляется считанное слово OjV&j. Со сдвигом на один разряд влево через диоды оно записывается в блоки формирования импульсов записи. Во втором такте третьего цикла происходит считывание ячейки 6. Одновременно возбуждается блок 26 формирования стробирующих импульсов и подается сигиал на вход 27 элемента «И. От спада стробирующего импульса блок 25 формирует импульс на выходе, который поступает на вход 24 элеме1гга «И 23, на выходе последнего образуется импульс, возбуждаюи ий элемент 22. Таким образом, элемент 22 возбуждается с задержкой, равной длите;п ности стробирующего импульса. На выходах блока 10 усиления воспроизведения появляется считанное слово )i. В момент замыкания элемента 22 код считанного слова со сдвигом на один разряд влево через диоды 21 поступает на входы 16 считывания блоков 12. При этом те блоки 12 формирования импульсов записи, на входы 16 которых поступил импульс, формируют на выходе 11 импульс записи, так как в первом такте в них была записана «единица кодом uiV Ь{. Выходной импульс блока формирования импульсов записи /г-го разряда считывает блок формирования импульсов записи следующего ()-ro разряда. Таким образом, возбуждается волна переноса. Код на выходах 11 соответствует слову переносов Pi+i, вычисленному по формуле (1). Импульсы записи с выходов 11 поступают в разрядные шины 9 накопителя МОЗУ 1. Одиовременно формируются импульсы адресных токов записи в ячейках 4 и 8, в результате чего слово переносов записывается в эти ячейки. Длительность импульсов тока в адресных шинах должна быть больше длительности импульсов тока в разрядных шинах на величину максимальной задержки распространения волны переноса от младшего разряда до старшего. Задержка считывания блоков формирования импульсов записи во втором такте, обеспечиваемая блоком 25, необходима для того, чтобы исключить влияние помех в разрядных шинах 9 от имнульсов записи на работу блока 10 усиления воспроизведения. Осуществлеие необходимой задержки с помощью блоков 5, 23, связанных с блоком 26, позволяет уп

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

Авторы

Даты

1976-07-30—Публикация

1974-08-14—Подача