Предложенное устройство относится к области вычислительной техники и предназначено для суммирования чисел в десятичном коде.

Известен накопительный десятичный сумматор, содержащий преобразователь фазового представления кода в число импульсов, фазоимпульсный элемент памяти с элементами «ИЛИ и цепь формирования импульса переноса, Содержащую триггер с раздельными входами и элемент «И.

Однако в таком сумматоре исключение ошибки при суммировании чисел я переноса достигается за счет разнесения во времени импульса пачки и импульса переноса, что уменьшает быстродействие сумматора.

Предложенное устройство отличается тем, что в нем цепь формирования импульса переноса содержит триггер со счетным входом и элемент «И, причем счетный вход триггера соединен с выходом фазоимпульсного элемента памяти, выход триггера соединен с одним из входов элемента «И, с другим входом которого соединена шина импульсов опроса.

Это Позволяет повысить быстродействие сумматора за счет того, что импульс переноса выдается в момент опросного импульса.

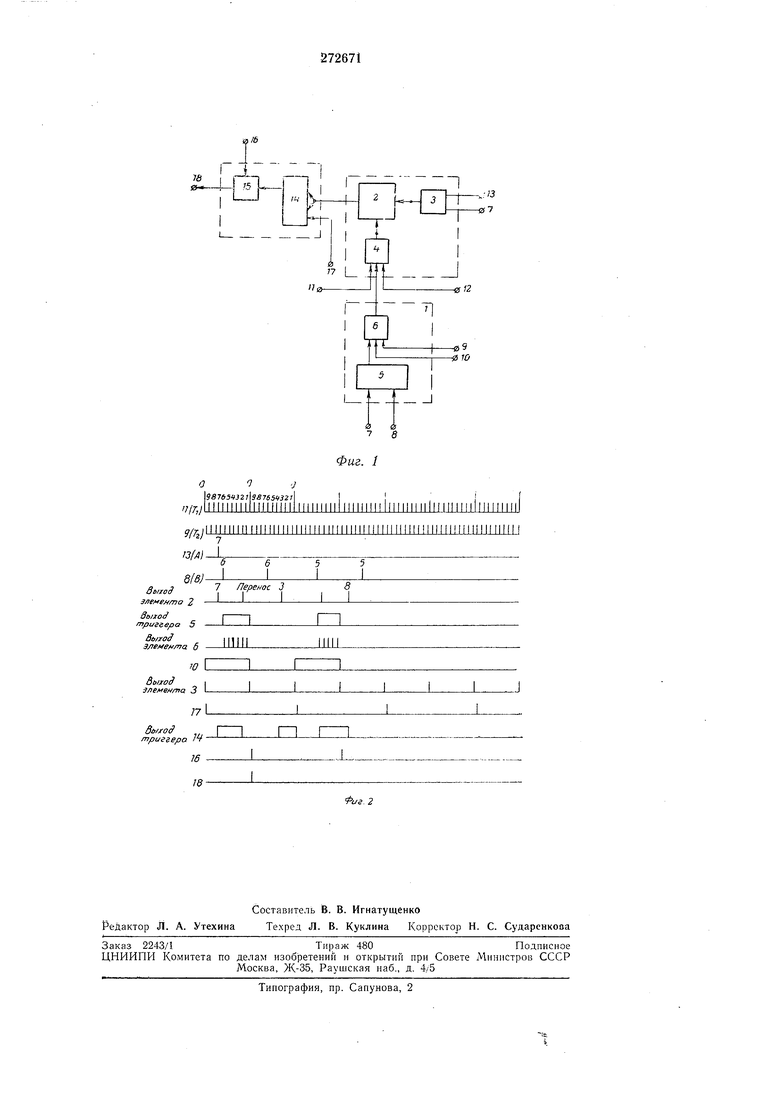

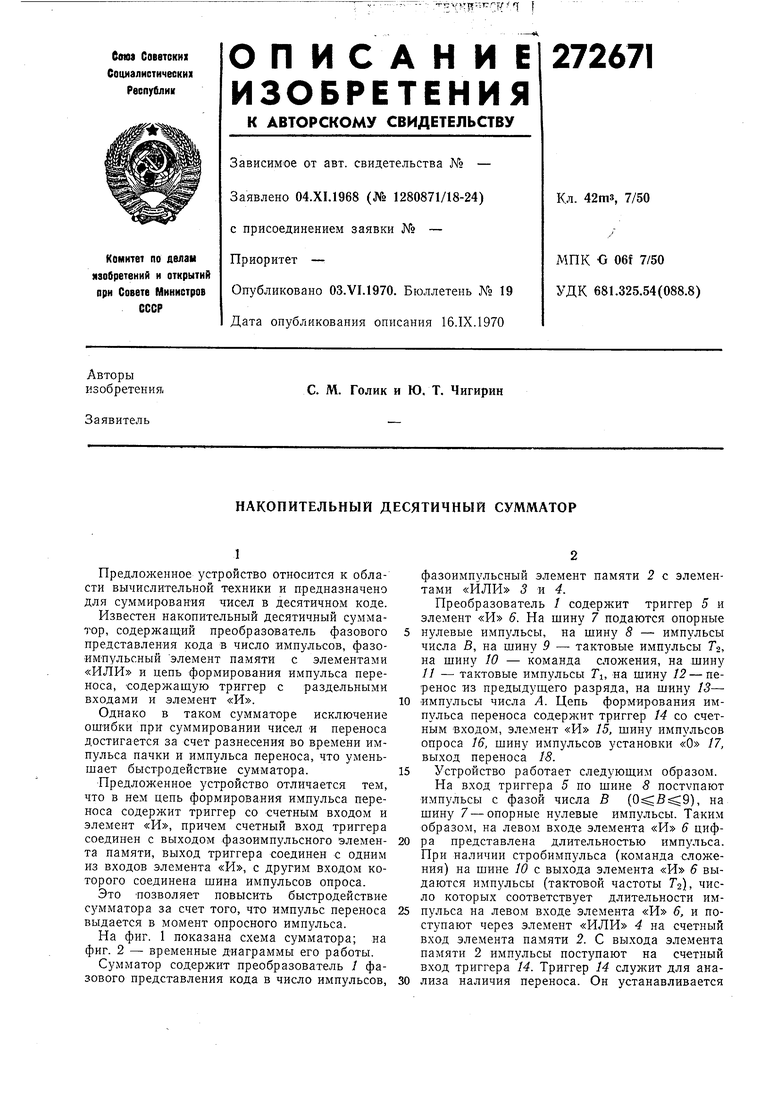

На фиг. 1 показана схема сумматора; на фнг. 2 - временные диаграммы его работы.

фазоимпульсный элемент памяти 2 с элементами «ИЛИ 3 и 4.

Преобразователь / содержит триггер 5 и элемент «И 6. На шину 7 подаются опорные

нулевые импульсы, на шину 8 - импульсы числа В, на шину 9 - тактовые импульсы Га, на шину 10 - команда сложения, на шину // - тактовые импульсы Т, на шину 12 - перенос из предыдущего разряда, на шину 13-

импульсы числа А. Цепь формирования импульса переноса содержит триггер 14 со счетным -входом, элемент «И 15, шину импульсов опроса 16, шину импульсов установки «О 17, выход переноса 18.

Устройство работает следующим образом.

На вход триггера 5 по шине 8 поступают импульсы с фазой числа В (), на шину 7 - опорные нулевые импульсы. Таким образом, на левом входе элемента «И 6 цифра представлена длительностью импульса. При наличии стробимпульса (команда сложения) на шине 10 с выхода элемента «И 6 выдаются импульсы (тактовой частоты TZ , число которых соответствует длительности импульса на левом входе элемента «И 6, и поступают через элемент «ИЛИ 4 на счетный вход элемента памяти 2. С выхода элемента памяти 2 импульсы поступают на счетный вход триггера 14. Триггер 14 служит для анав нулевое состояние импульсами по шине 17, частота которых в два раза меньше частоты нулевых опорных импульсов. Если /l + , то в течение интервала времени от момента установки триггера 14 в «О до опорного нулевого импульса один нмпульс с выхода элемента памяти 2 поступает на счетный вход триггера 14. Триггер 14 устанавливается в единичное состояние и выдает запрещающий потенциал, поступающий с выхода триггера на вход элемента «И 15. На второй вход элемента «И 15 по шине 16 поступает импульс опроса с частотой, в два раза меньшей частоты нулевых опорных импульсов, сдвинутый на полпериода счетных тактовых импульсов относительно нулевой опорной частоты. В этом случае на выходе 18 элемента «И 15 импульс переноса отсутствует. Если , то в течение интервала времени от момента установки триггера 14 в нулевое состояние до опорного нулевого импульса С выхода элемента памяти поступают на счетный вход триггера 14 два импульса. Первый импульс устанавливает триггер 14 в единичное состояние, а второй возвращает его в нулевое состояние. С выхода триггера 14 выдается разрещающий потенциал, поступающий на вход элемента «И 15. Прн поступлении импульса опроса по шине 16 на выходе 18 элемента «И 15 появляется импульс переноса. Предмет изобретения Накопительный десятичный сумматор, содержащий преобразователь фазового представления кода в число импульсов, фазоимпульсный элемент памяти с элементами «ИЛИ и цепь формирования импульса переноса, отличающийся тем, что, с целью повыш.ения быстродействия, цепь формирования импульса переноса содержит триггер со счетным входом и элемент «И, причем счетный вход триггера соединен с выходом фазоимпульсного элемента памяти, выход триггера соединен с одним из входов элемента «И, с другим входом которого соединена шина импульсов опроса.

987654321

3S76S432t

IT,I

9fr,)

/J//Jj-i

8le)

7 Перенос 3

Stifzod

JL I II лемеято 2

ts/noJ риггера 5

Str/ro элемента 6

Bbijfo8I

злемента 3 L.

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ, НРЕДСТАВЛЕННЫХ ФАЗОИМПУЛЬСНЫМИ ДЕСЯТИЧНЫМИ КОДАМИ | 1973 |

|

SU384104A1 |

| СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ | 1971 |

|

SU322855A1 |

| УСТРОЙСТВО для УСТАНОВКИ ЗАПЯТОЙ СУММИРУЮЩЕЙ КЛАВИШНОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1973 |

|

SU367419A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Счетчик импульсов | 1978 |

|

SU746949A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК | 1973 |

|

SU362490A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU972591A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

Даты

1970-01-01—Публикация