Изобретение относится к цифровой вычислительной технике.

Известны цифровые дифференциальные анализаторы (ЦДА) носледовательного типа, содержащие запоминающее устройство с произвольной выборкой, блок интегрирования, имеющий Л-регнстр, У-регистр, устройство суммирования и вычитания, входы dx, dy и выход dz, регистр приращений dz с рядом выходов и вентильных входов, блок команд, содержащий коммутирующую схему, включающую Зстройство выбора информации интеграторов.

Недостатком известных устройств является больщая погрещность, низкое быстродействие н малая гибкость.

Предлагаемое устройство отличается от известных тем, что оно содержит иерархнческую вентильную схему управления, состоящую из ряда вентилей управления и вентилей переноса, причем первый вход каждого вентиля управления подсоединеи к едииичному входу управления иерархической веитилыюй схемой управления, первый вход каждого веитиля переиоса подключен к нулевым входам управления иерархической вентильной схемой управления; ко вторым входам каждого из вентилей управления и переноса подсоединен выход вентиля переноса предыдущего более старшего (рааряда, а ко вторым входам вентилей улравлснпя и переноса старщего разряда регистра приращ,ення dz подключен источник тактовых импульсов, выходы вентилей управления соединеиы с выходами управленгя иерархической вептяльной схемы, JR-регистр блока интегрирования содержит дополнительный выход займа старшего разряда, иодсоедпненный к выходу dz блока, единичные н нулевые выходы соответствующего триггера регистра приращенкя связаны с единичными и нулевыми входами управления иерархической вентильной схемы, выходы управления нодсоединены ко входам dz блока команд, выход блока интегрирования подключен к вентильным входам

регистра приращений.

Другим отличием предлагаемого устройства является набор групп входных коммутаторных гнезд по три гнезда в группе, набор выходных командных гнезд и гнезд считывания, линии

задержки и коммутаториые шнуры с одннм входным и двумя выходными концами; нричем первое гнездо каждой группы входных коммутаторных гнезд нодсоединено к одному входу dz блока команд, второе гнездо через линию

задержки подключено к первому, а третье гнездо через линию задержки подсоединено ко второму, каждое командное гнездо dx связано с одним из выходов блока команд, каждое гнездо считытывания блока команд, входной конец коммутаторных шнуров подключен к соответствующим входным коммутаторным гнездам, однн выходной конец коммутаторных шнуров нодключен к соответствующему командному гнезду, а другой - к гнездам счнтывания.

Это нозволяет уменьшить иогрешность, увеличить быстродействие и гибкость устройства.

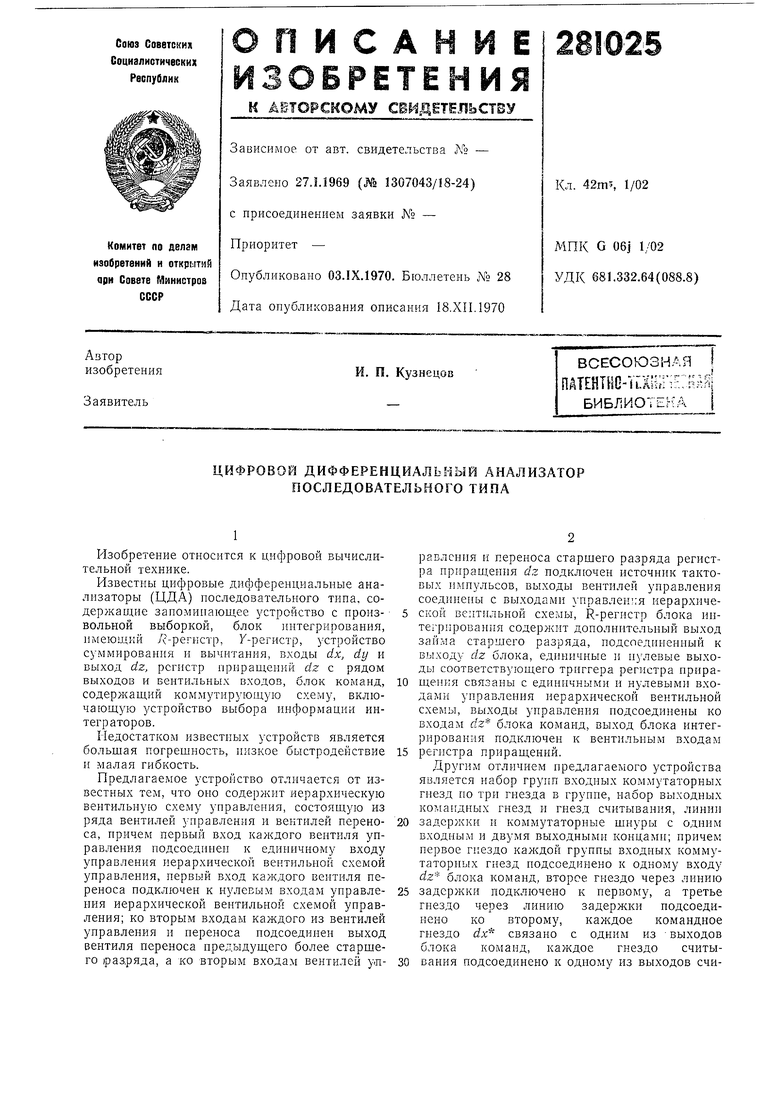

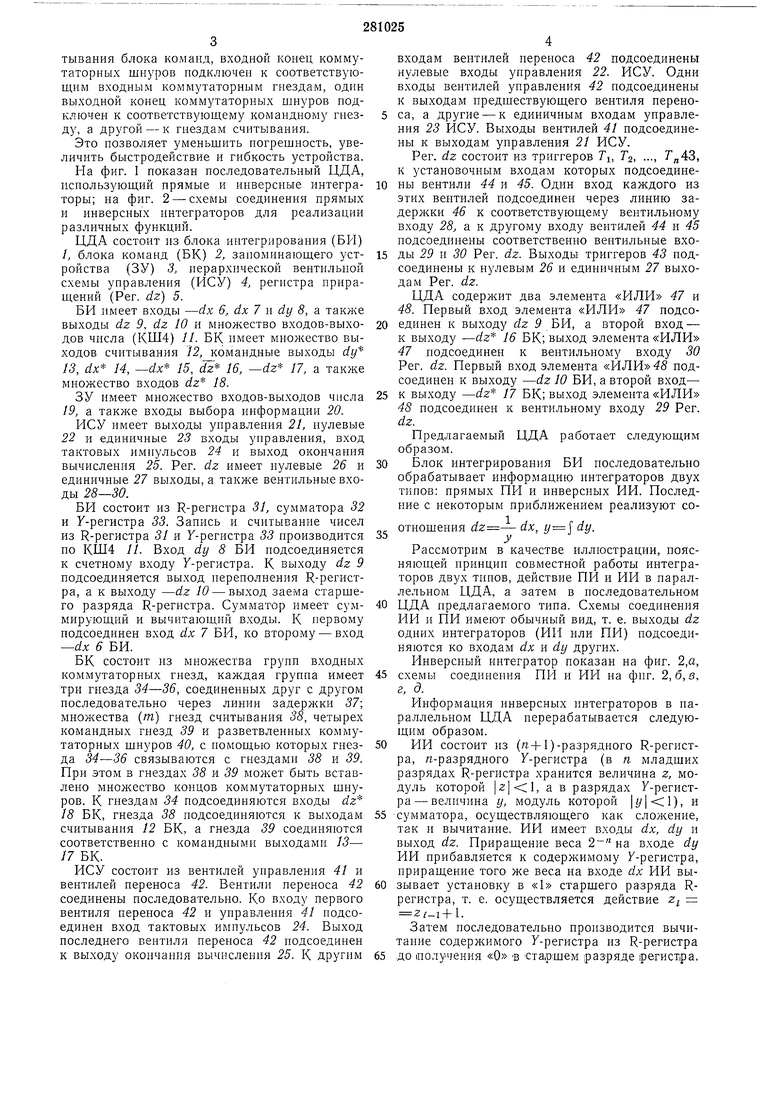

На фиг. 1 показан последовательный ЦДА, использующий прямые и инверсные интеграторы; ца фиг. 2 - схемы соединения црямых и инверсных интеграторов для реализации различных функций.

ЦДА состоит на блока интегрирования (БИ) /, блока команд (БК) 2, заноминающего устройства (ЗУ) 3, иерархической веитильной схемы управления (ИСУ) 4, регистра приращений (Per. dz) 5.

БИ имеет входы -dx 6, dx 7 и dy 8, а также выходы dz 9, dz 10 и множество входов-выходов числа (КШ4) 11. БК имеет множество выходов считывания 12, командные выходы dy 13, dx 14, -dx 15, dz 16, -dz 17, a также множество входов dz 18.

ЗУ имеет множество входов-выходов числа 19, а также входы выбора информации 20.

ИСУ имеет выходы уиравления 21, цулевые 22 и единичные 23 входы унравлеиия, вход тактовых импульсов 24 и выход окончания вычисления 25. Per. dz нмеет нулевые 26 и единичные 27 выходы, а также вентильные входы 28-30.

БИ состоит из R-регистра 31, сумматора 32 и У-регистра 33. Запись и считывание чисел из R-регистра 31 и F-регистра 33 производится но КШ4 11. Вход dy 8 БИ иодсоединяется к счетному входу У-регистра. К выходу dz 9 подсоединяется выход нереполнения R-регистра, а к выходу -dz 10 - выход заема старшего разряда R-регистра. Сумматор имеет суммирующий и вычитающий входы. К первому подсоединен вход dx 7 БИ, ко второму - вход -dx 6 БИ.

БК состоит из мнол ества груип входных коммутаторных гнезд, каждая группа имеет три гнезда 34-36, соединенных друг с другом иоследовательно через линии задержки 57; множества (т) гнезд считывания 38, четырех командных гнезд 39 и разветвлеииых коммутаторных шнуров 40, с иомощью которых гнезда 34-36 связываются с гнездами 55 и 39. При этом в гнездах 55 и 39 может быть вставлено множество концов коммутаторных шнуров. К гнездам 34 подсоединяются входы dz 18 БК, гнезда 55 иодсоединяются к выходам считывания 12 БК, а гнезда 39 соедиияются соответственно с команднымн выходами 13- 17 БК.

ИСУ состоит из вентилей уиравления 41 и вентилей переноса 42. Вентили переноса 42 соединены последовательно. Ко входу первого вентиля переноса 42 и уиравлення 41 иодсоедииен вход тактовых импульсов 24. Выход последнего вентиля переноса 42 подсоединен к выходу окончания вычисления 25. К другим

входам вентилей переноса 42 подсоединены нулевые входы управления 22. ИСУ. Одни входы вентилей управления 42 подсоедииеиы к выходам предществующего вентиля иерено5 са, а другие - к единичным входам управления 23 ИСУ. Выходы вентилей 41 подсоединены к выходам управления 21 ИСУ.

Per. dz состоит из триггеров Т, Т, ..., , к установочным входам которых подсоединены вентили 44 и 45. Один вход каждого из этих вентилей подсоединеи через линию задержки 46 к соответствующему вентильному входу 28j а к другому входу вентилей 44 и 45 подсоединены соответственно вентильные входы 29 и 30 Per. dz. Выходы триггеров 43 иодсоединены к нулевым 26 и единичным 27 выходам Per. dz.

ЦДА содерл ит два элемента «ИЛИ 47 и 48. Иервый вход элемента «ИЛИ 47 подсоединен к выходу dz 9 БИ, а второй вход - к выходу -dz 16 БК; выход элемента «ИЛИ

47нодсоедииен к вентильному входу 30 Per. dz. Цервый вход элемента «ИЛИ 48 подсоединен к выходу -dz 10 БИ, а второй вход-

5 к выходу -dz 17 БК; выход элемента «ИЛИ

48нодсоединен к вентильному входу 29 Per. dz.

Предлагаемый ЦДА работает следующим образом.

Блок интегрирования БИ последовательно обрабатывает информацию интеграторов двух типов: прямых ПИ и ннверсиых ИИ. Последние с некоторым приближением реализуют соотношения dx, у Г dy.

Рассмотрим в качестве иллюстрации, поясняющей иринции совместной работы интеграторов двух тииов, действие ПИ и ИИ в параллельном ЦДА, а затем в последовательном

0 ЦДА предлагаемого типа. Схемы соединения ИИ и ПИ имеют обычный вид, т. е. выходы dz одних интеграторов (ИИ или ПИ) подсоединяются ко входам dx и dy других. Инверсный интегратор показан на фиг. 2,а,

5 схемы соедииения ПР1 и ИР1 на фиг. 2, б, я, г, д.

Ииформация инверсных интеграторов в иараллельном ЦДА иерерабатывается следующим образом.

0 ИИ состоит из (/г+1)-разрядиого R-регистра, п-разрядного У-регистра (в п младших разрядах R-регистра хранится величина z, модуль которой , а в разрядах У-регистра- величина у, модуль которой ), и

сумматора, осуществляющего как сложение, так и вычитание. ИИ имеет входы dx, dy и выход dz. Приращение веса 2 на входе dy ИИ нрибавляется к содержимому У-регистра, ириращение того же веса на входе dx ИИ вызывает установку в «1 старшего разряда Rрегистра, т. е. осуществляется действие z .

.

Затем иоследовательно производится вычитаиие содержимого У-регистра из R-регпстра Также последовательно (с каждым вычитанием) выдается приращеиие веса выходе dz интегратора. Число приращений на выходе равно целой части величины . Остаток б - -- хранится в R-регистре. Л Вначале введем некоторые понятия. Назовем выполнение действий, вызываемых приращениями иа входах интеграторов, соответственно реализацией приращений на этих входах. Будем считать, что приращение иа выходе интегратора реализовано, если оно реализовано на всех входах других интеграторов, к которым иодсоединен выход данного интегратора. Рассматриваемые ЦДЛ состоят из цифровых интеграторов (ЦИ) двух типов. Интеграторы первого типа (ИИ) вырабатывают с каждым приращеиием на входе dx множество приращений на выходе dz, интеграторы второго типа (ПИ) - только одно приращение. Последовательность расиределеиия выходных приращений (одного или множества) имеет следующий вид. 1.Если выход dz одного ЦИ подсоединен и ко входу dx другого ЦИ, то реализация очередного приращения на выходе dz первого ЦИ и на входе dx второго ЦИ возможна только после реализации всех приращений на выходе dz второго ЦИ, вызванных иредыдущим приращением на выходе dz нервого ЦИ. Ясно, что если выход dz второго ЦИ, в свою очередь, подсоединен ко входу dx третьего ЦИ,то реализация очередного нриращения на входе dx иервого ЦИ возможна только после реализации всех нриращеиий на выходах dz нервого ЦИ, а также dz второго ЦИ и dz третьего ЦИ, вызванных предыдущим приращением на входе dx первого ЦИ. 2.Если выход dz ЦИ подсоединен одновременно ко входам dx и dy нескольких иитеграторов, то каждое приращение на выходе dz данного ЦИ вначале реализуется на входах dy соответствующих интеграторов и только затем на входах dx. Реализовать данную последовательность распределения приращений можно как на параллельных, так и на иоследовательиых ЦДЛ, однако в последнем случае получаемый эффект значительно существеннее. Рассмотрим работу носледовательного ЦДЛ, в котором реализуется введеиная последовательность распределения приращений. В Per. dz хранятся старшие разряды R-peгистров интеграторов. В ЗУ хранится остальная информация интеграторов, т. е. содержимое п младших разрядов R-регистра и п разрядов У-регистра. Эта информация выбирается из ЗУ в определенной последовательности с помощью БК, далее помещается и обрабатывается в БИ и затем пересылается в ЗУ и запоминается. приращения, поступающие на входы БИ. С выходов Б1 могут быть выданы следующие командные приращения: 1)dy, которое с выхода 13 БК поступает на вход dy 8 БИ и вызывает увеличение на соответствующую величину содержимого Yрегистра;2)dx, которое с выхода 14 БК поступает иа вход dx 7 БИ и вызывает прибавление содержимого /-регистра к R-регистру. Если в результате прибавления произощло переполнение R-регистра, то на выходе dz 3 БИ вырабатывает выходное приращение, которое ностуиает на вход 30 Per. dz. 3) -dx, которое с выхода 15 БК поступает на вход -dx 9 БИ и вызывает вычитаиие содержимого 7-регистра из R-регистра. Если в результате вычитания содержимое R-регистра сделалось меиьще «О, то иа выходе -dz 10 БИ вырабатывает приращение займа, которое поступает на вход 29 Per. dz; при этом к Rрегистру 31 БИ прибавляется единица старшего разряда; 4) - которое с выхода 16 БК поступает через элемеит «ИЛИ 47 на вход 30 Per. dz, вызывает установку в состояние «1 одного из триггеров Per. dz. 5)-dz, которое с выхода 17 БК поступает через элемеит «ИЛИ 48 на вход 29 Per. dz, вызывая установку в состояние «О одного из триггеров Per. dz. Последовательность, в которой ироизводится выбор информации интеграторов из ЗУ, а также обработка этой информации командными приращениями БК, оиределяются, во-первых, коммутацией в БК, осуществляемой с помощью коммутаториых щнуров 40, и, во-вторых, последовательностью поступления импульсов иа входы dz 18 БК. Эти импульсы поступают на БК с выходов 21 ИСУ, проходят по коммутаторным щнурам к гнездам считывания 38 БК и командным гнездам БК, вызывая выполнение команд, т. е. соответственно считывание нужной информации из ЗУ в БИ и подачу командных приращений с БК на БИ. Последовательность подачи импульсов на входы 18 БК определяется содержанием Per. dz и ИСУ. В Per. dz хранятся приращення, выработанные на выходах иитеграторов в процессе их обработки в БИ. Per. dz состоит из триггеров TI, ..., Г, в которых хранятся приращения, выработаиные на выходах интеграторов ЦИ1 ..., ЦИ„. При этом присвоение номеров интегратором и соответственно ирисвоение каждому интегратору триггера 43 Per. dz осуществляет в зависимости от схемы соедииения иитеграторов (схема ЦДЛ). Па вентильные входы 29 и 30 Per. dz поступают имиульсы с выходов БИ и БК, которые устанавливают один из триггеров соответстНа входы 28 Per. dz заводятся выходы считывания 12 БК. На входы 28, а также на вход 29 или 30 поступают нмпульсы, которые с помощью вентилей 44 и 45 обеспечивают установку в «О или «1 только одного из триггеров Per. dz. При этом изменяется состояние только того триггера Per. dz, в котором хранится приращение интегратора, чья информация в текущий момент обрабатывается в БИ. Содержимое триггеров Per. dz управляет с помощью ИСУ последовательностью распределения и реализацией приращений, появивщихся иа выходах интеграторов. Это та последовательность, которая была предложена выше. Например, если необходимо реализовать приращения на выходе i-ro интегратора ЦР1, то ИСУ обеспечивает подачу импульса на i-й вход 18 БК. Этот импульс вызывает выполнение соответствующей команды, набранной с помощью коммутаторных щнуров 40 в БК. Команды набираются в БК в зависимости от схемы соединения интеграторов.

Рассмотрим команды, которые могут быть выполнены с помощью БК;

а)команда dx-llHQ вызывает выбор из ЗУ в БИ информации интегратора ПИ, поступление приращения на вход dx БИ и соответственно прибавление содержимого Y-регистра к R-регистру БИ. Если в результате произощло переполнение R-регистра БИ, то триггер Гс Per. dz устанавливается в состояние «1. Затем из БИ переработанная информация передается в ЗУ и запоминается;

б)команда вызывает появление импульса на выходе dz БК и соответственно установку Tt, Per. dz в состояние «1.

в)команда соответственно вызывает выбор из ЗУ в БИ информации интегратора ЛИ1, соответственно ИИС,, поступление приращения на вход dy БИ и соответственно увеличение на единицу содержимого Y-регистра. Затем переработанная информация заноминается в ЗУ.

г)команда вызывает выбор из ЗУ в БИ ииформации интегратора ИИс, поступление приращения на вход -dx БИ и соответственно вычитание содержимого У-регистра из R-регистра БИ. Если в результате вычитания содержимое R-регистра сделалось меньще «О, то БИ посылает имиульс на выход -dz, устанавливает Tt, Per. dz в состояиие «О и занимает из Tt, Per. dz единицу старшего разряда; затем содержимое регистров БИ передается в ЗУ и запоминается;

д)команда О-Tt вызывает появление импульса на выходе -dz 17 БК и соответственно установку в «О -го разряда (т. е. Tt,) Per. dz.

Команды имеют приоритет по срочности исполнения, который обеспечивается линиями задержки 37 в БК. Наиболее срочной является команда в), затем а), б) и, наконец, г) и д). Каждый импульс на входе dz 18 БК вызывает выполнение команд, осуществляющих

реализацию очередного приращения на выходе dz интегратора ЦИ,,. Команды, которые требуют выполнения, следующим образом определяются схемой соедииепия интеграторов (схемой ЦДЛ).

1)Если в схеме ЦДЛ выход dz ПИц подсоединен ко входу dx ПИС, (соответственно dx ЯЯЕ), то импульс на TI-OM входе dz 18 БК должен вызвать выполнение команд

и (соответственно команд , н , ).

2)Еслн в схеме ЦДЛ выход dz ИИц подсоединен ко входу dx riMt, (соответственно //Я), то импульс на TJ-OM входе dz 18 БК

должен вызвать выполнение команд , и (соответственно команд и .

3)Если в схеме ЦДЛ выход dzMH (соответственно ПИг) нодсоединен ко входам dx

ЦИц, то импульс на т|-ом входе dz 18 БК

должен вызвать выполнение команд dz-

и (соответственно

( .1 и ,).

Выполнение каждой из этих команд обеспечивается соответствующей коммутацией в БК с помощью коммутаторных щнуров. Если импульс на TI-OM выходе dz 18 БК должен вызвать выполнение команды (соответственно ), то гнездо 35, подсоединенное через лииию задержки 37 к входу dz 18, необходимо подсоединить с помощью коммутаторных щнуров к 1г)-му гнезду считывания 5S и к командному гнезду 39, связанному с выходом дх 14- БК (соответственно с

выходом - дх 15 БК).

Если импульс на выходе dz 18 должен вызвать выполнение команды с( или йг/- ИИ, то гнездо 34, связанное с т1-ым входом dz IS, необходимо подсоединить с помощью коммутаторных щнуров к гнезду считывания 55 и к командному гнезду 39, связанному с выходом dy 13 БК. Если импульс на входе dz 18 БК должен вызвать выполнение команды (соответственно ,

то гнездо 36, связанное через линии задерлжи 37 с входом dz 18, необходимо подсоединить с помощью коммутаторных щнуров к т1-му гнезду считывания 38 и к командному гнезду 39, связанному с выходом dz 16 БК

(соответственно с выходом -dz 17 БК). В этом случае информация интеграторов, поступивщая в БИ, не обрабатывается, а изменяется только содержимое Г,, 43 Per. dz.

ИСУ обеспечивает правило 1 распределения приращений, рассмотренное выше. ТИ проходят через последовательно соединенные вентили переноса 42 только в том случае, если триггеры Т 43, к которым подсоединены эти вентили, находятся в состоянии «О. Если первый по счету триггер Т 43 Per. dz находится в состоянии «I, то ТИ не проходят через вентиль переноса, подсоединенный к этому триггеру, а поступают на вход вентиля управления 41, проходят через этот вентиль управления на соответствующий выход управления 21 ИСУ, вызывая реализацию приращения, находящегося в искомом триггере. Таким образом, имнульсы выдаются с такого выхода управления 2 ИСУ, который через вентиль управления 41 подсоединен к триггеру Т 43, находящемуся в состоянии «1 и имеющему наименьший номер (среди триггеров в состоянии «1). Правила, по которым присваиваются номера интеграторам, зависят от схемы соединения интеграторов и удовлетворяют следующему условию. Если в схеме ЦДЛ выход dz одного интегратора подсоединен ко входу dx другого, 15 то первому интегратору должен быть нрисвоен больший номер чем второму. Следовательно, приращения не поступают на выход dz первого интегратора до тех пор, пока не будут реализованы все приращения на выходе второго 20 интегратора (что обеспечивается с помощью ИСУ). Применение инверсных интеграторов в схемах ЦДЛ позволяет уменьшить число интеграторов в схемах. Рассмотрим некоторые примеры. На фиг. 2,6, в, г, д соответственно приведены: схема ЦДЛ для вычисления значений функций In л:, arcsinx, 21/- arcsecx Для вычисления зо аналогичных функций без применения инверсных интеграторов требуется соответственно 3 (для In л;), 4 (для агсз1п л:), 3 (для 21/л:),6(для arcsec к интеграторов. При этом часто приходится пользоваться следующими интегратора- 35 ми, что значительно увеличивает время вычисления и требует дополнительных проверок на возможность переполнения интеграторов при программировании. При использовании инверсных интеграторов (см. фиг. 2) для вычис- 40 ления значений этих функций требуется соответственно 2, 3, 1 и 4 интегратора. Применение инверсных интеграторов облегчает программирование на ЦДЛ обратных функций. Схемы ЦДА для вычисления обратных функций мо- 45 гут быть получены из схем, вычисляющих прямую функцию заменой местами входа независимой переменной и выхода, на котором вырабатывают приращения функции, а также заменой ряда ПИ (связывающих непосредст- 50 венно искомые вход и выход) и ИИ. Предмет изобретения 1. Цифровой дифференциальный анализа- 55 тор последовательного типа, содержащий запоминающее устройство с произвольной вы510 25 боркой, блок интегрирования, имеющий R-peгистр, У-регистр, устройство суммирования и вычитания, регистр приращений dz с рядом выходов и вентильных входов, блок команд, содержащий коммутирующую схему, включающую устройство выбора информации интеграторов, отличающийся тем, что, с целью уменьшения погрешности, увеличения быстродействия и гибкости, он содержит иерархическую вентильную схему з равления, состоящую из ряда вентилей управления и вентилей переноса, причем первый вход каждого вентиля управления подсоединен к единичному входу управления иерархической вентильной схемой управления, первый вход каждого вентиля переноса подключен к нулевым входам управления иерархической вентильной схемой управлепия; ко вторым входам каждого вентиля управления и переноса подсоединен выход вентиля переноса предыдущего более старшего разряда, а ко вторым входам вентилей управления и переноса старшего разряда регистра приращения dz подключен источник тактовых импульсов, выходы вентилей управления соединены с выходами управления иерархической вентильной схемы, R-регистр блока интегрирования содержит дополнительный выход займа старшего разряда, подсоединенный к выходу dz блока интегрирования, единичные и нулевые выходы соответствующего триггера регистра приращений связаны с единичными н нулевыми входами управления иерархической вентильной схемы, ее выходы управления подсоединены ко входам иг блока команд, выход dz блока интегрирования подключен к вентильным входам регистра приращений. 2. Устройство по п. 1, отличающееся тем, что блок команд содерл :ит набор групп входных коммутаторных гнезд по три гнезда в группе, набор выходных командных гнезд и гнезд считывания, линии задержки и коммутаторные шнуры с одним входным и двумя выходными концами; причем первое гнездо каждой группы входных коммутаторных гнезд подсоединено к одному входу dz блока команд, второе гнездо через линию задержки подключено к первому, а третье гнездо через линию задержки подсоединено ко второму, каждое командное гнездо dx, связано с одним из выходов блока команд, каждое гнездо считывания подсоединено к одному нз выходов считывания блока команд, входной конец коммутаторных шнуров подключен к соответствующим входным коммутаторным гнездам, один выходной конец коммутаторных шнуров подключен к соответствующему командному гнезду, а другой- к гнездам считывания.

Зг

(--«fra b c: iii

Даты

1970-01-01—Публикация