1

Изобретение относится к области вычислительной техники при иостроении специализированных вычислительных машин и иредназначено для вычисления функции у У х.

Известно зстройство для извлечения квадратных корней, содержащее три интегратора, иснользующее положительные и отрицательные пилообразные сигналы двух интеграторов поочередно в качестве входного сигнала третьего интегратора. Уровень выходного сигнала третьего интегратора контролируется с целью включения и выключеиия первых двух интеграторов 1.

В аналоговом вычислительном устройстве, формирующем функции степеней или корней от входного напряжения, входное напряжение убывает по экспоненпнальному закону во времени и нрикладывается к двум входам устройства сравнения. В этом устройстве ири

вычислеиии функцни у У х для значений аргумента х, приближающихся к нулю, ногрещность резко возрастает.

Наиболее близким ио технической сущности является устройство, содержащее два интегратора, два сумматора и сдвиговый регистр, причем первый вход первого сумматора соединен с выходом первого интегратора, выход первого сумматора подключен к первому входу второго ннтегратора, первый вход первого интегратора соединен с первым входом второго сумматора, второй вход второго сумматора подключен к нервому выходу сдвигового регистра, а выход второго сумматора соединен с входом сдвигового регистра 2.

При вычислении функции для значений х, приближающихся к нулю, погрещность вычислений резко возрастает, что ограничивает возможность ирименения указанного устройства. В нрактике рещения задач в области навигации, управления и др. приходится часто вычислять данную функцию при изменении независимой переменной в щироком диапазоне, включая значения, приближающиеся к

нулю.

Целью изобретення является повыщенне точности вычислений для значений х, приближающихся к нулю. Для этого в предлагаемое устройство введены третий интегратор и коммутатор, причем второй выход сдвигового регистра соединен со входом коммутатора, первый выход которого подключен к второму входу первого интегратора, а второй выход - к второму

входу второго иитегратора, выход второго интегратора соединен с первым входом третьего интегратора, второй вход которого подключен к первому входу второго интегратора, а выход соединен с вторым входом первого

сумматора.

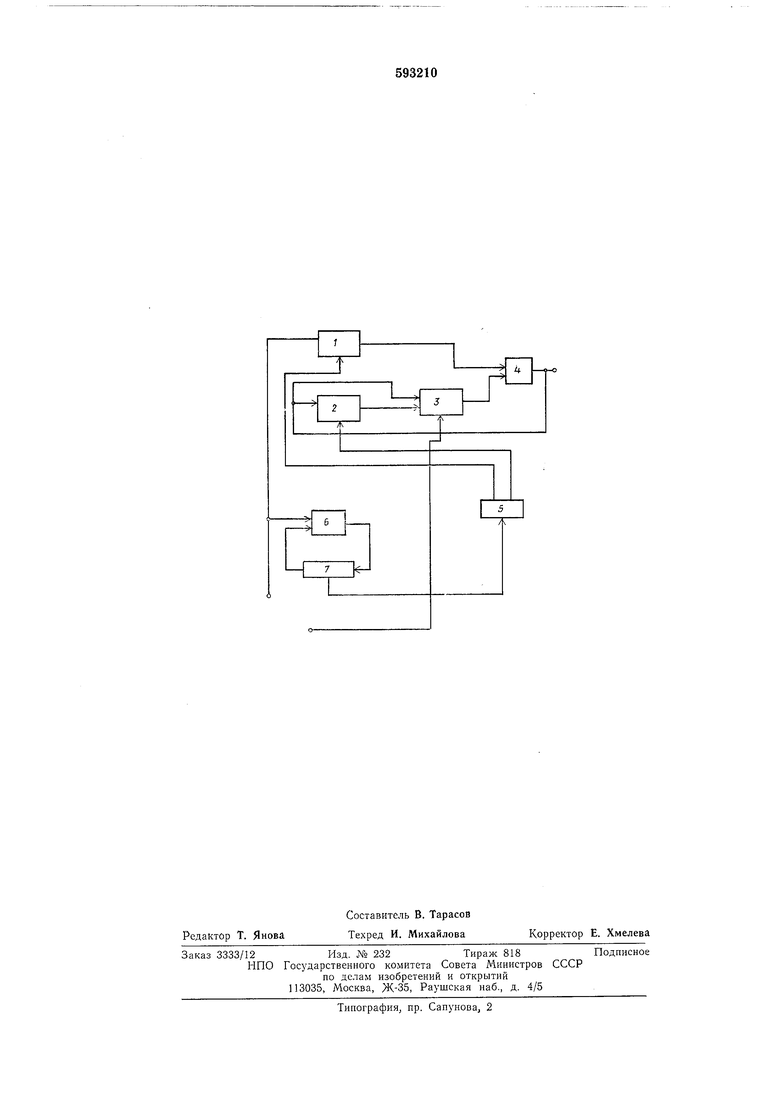

На чертел е дано предлагаемое устройство.

Устройство содержит первый,второй и третий интеграторы 1-3 соответственно, первый сумматор 4, коммутатор 5, второй сумматор 6 и сдвиговый регистр 7.

Работа предлагаемого устройства для вычислепия функции у заключается в следующем.

Перед пачалом вычислений на вход начальных значеиий подынтегральной функции интегратора 3 записывается значение ().

Вычисление функции у j/x начинается в устройстве с момента подачи через вход приращений dx независимый переменной. Приращения dx поступают на вход первого интегратора и на второй вход второго сумматора 6. Проходя через второй сумматор 6 и накапливаясь в сдвиговом регистре 7, приращения образуют значение подкоренного выражения х, которое поступает на вход коммутатора 5. В этом коммутаторе в зависимости от значения X производится формирование корректирующих множителей аи -

При изменении аргумента х от значений .)(-) до )+i корректирующий множитель а принимает значение а 2™-. С выхода первого интегратора на первый вход первого сумматора 4 поступает приращение

dx, умноженное на кеэффициент -. С выхода

второго интегратора 2 значение (-ady) сознаком минус подается на вход независимой переменной третьего интегратора 3, с выхода которого приращение dy(l-ay) поступает на второй вход первого сумматора 4. Приращение dy, образующееся на выходе первого сумматора, иодается на выход устройства. По мере изменения перемеиной х в коммутаторе 5 формируются соответствующие значения а

а

И - которые поступают на входы первого и второго интеграторов.

Таким образом, в предлагаемом устройстве введение новых элементов и связей значительно повыщает устойчивость вычислительной схемы, точность для значений х, приближающихся к пулю, и скорость вычислений. Кроме того, эффективность предлагаемого устройства заключается в том, что оно может быть использовано не только для вычисления функции у Vx.

Формула изобретения

Устройство для вычисления функции , содержащее два интегратора, два сумматора и сдвиговый регистр, причем первый вход первого сумматора соединен с выходом первого интегратора, выход первого сумматора

подключен к первому входу второго интегратора, первый вход первого интегратора соединен с первым входом второго сумматора, второй вход сумматора подключен к первому выходу сдвигового регистра, а выход второго

сумматора соединен со входом сдвигового регистра, отличающееся тем, что, с целью повыщения точности, в него введены третий интегратор и коммутатор, причем второй выход сдвигового регистра соединен со входом

коммутатора, первый выход которого подключен ко второму входу первого интегратора, а второй выход - ко второму входу второго интегратора, выход второго интегратора соединен с первым входом третьего интегратора,

второй вход которого подключен к первому входу второго интегратора, а выход соединен с вторым входом первого сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР №378846, кл. G 06F7/38, 18.01.71.

2. Г. П. Дригваль Цифровые дифференциальные анализаторы.. Сов. радио, М., 1970, с. 392.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обратной функции | 1980 |

|

SU942035A1 |

| Устройство для вычисления обратной функции | 1982 |

|

SU1137478A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Цифровой интегратор | 1980 |

|

SU879586A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| Устройство для цифрового дифференцирования | 1975 |

|

SU608145A1 |

| Устройство для вычисления логарифмической функции | 1988 |

|

SU1596323A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР ПОСЛЕДОВАТЕЛЬНОГО ТИПА | 1970 |

|

SU281025A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

Авторы

Даты

1978-02-15—Публикация

1976-04-27—Подача