Изобретение относится к области автоматики и вычислительной техники и предназначено для ассоциативных запоминающих устройств и схем приоритета.

Известны устройства для последовательного выделения «единиц в заданном порядке на п-разрядного двоичного кода, содержащие два последовательно соединенных регистра, блок выделения «единиц и блок исключения выделенных «единиц.

Предложенное устройство отличается тем, что в нем узел выделения «единиц выполнен, с дополнительными входами для запрета выделенных «единиц, присоединенными к узлу исключения выделенных «единиц, а информационные входы служат для нодачи исходного кода; между входом регистра и выходом узла выделения установлен преобразователь номера разряда выделенной «единицы в двоичный код, на выходе регистра установлен дешифратор двоичного кода, выходы которого соединены со входами узла исключения выделенных «единиц, вынолненного в виде шифратора запрета, вырабатывающего «нули в обработанных разрядах и «единицы в остальных разрядах.

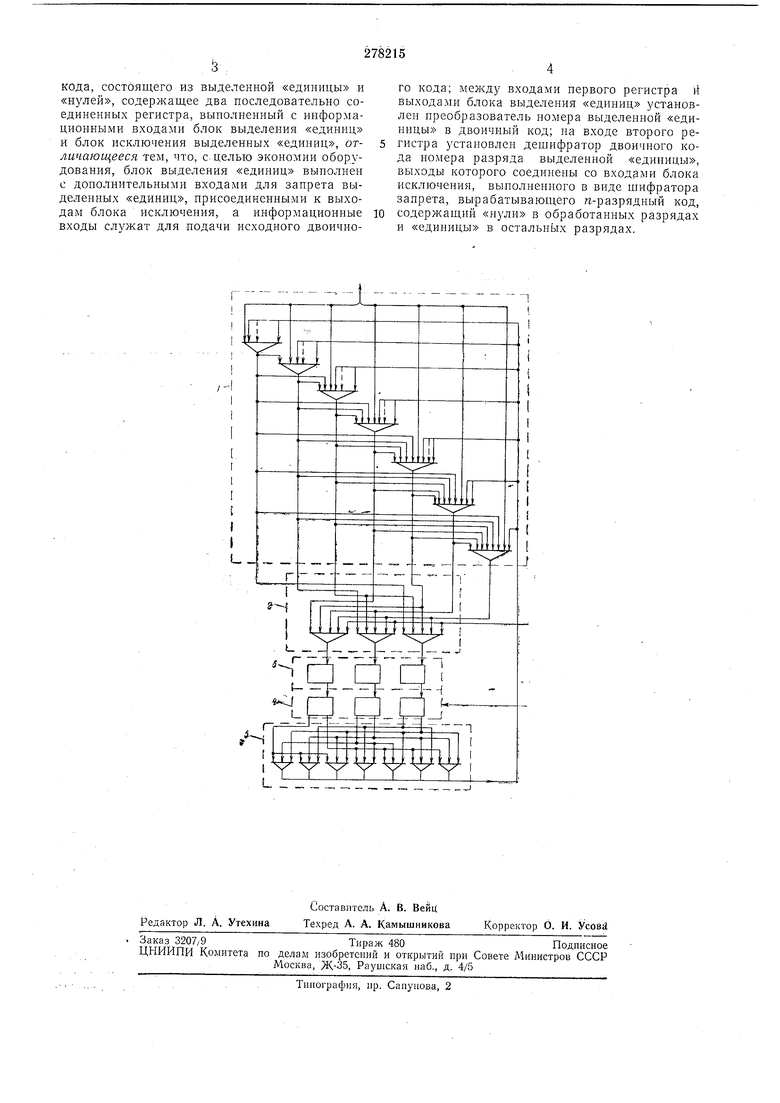

Устройство содержит блок выделения «единиц с шифратором запрета обработанных разрядов 1, блок кодирования номера разряда выделенной «единицы 2; регистры хранения

5 и 4 этого кода, дешифратор 5 двоичного кода номера разряда выделенной единицы. Устройство работает следующим образом. Перед началом работы производится пачальное гашение регистров 3 к 4, затем на

вход 6 поступает исходный двоичный код.

Работа устройства делится на такты, в каждом из которых происходит выделение очередной «единицы. В каждом такте блок / выделяет очередную, (в данном нримере левую)

«единицу исходного кода. Блок 2 кодирует выделенную «единицу двоичным кодом, который принимается в регистр 3, а затем в регистр 4. Прием в регистры 3 и 4 производится при подаче импульсов приема па шины 7 и S.

Блок 5 дешифрирует код, хранящийся в регистре 4. Шифратор запрета запрещает последующее, выделение закодированной «единицы и всех выделенных в предыдущих тактах (в данном нримере более левых) «единиц.

Предмет изобретения J3 , кода, состоящего из выделенной «единицы и «нулей, содержащее два последовательно соединенных регистра, выполненный е информациопными входами блок выделения «единиц и блок исключения выделенных «единиц, от-5 угишю ееся тем, что, с целью экономии оборудования, блок выделения «единиц выполнеи с дополнительными входами для запрета выделенных «единиц, присоединенными к выходам блока исключения, а информационныею входы служат для подачи исходного двоично4го кода; между входами первого регистра и выходами блока выделения «единиц установлен преобразователь номера выделенной «единицы в двоичный код; на входе второго регистра установлен дешифратор двоичного кода номера разряда выделенной «единицы, выходы которого соединены со входами блока исключения, выиолнеиного в виде шифр атора запрета, вырабатывающего п-разрядный код, содержащий «пули в обработанных разрядах и «единицы в остальньгх разрядах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

| Многоканальное устройство для организации доступа к ресурсам | 1986 |

|

SU1322284A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для выделения значащих разрядов из последовательности многоразрядных двоичных кодов | 1982 |

|

SU1038935A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

Даты

1970-01-01—Публикация