Устройство относится к автоматике и вычислительной те.хнике. Оно нредиазиачено для использования в различны.х устройствах ЭВМ, 3 схемах управления электронных и квазиэлектронных АТС, в автоматических и телемеханических системах.

Уже известны матрицы для выбора адреса, содержащие электронные ключи.

Цель изобретения - сокран;ение количества электронного оборудования.

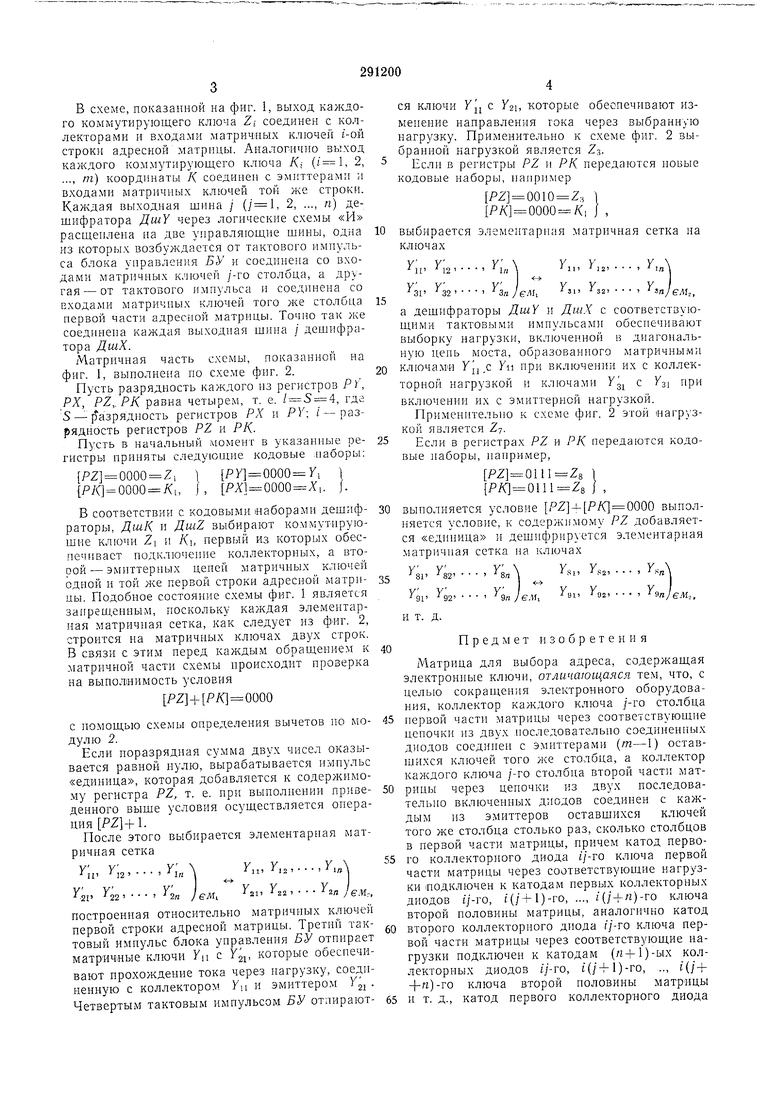

Предлагае.мая матрица отличается от известных тем, что коллектор каждого ключа /-го столбца нервой части матрицы через соответствующие цеиочки из двух последовательно сО единенных диодов соединен с эмиттерамн (т-1) оставшихся ключей того же столбца, а коллектор каждого ключа /-го столбца второй части матрицы через цепочки из двух последовательно включенных диодов соединен с каждым из эмиттеров осгавшихся ключей того же столбца столько раз, сколько столбцов в первой части матрицы.

Катод первого коллекторного диода ij-ro ключа иервой части матрицы через соответствующие нагрузки подключен к катодам нервых коллекторных диодов ij-ro, г(/+1)-го, ..., i(i + n)-ro ключа второй половины матрицы. Аналогично катод второго коллекторного диода f/-ro ключа первой части матрицы через соответствующие нагрузки подключен к катодам

(/;-}-1) -ых коллекторных диодов ij-ro, г (/+1) -го, ..., /{/ + «)-го ключа второй половины матрицы и т. д. Катод первого коллекторного диода /(/+1)-го ключа первой частп матрпцы через соответствующпе иагрузки подключен к катодам вторых коллекторных диодов ij-ro, i (j-г + 1)-го, ..., /(/ + /)-го ключа второй половины .матрицы. Аналогично катод второго коллекторного диода /(/--1)-го ключа первой части матрицы через соответствующпе нагрузк подключен к катодам () -ых коллекторных диодов ij-ro, г (/+1)-го, ..., i(j + /i)-ro ключа второй половины матрицы и т. д.

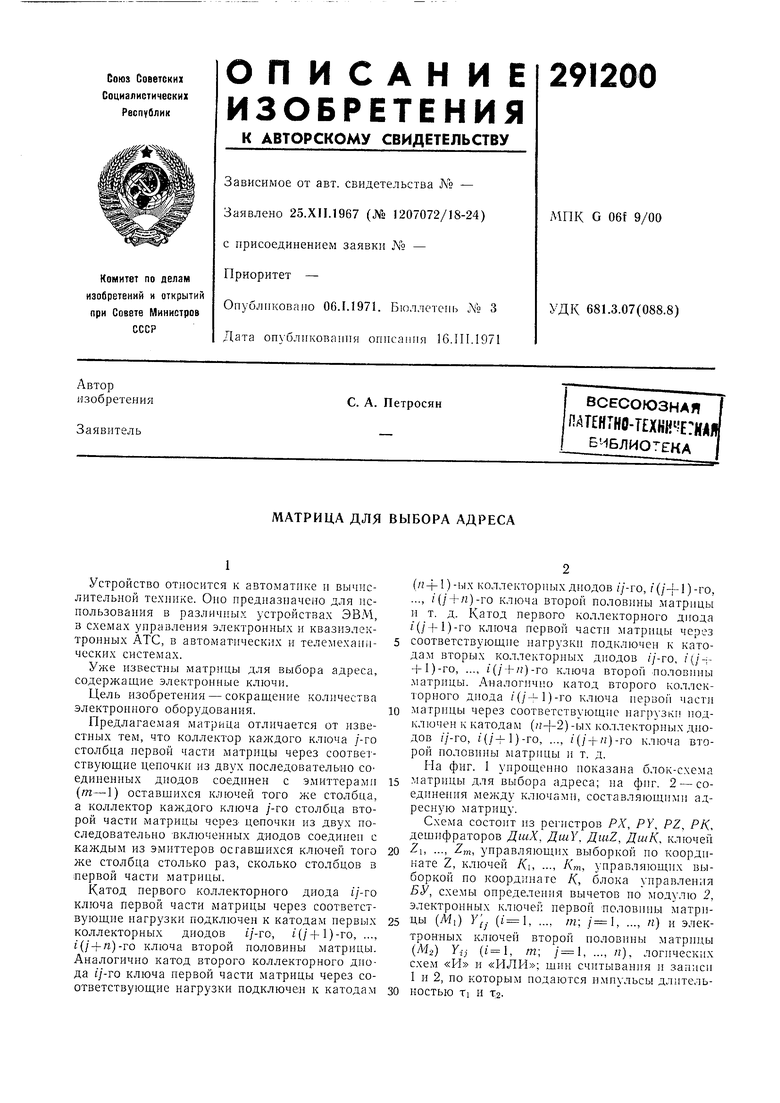

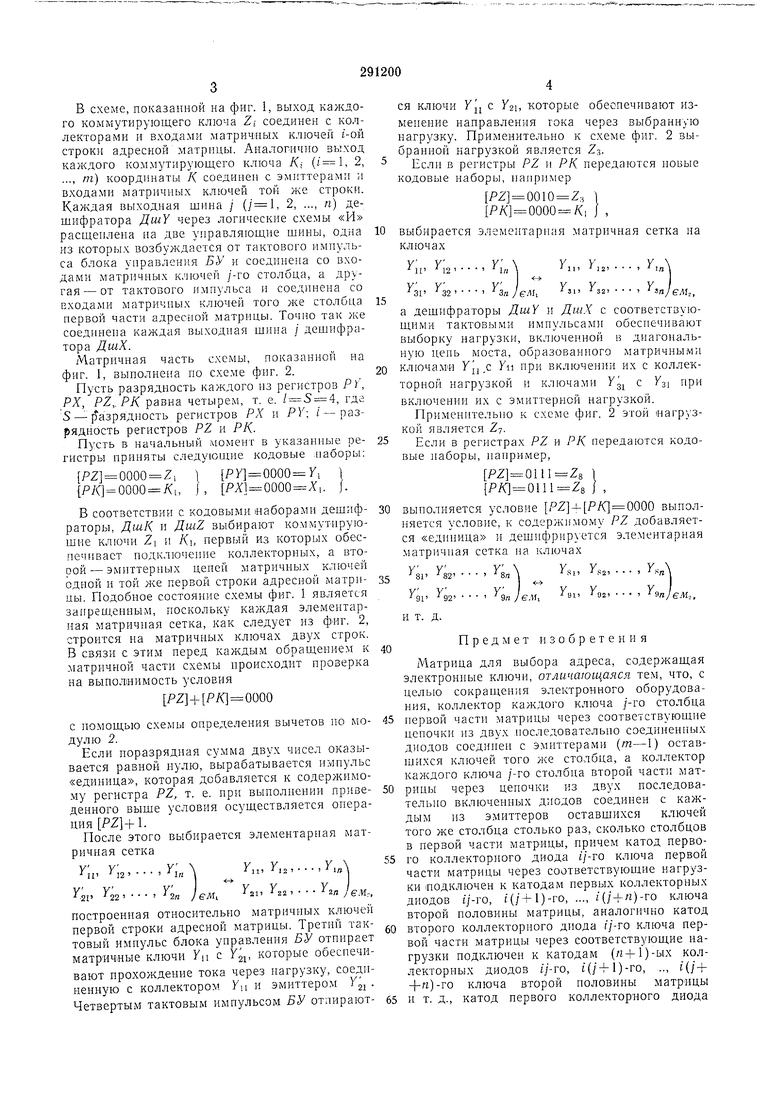

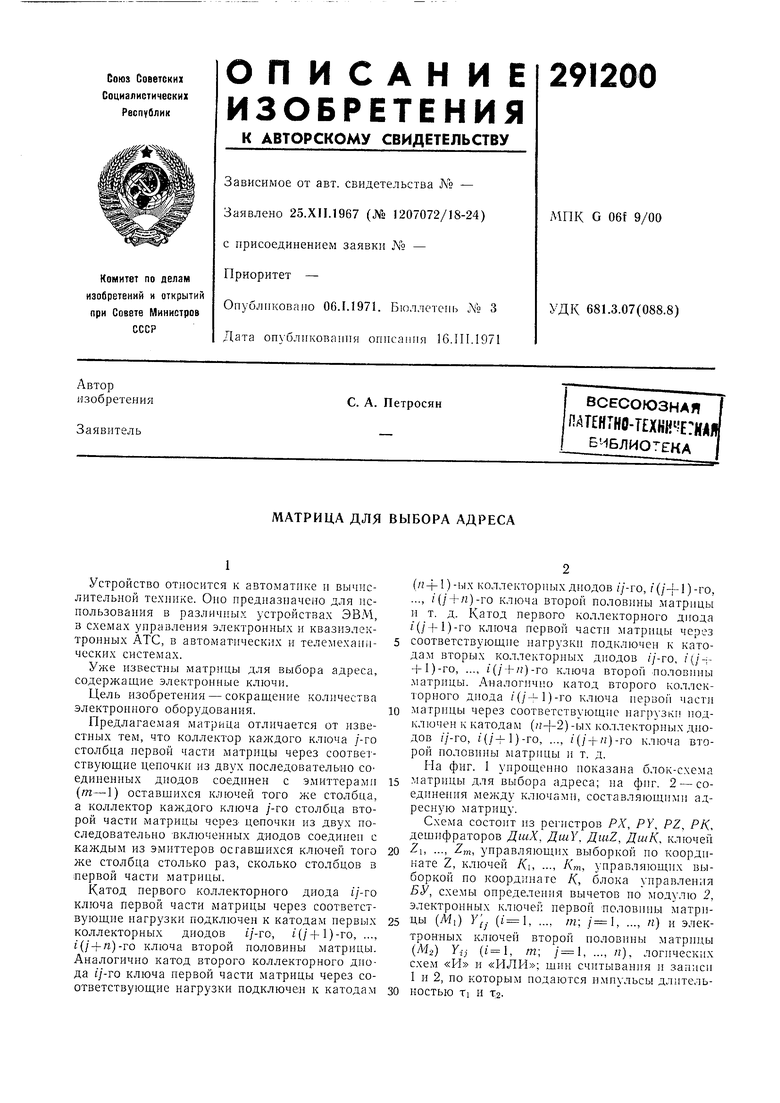

Па фиг. I упрощенно ноказана блок-схема матрицы для выбора адреса; на фиг. 2 - соединения менчду ключами, составляющими адресную матрицу.

Схема состоит из регистров РХ, PY, PZ, РК., дешифраторов ДшХ, ДшУ, Дш2, ДшК, ключе Zi, ..., Zm, управляющих выборкой по коордпнате Z, ключей /Ci, ..., Km, управляющих выборкой по координате /(, блока управления БУ, схемы определения вычетов по модулю 2, электронных ключей иервой половины матрицы (Ml У (i, .... т; , ..., п) и электронных ключей второй иоловины матрицы (М-2 Yij (, m; , ..., п), логических схем «И и шин считывания и записи 1 и 2, по которым подаются импульсы длительностью TI и Т2.

В схеме, показанной на фиг. 1, выход каждого коммутирующего ключа Z,; соединен с коллекторами и входами матричных ключей t-ой строки адресной матрицы. Аналогично выход каждого коммутирующего ключа /(,- (, 2, ..., т) координаты К соединен с эмнттерами и входами матричных ключей той же строки. Каждая выходная шииа / (, 2, ..., п) дешифратора ДшУ через логические схемы «И расщеплена на две управляющие щины, одна из которых возбуждается от тактового имнульса блока унравления БУ и соединена со входами матричных ключей /-го столбца, а другая- от тактового имиульса и соединеиа со входами матричных ключей того же столбца первой части адресной матрицы. Точно так же соедпнеиа выходная шина / дешифратора ДшХ.

Матричная часть схемы, показанной на фиг. 1, выполнена но схеме фиг. 2.

Пусть разрядность каждого из регистров РУ, РХ, PZ,.PK равна четырем, т. е. .5 4, где S - разрядиость регистров РХ и PY; i-разрядность регистров PZ и Р/(.

Пусть в начальный момент в указанные регистры приняты следующие кодовые .наборы;

PZ 0000 Z, PY Р/( J , .

В соответствии с кодовыми наборами дешифраторы, Дш/( и ДulZ выбирают коммутируюшие ключи Zi и , первый из которых обеспечивает нодключе1п- е коллекторных, а второй- эмпттерных цепей матричных ключей одной и той лее первой строки адресной матрицы. Подобное состояние схемы фиг. 1 является запреш.енным, поскольку каждая элементарная матричная сетка, как следует из фиг. 2, строится на матричных ключах двух строк. В связи с этим перед каждым обращением к матричной части схемы происходит проверка на выполнимость условия

0000

с номощью схемы определения вычетов но модулю 2.

Если поразрядная сумма двух чисел оказывается равной нулю, вырабатывается имиульс «единица, которая добавляется к содержимому регистра PZ, т. е. при выполнеиип призеденного выше условия осуществляется операция .

После этого выбирается элементарная матричная сетка У VУ Y YY

Гц, J 12. In -f in -f 12 1/

-

V VVу уу /

21 22 2« /ем,21 J 22 2л Уем,,

построенная относительно матричных ключей первой строки адресной матрицы. Третий тактовый имиульс блока управленпя БУ отпирает матричные ключи Уц с Y, которые обеспечивают прохождение тока через нагрузку, соединенную с коллектором Уц и эмиттером Y . Четвертым тактовым импульсом БУ отпираются ключи У;( с Угь которые обеспечивают изменение направления гока через выбранную нагрузку. Применительно к схеме фиг. 2 выбранной нагрузкой является Zs.

Еслн в регистры PZ п Р/С передаются новые кодовые наборы, например

PZ 0010 Z, РЛ; (,

выбирается элементарная матричная сетка на ключах

У УV

111 121 ) I

мр М2 In

1/)

У УУ I У УV I

/3J, J 32 , з2--- зп/елг,,,

а дешифраторы ДшУ и ДшХ с соответствующими тактовыми импульсами обеснечнвают выборку нагрузки, включенной в диагональную цепь моста, образованного матричными ключами yji.c Уи при включении их с коллекторной нагрузкой и ключами Уд с УЗ) при включении их с эмиттерной нагрузкой.

Применительно к схеме фиг. 2 этой нагрузкой является Zy.

Если в регистрах PZ и РК, передаются кодовые наборы, например,

PZ

P/(

выполняется условие 0000 выполняется условие, к содержимому PZ добавляется «единица и дешифрируется элементарная матричная сетка на ключах

У УУ У УY

81 82 8ч 1Su .f 82 -I .«л

-

у уу I у уу

Зп/еМг,

J qi Q9 Qn / с- .SI 02 l

91 - 92 9л /e.Vf,

н т. д.

Предмет и з о б р е т е н и я

Матрица для выбора адреса, содержащая электронные ключи, отличающаяся тем, что, с целью сокращения электронного оборудования, коллектор каждого ключа /-го столбца первой части матрицы через соответствующие цепочки из двух последовательно соединенпых диодов соединен с эмиттерами (т-1) оставшихся ключей того же столбца, а коллектор каждого ключа /-го етолбца второй части матрицы через цепочки из двух последовательно включепных диодов соединен с каждым из эмиттеров оставшихся ключей того же столбца столько раз, сколько столбцов в первой части матрицы, причем катод первого коллекторного диода г7-го ключа первой части матрицы через соответствуюидие нагрузки подключен к катодам первых коллекторных диодов 17-го, i(/+l)-ro, ..., ;(/-fn)-ro ключа второй половины матрицы, аналогично катод второго коллекторного диода ij-ro ключа первой части матрицы через соответствующие нагрузки подключен к катодам (п+1)-ых коллекторных диодов j7-ro, i(i-rl}-rQ, .., i(i + -|-и)-го ключа второй половины матрицы и т. д., катод первого коллекторного диода iO + l)-ro ключа первой части матрицы через соответствующие нагрузки подключен к катодам вторых коллекторных диодов ij-ro, г(/+ + 1)-го, ..., i(/ + n)-ro ключа второй половины матрицы, аналогично катод второго коллектор-5 ного диода i(/+l)-ro ключа первой части матрицы через соответствующие нагр)зки подключей к катодам (л-:-2)-ых коллекторных диодов ij-ro, i(i+l)-TO, ..., i(/+n)-ro ключа второй половины матрицы и т. д.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

| Устройство для отображения графической информации на газоразрядном матричном индикаторе | 1987 |

|

SU1495846A1 |

| МНОГОПОЗИЦИОННОЕ ПРОГРАММНОЕ УСТРОЙСТВО | 1971 |

|

SU320003A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

| Устройство для решения транспортных задач | 1985 |

|

SU1379787A1 |

| ТРЕНАЖЕР ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ МАТРИЦ | 1990 |

|

RU2102792C1 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2013 |

|

RU2540780C2 |

.2

Даты

1971-01-01—Публикация