Предлагаемое изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных устройствах, в частности в запоминающи.х, арифметических и других устройствах, где о,существляется ирием, хранение и выдача кодированных чисел.

Известны схемы контроля правильности записи числа в регистре, содержащие регистр и логические элементы «И и «ИЛИ.

Целью изобретения является упрощение схемы контроля правильности записи числа в регистре и увеличение надежности ее функционирования.

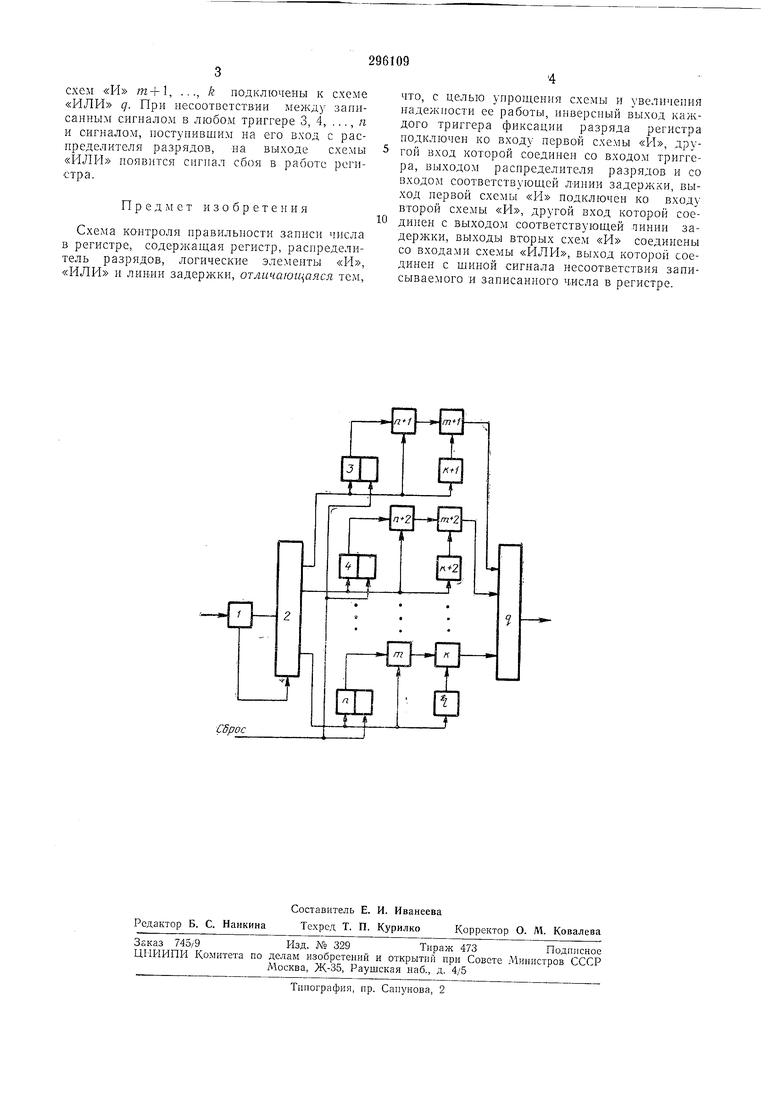

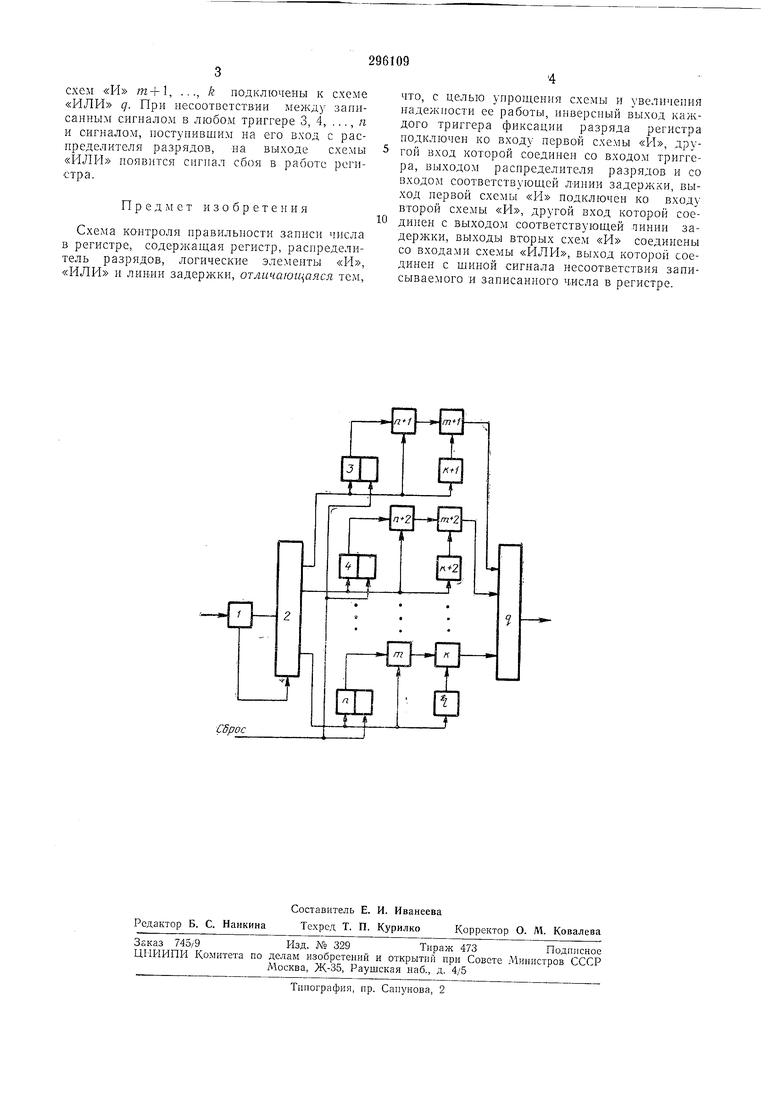

Предлагаемое устройство отличается те.м, что посредством логических схем «И, «ИЛИ и времязадерживающих цепочек производится сравнение каждого разряда числа, поступающего па вход регистра, с соответствующим разрядом числа, записанного на фиксирующих элементах регистра, например триггерах, и при наличии песоответствия между ними схема вырабатывает сигнал неисправности регистра или сбоя при записи в него числа. Это позволяет достигнуть поставленную цель.

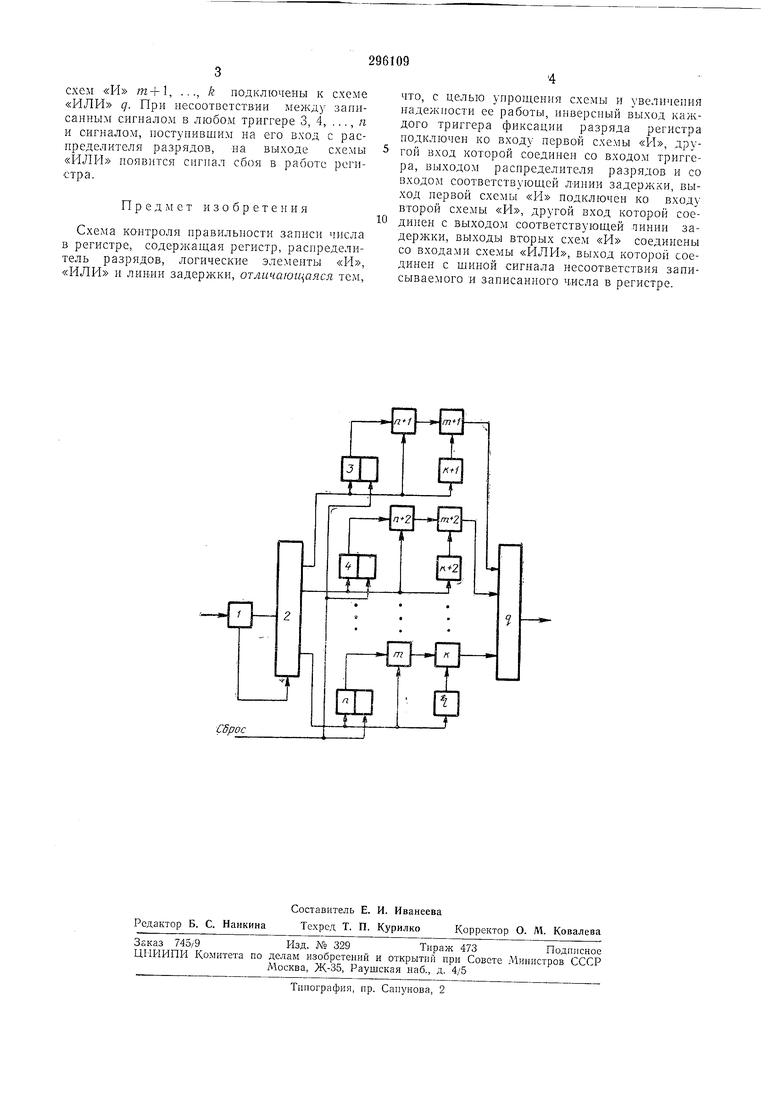

Блок-схема предлагаемого устройства показана на чертеже.

вующ.ие фиксаторы разрядов, в качестве которых использованы, например, триггеры 3, 4, ..., п. Другие входы этих триггеров используются для приведения регистра в нулевое состояние путем подачи сигнала «Сброс. Инверсные выходы триггеров подключены ко входам соответствующих с.хем п+1, , ..., т, а другие входы этих же схем «И подключены параллельно входам соответствующих триггеров, которые, в свою очередь, подключены к распределителю разрядов. Сигпалы па выходах схем «И n-fl, л-(-2, ..., т появляются только в случае несоответствия записанного в данном триггере разряда и сигнала, поданного на вход этого же триггера с распределителя разрядов. С выходов схем n + l, «-f2, ..., т сигналы поступают на соответствующие входы других схем «И т+1, т+2, ..., k, на вторые входы которых поступают сигналы через времязадерживающие цепочки /e-f-l, k + 2, ..., I с выходов распределителя разрядов, т. е. входы времязадерживающих цепочек подключены параллельно входам соответствующих им триггеров. Времязадерживающие цепочки обеспечивают подачу сигналов на схемы «И т+1, ni + 2, ..., k со сдвигом во времени, для предотвращения ложных срабатываний схемы в момент переключения триггеров (фиксаторов разрядов) 3, 4, ..., п при вводе числа в регистр. Выходы

схем «И in+l, ..., k подключены к схеме «ИЛИ д. Ири несоответствии между записанным сигналом в любом триггере 3,4, ..., п и сигналом, постунившим на его вход с распределителя разрядов, на выходе схемы «ИЛР1 появится сигнал сбоя в работе регистра.

Предмет изобретения

Схема контроля правильности записи числа в регистре, содержащая регистр, распределитель разрядов, логические элементы «И, «ИЛИ и линии задержки, отличающаяся тем.

что, с целью упрощения схемы и увеличения надежности ее работы, инверсный выход каждого триггера фикеадии разряда региетра подключен ко входу первой схемы «И, другой вход которой соединен со входом триггера, выходом распределителя разрядов и со входом соответствующей линии задержки, выход первой схемы «И подключен ко входу второй ехемы «И, другой вход которой соединен с выходом соответствующей линии задержки, выходы вторых схем «И соединены со входами схемы «ИЛИ, выход которой соединен с щиной сигнала нееоответствия записываемого и записанного числа в регистре.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

fffpoc

Даты

1971-01-01—Публикация