Изобретение относнтся к технике передачи информации с помощью бинарных сигналов, a именно к технике обеспечения синхронизма источников и приемников информации в системах передачи дискретных сообщений и в системах с импульсно-кодовой модуляцией речевых и других аналоговых сигналов.

Известны способы синхронизации на передаче в начале подциклов , частных кодовых групп синхросигнала и на одновременном сравнении принимаемого сигнала со всеми возможными комбинациями символов этих частных кодовых групп.

Недостатком известных способов является то, что, обеспечивая существенное уменьщение времени вхождения в синхронизм при на.личин в каждой частной кодовой группе трех и более символов, этот способ перестает быть эффективным при уменьщении числа символов в каждой частной кодовой группе синхросигнала до двзх и особенно до одного символа. В тоже время объединении в общий групповой сигнал нескольких каналов наиболее удобно выделять для передачи синхросигнала как раз по однол{у символу от кодовой труппы -каждого канала.

сигналами маркерной группы до тех пор пока на одних и тех же позициях не будет обпаружепо нелднократное повторение одпого из указанных циклических сдвигов, после чего устанавливают фазу си-гнала приемных распределителей.

Предлагаемый способ отличается также тем, что в процессе вхождения в синхронизм сравнение принимаемого импульсно-кодового сигнала с сигналами, представляющими собой циклические по подциклам сдвиги маркерной группы синхросигнала, осуществл.яют в каждом цикле на нескольких соседних группах ПОЗИЦИЙ, г корректирование приемных распределителей производят на число временных ннтервалов, соответствующее тому числу соседних групп позиций, начиная с первой группы, на которых не обнаружено никакого циклического сдвига маркерной группы синхросигналов.

Это позволяет y eньщить время вхождения в синхронизм и .сократить число позиций, отводимых в подциклах для передачи сипхросигнала.

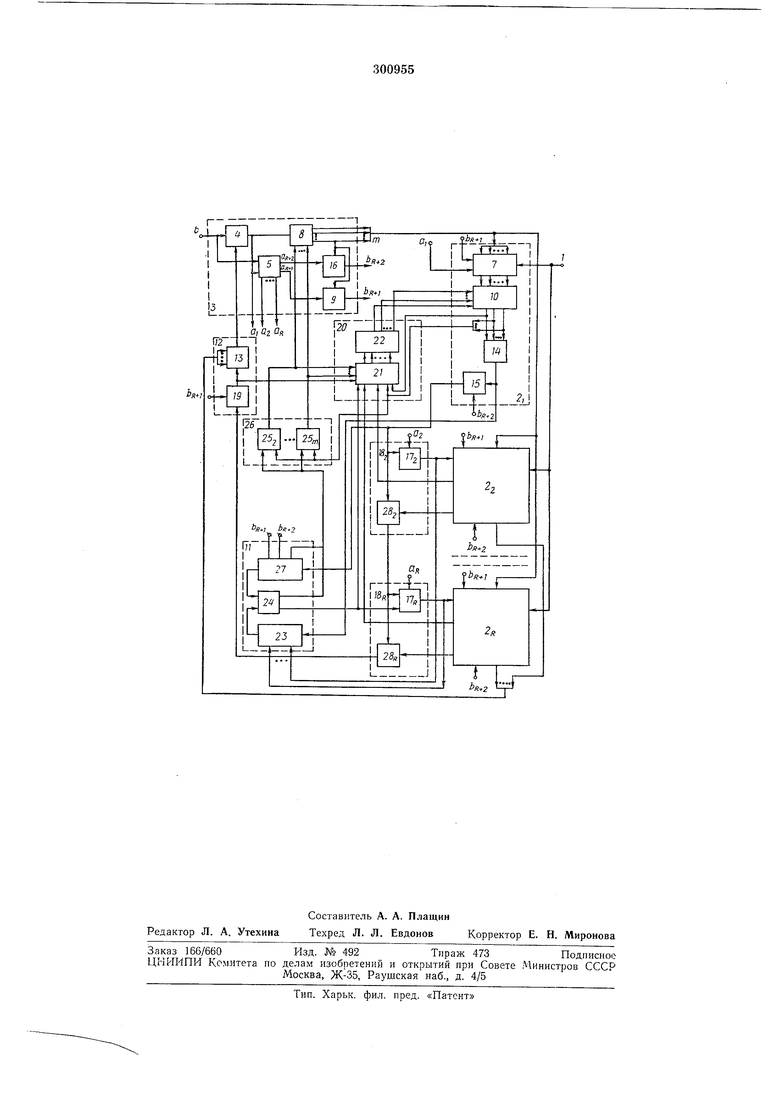

Предлагаемый способ поясняется блок-схемой, показанной на чертеже, где 1 - вход принимаемого сигнала; опознаватедо частоты следования оодциклов (делитель

п

на, где п - число игаформациоиных позиции в каждом цикле, а m равно числу маркер,ных символов, передаваемых в одном цикле) ; 5 - регистр сдвига, в котором число сдвигающих ячеек равно числу иараллельно опробуемых позиций иодцикла плюс 1 (регистр сдвига на / + 1, где

1 - о / + И- 04 /1 -ч.); 6 - :вх.од тактовых импульсов; 7 - схема запоминания символов на т опробуемых позиций циклов; 8 - делитель-распределитель на число подциклов, равное числу символов в кодовой комбияации (делитель-Ра-определитель на т); 9 - схема 10 - схема обнар ужения циклических сдвигов маркерной грустны; // - индикатор состояния синхронизма; 12 - схема управления делителем на-; 13 vi 14 - схемы

15 - распределитель импульсов до момента времени, определяемого сигналом, поступающим к нему на вход 17л - схемы ISz-- S - схемы управления опозвавателями синхрогрупп со 2-го по R-TA; 19 - схема 20 - схема управления первым опознавателе.м синхрогрупп; 21 - узел коммутации сигналов с выходов схем обнаружения цикличеоких сигналов маркерных групп; 22 - узел динамической намяти и управления схемами обнаружения циклических сдвигов маркерной группы первого опознавателя синхрогрупп; 23 - индикатор вхождения ,в синхрОЕИзм; 24 - двдичиая ячейка памяти (триггер) 252-25 ,п- схемы 26 - схема управления делителем-раоиределителем на т; 27 - индикатор выхода из синхронизма.Oi-я +2- последовательности импульсов, задержанные соответственно на О, 1,2,..., R + 1 тактовых интервала относительно начала подцикл,ов опробования.

Яч-Ь R+2 тоследовательности импульсов, задержанные соответствеино на R я R+1 тактовых интервалов относительно начала цикла опробования.

В соответствии с предложенным способом принимаемый сигнал / с линии подают параллельно па R опозпавателей синхрогрупп 2,

т+ п

число которых

-2. В каждом опот

знавателе 2 с помощью последовательностей импульсов местного генератора 3 осуществляют опробование т позиций принимаемого сигнала, распределенных во времени апалогично маркерным позициям цикла. Для выполнения этих фуикщий на каждый опознаватель 2 подают соответствующие последовательности импульсов, которые формируют с помощью делителя 4 и регистра сдвига 5 генератора 3. На

вход 6 генератора 3 подают тактовые импульсы.

Опробавание импульсных позиций с помощью опознавателей 2i-2н производят таКИМ образом, что каждььм следующим опознавателем опробуют позиции, соседние позициям, которые опр01буют предшествующим опознавателем. Значение симв.олов на опробуемых позициях запоминают с помощью схем запоминания 7, причем последовательную запись в ячейки запоминания производят с помощью сигналов с делителя-распределителя 8, генератора 3. Обновление данных в схемах запоминания 7 производят один раз за время цикла, определяемого п + п импульсными позициями.

Перед каждой но1вой записью сигналов в схемы запоминания 7, имевшаяся ранее запись стирается в момент формирования импульсов bfi „. 1 в схеме «И 9.

В каждом из .апознавателей 2 с помощью схем 10 обнаружения циклических сдвигов маркерной группы выявляют наличие или отсутствие соответствия символов входного сигнала на опробуемых позициях маркерной группе или какому-либо ее цикличеоко.му сдвигу. При обнаружении такого соответствия в режиме вхождеЕШя в синхронизм, определяемом инди1катором состояния синхронизма 11,

осуществляют корректирование фазы делителя 4 на число позиций, равное числу опознавателей, начиная с первого, в которых на опробуемых позициях обнаружены символы, не соответствующие маркерной группе или ее

циклическим сдвигам. Корректирование проводят с помощью схемы управления 12, в которой сигнал нужной фазе подают на сброс делителя через схему «ИЛИ 13.

При обнаружении в како м-либо из опознавателей 2 си-ехр.осигнала, представляющего собой маркерную rpyniny или ее циклический сдвиг, формируют сигнал, который через схему «ИЛИ 14 подают на расщиритель 15. Имцульсом с выхода распределителя блокируют

работу последующих опознавателей 2i+i- 2R. окончания блокирования определяют по импульсной последовательно Ьл + а со схемы «И 16 генератора 3. Сигналом с выхода распределителя 15 выключают опробования последующих опознавателей 2; 1-н2л с помощью схел «И 17, схемы управления 18, на которую 1подают сигналы опробо:еания с выхода регистра сдвига 5.

Если ни в каком из опознавателей 2 не

обнаружено синхрогрупп, то на делитель 4 через схему «И 19 подают сигнал установки фазы, определяющей сдвиг на R периодов тактовой частоты (&л ; i).

В случае, если каким-либо опознавателе.м

2; опробуют комбинации СИЛ1ВОЛОВ, совпадающие с маркерной группой или одним из ее циклических сдвигов, то следующее опробование позиций, на которых обнаружена указанная комбинация, после произведенного корректироваиия фазы делителя 4, осуществляют первым о:позна вателем 2i, которым при этом блокируют схемы обнаружения всех других циклических сдвигов .мар|керной группы с помощью схемы управления первым оиознавателем. Обеспечивается такой режим работы за счет того, что сигиалы с выходов узла 10 обнаружения циклических сдвигов маркерной группы с 1помощью узла коммутации 21 распределяют по двоичным ячейкам узла динамической памяти 22 так, что сигналами с выходов этих ячеек блокируют все схемы обнаружения синхрогруппы, кр.оме схемы, в которой выделяют кодовую комбинацию, идентичную принятой в предыдущем цикле с помощью

Оиробова-ние позиций, на которых обнаружена синхрхзгрупиа, производят до тех пор, пока на них не поступят символы, не соответствующие принимаемой синхрогруппе. При этом разблокируют все схемы обнаружения маркерной группы и ее циклических сдвигов и продолжают процесс пяиска синхросигнала указанным выще образом. В случае неоднократного повторения на опробуемых позициях символов синхросигнала после фиксации этого состояния индикатором вхождения в синхронизм 23 и соответственно триггером 24 производят установку фазы делителя-распределителя 8. Причем величина скачка при установке фазы определяется тем, какой из циклических сдвигов маркерной груотпы опробовался перед фиксацией состояния синхронизма. Производят эту операцию с помощью выделения делителем-распределителем 26. Контроль

за правильностью фиксации положения синхронизма производят с помощью индикатора выхода из синхронизма 27.

Пред -м ет изобретения

1.Способ синхронизации по циклам систем передачи дискретной информации и систем с импульсно-кодовой модуляцией, отличающийся тем, что, с целью уменьщения времени вхождения в синхронизм и сокращения числа позиций, отводимых в подциклах для передачи синхросигнала, принимаемый импульсно-кодовый сигнал в режиме вхождения в синхронизм сравнивают со всеми циклически сдвинутыми по подци1клам сигналами маркерной группы синхросигнала до тех пор, пока на одних и тех же позициях не будет обнаружено неоднократное повторение одного из указанных циклических сдвигав, после чего устанавливают фазу сигнала приемных распределителей.

2.Способ по п. 1, отличающийся тем, что в процессе вхождения в синхронизм сравнение

принимаемого импульсно-кодового сигнала с сигналами, представляющими собой циклические по подциклам сдвиги маркерной группы синхросигнала, осуществляют в цикле на нескольких соседних группах позиций, а корректирование приемных распределителей производят на число временных интервалов, соответствующее тому числу соседних групп позиций, начиная с первой группы, на которых не обнаружено циклических сдвигов

маркерной группы синхросигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ | 1971 |

|

SU305578A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство синхронизации по циклам | 1974 |

|

SU565402A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМЫ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1970 |

|

SU279701A1 |

Даты

1971-01-01—Публикация