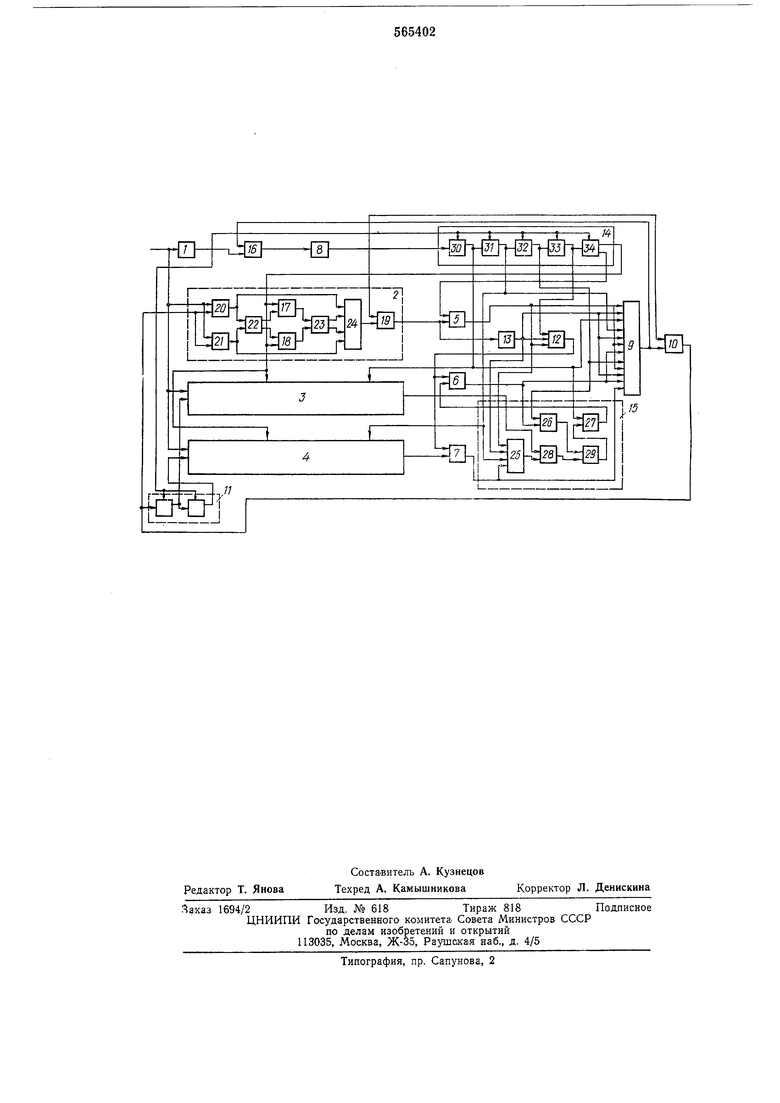

выход формирователя I тактовых импульсов непосредственно и через последовательно соединенные элемент запрета 16 и делитель-распределитель 8 подключен к соответствующим входам регистра 14 сдвига, одна группа выходов которого подключена к соответствующим входам блоков 3 и 4 опробывания импульсных позиций, узла 15 перезаписи сигналов несоответствия и элемента И-ИЛИ 9, а другая группа выходов - к входу расщирителя 5 непосредственно, а к входам расщирителей 6 и 7 через элемент И 12, причем выходы расширителей 5-7 непосредственно подключены к соответствующим входам элемента И-ИЛИ 9, выход которого подключен к второму входу элемента запрета 16, а выход узла 15 подключен к дополнительному входу расщирителя 6. Блок 2 опробывания импульсных позиций, как и блоки 3 и 4 опробывания, состоит из элементов И 17-20 и элемента запрета 21, триггеров 22 и 23 и элемента И-ИЛИ 24. Узел 15 состоит из элементов И 25, 26 и 27, элемента ИЛИ 28 и триггера 29. Регистр 14 состоит из ячеек 30-34. Устройство работает следующим образом. В состоянии синхронизма импульсы тактовой частоты с выхода формирователя 1 через элемент запрета 16 поступают на вход делителя-распределителя 8, осуществляющего деление частоты следования тактовых импульсов до частоты следования циклов. Регистр 14 задерживает импульсы с выхода делителя-распределителя 8 на один, два, три, четыре и пять периодов тактовой частоты. С входа устройства на блоки 2-4 поступает групповой сигнал. На вход блока 2 в режиме синхронизации при отсутствии сбоев символов синхросигнала цикла с выхода делителя-распределителя 8 через элемент ИЛИ 10 поступает последовательность импульсов с частотой следования циклов. На входы блоков 3 и 4 с элемента 11 поступают такие же последовательности импульсов, но задержанные на один и два периода тактовой частоты соответственно. Таким образом, если блок 2 опробывает какую-либо позицию группового сигнала, то блоки 3 и 4 опробывают следующие за ней импульсные позиции. В случае опробывания блоком 2 на импульсной позиции символа «1 на выходе элемента И 20 появляется импульс, а при опробывании символа «О импульс появляется на выходе элемента запрета 21, при этом триггер 22 з станавливается в соответствующее состояние. Через некоторое время импульс с выхода ячейки 34 регистра сдвига после совпадения на элементе И 17 или И 18 устанавливает триггер 28 в такое же состояние. Триггер 23 запоминает на длительность цикла символ на опробованной позиции. В следующем цикле на элементе И-ИЛИ 24 происходит сравнение опробуемого символа и символа, «запомненного триггером 24. Принцип работы блоков 3 и 4 аналогичей. Таким образом, каждый из блоков 2-4 опробывает две разделенные временем цикла позиции: «запомненную при предыдущем опробывании и опробуемую в данном цикле. При опробывании чередующихся символов «10 или «01 на разделенных временем цикла позициях импульсы с выхода элементов И 17 и 18, соответствующие первому опробуемому символу, устанавливают триггер 23 в такое состояние, при котором импульс, соответствующий второму опробуемому символу, не проходит на выход элемента И-ИЛИ 24. В установивщемся режиме (в режиме синхронизма) блок 2 опробывает чередующиеся символы «1010 ... «синхросигнала цикла, при этом блоки 3 и 4 опробывают символы, чередующиеся по случайному закону. Результаты опробывания блоками 3 и 4 в режиме синхронизма на работу всего зстройства не влияют. Если при оиробывании двух разделенных временем цикла позициях обнаруживаются одинаковые символы, т. е. «00 или «11, то на выходе элемента И-ИЛИ 24 появляется импульс положительной полярности - сигнал несоответствия опробуемых символов символам синхросигнала цикла (сигнал ошибки). После поступления с выхода элемента И- ИЛИ 24 через элемент 19 нескольких импульсов (количество зависит от емкости накопителя 13) заполняется накопитель 13, в результате чего на его выходе появляется сигнал разрешения поиска, а устройство переходит из состояния синхронизма в режим поиска синхронизма. Накопитель 13 придает инерционность устройству, то есть сохраняет состояние синхронизма при случайных сбоях символов синхросигнала цикла (в режиме синхронизма), а также сохраняет состояние поиска синхронизма при случайном соответствии опробуемых символов символам синхросигнала (в режиме поиска синхронизма). После перехода устройства в режим поиска на входы блоков 2-4 с входов элемента ИЛИ 10 и элемента задержки 11 в этом цикле поступает опробующий сигнал для опробывания и запоминания символов на соседних позициях, причем на выходе элемента И-ИЛИ 23 могут появиться ложные импульсы сигнала ошибки. Для исключения прохождения этих импульсов на выходы блоков 2-4 на элементе И 19 производится стробирование, для чего в блоке 2 используются импульсы положительной полярности с выхода делителя-распределителя 8, а в блоках 3 и 4 - импульсы с выходов ячеек 30 и 31 регистра сдвига соответственно. Триггер 23 блоков 2-4 запоминает в режиме поиска символ на последней позиции, опробуемой соответствующим блоком опробования в данном цикле, то есть по окончании процесса опробывания. В режиме поиска, кроме опробывания и заоминания блоками опробывания 2-4 символов на соседних позициях осуи1ествляется также «торможение делителя-распределителя 8, при этом через элемент зэпрета 16 запрещается прохождение одного, двух или трех импульсов тактовой частоты, в результате чего в следующем цикле на выходе делителяраспределителя 8 появляется импульс иа один, два или три периода тактовой частоты позже. Следовательно, блоки опробывания в следующем цикле опробируют позиции, отстоящие от ранее опробуемых на один, два или три периода тактовой частоты, в зависимости от того, на сколько позиций происходит «торможение делителя-распределителя 8.

Расп1ирители 5-7 осуществляют заттомицание сигналов ошибок на время, необходимое для «торможения делителя-распределителя 8 и осунхествления перезаписи. Расширители 6 и 7 могут запоминать сигналы ошибки на более длительное время, так как установка их в исходное состояние производится импульсом с выхода ячейки 33 регистра сдвига лишь при наличии на входах элемента И 12 разрешающих сигналов с выходов расширителя 5 и накопителя 13. Следовательно, расширители б и 7 могут заполтинать сигнал ошибки предыдущих опробываний, поэтому «торМожение делителя-распределителя 8 может осуществляться в да.льнейц ем и на большее число позиций, что сокращает время вхождения в синхронизм.

Формирование импульса «торможения происходит следующим образом.

После заТюлнения накоцителя 13 на его выходе появляется сигнал, разрешающий совместно с сигналом ошибки, расширенным расширителем 5, прохождение через элемент И-ИЛИ 9 импульса с выхода ячейки 30 регистра сдвига. Если в это время на выходе расширителя 6 присутствует сигнал ошибки, то на выход элемента И-ИЛИ 9 проходит импульс с выхода ячейки 31 регистра сдвига, а при наличии сигналов ошибки на выходах всех расширителей 5-7 на выход элемента И-ИЛИ 9 проходят импульсы с выходов ячеек 30, 31 и 32 регистра сдвига. Импульсы, появляющиеся на выходе элемента И-ИЛИ 9, поступают на элемент запрета 16 и осуществляют «торможение делителя-расцределителя 8 на соответствующее число позиций.

Импульсы с выхода элемента И-ИЛИ 9 поступают на элемент ИЛИ 10, на другой вход которого поступают импульсы с выхода делителя-распределителя 8. Элемент ИЛИ 10 и элемент задержки 11 осуществляют формирование сигнала опробывания.

В режиме поиска возможны следующие режимы работы блоков опробывания 2-4.

В первом режиме блок 2 опробывания опробывает символы, характер чередования которых не соответствует синхросигналу цикла, а блоки 3 и 4 символы, соответствующие Символам синхросигнала цикла. Сигналы ощибки на выходах блоков 3 и 4 отсутствуют, следовательно, отсутствуют разрешающие сигналы на выходах расширителей 6 и 7. «Торможение делителя-распределителя 8 производится на одну импульсную позицию, а элемент ИЛИ 10 и элемент задержки 11 обесцечивают поступление сигналов для опробывания и запоминания символов на трех следующих позициях, задержанных относительно первоначально опробуемых на одну. По окончании этих процессов импульсом с выхода

ячейки 34 регистра сдвига производится установка расширителя 5 в исходное состояние.

Во втором режиме блоки 2 и 4 опробывают символы, которые не соответствуют синхросигналу, а блок 3 оцробывают символы, соответствующие символам синхросигнала цикла. Импульсы сигнала ошибки на выходах блока 3 опробывания и расширителя 6 отсутствуют, в то время как импульсы с выходов блоков 2 и 4 опробывания устанавливают расширители 5 и 7 в единичное состояние.

Так как разрешающий сигнал на выходе расширителя 6 отсутствует, то импульсы с выходов ячеек 31 и 32 регистра сдвига на выход элемента И-ИЛИ 9 не проходят, поэтому «торможение делителя-распределителя 8 цроизво.дится, как и в первом случае, лишь на одну позицию, при этом на входы блоков 2- 4 с выходов элемента ИЛИ 10 и элемента задержки 11 поступают импульсы для опробывания и запоминания символов на цозициях, сдвинутых во времени на одну.

Кроме этих процессов в этом случае осуществляется также перезапись сигнала ошибки

(сигнала несоответствия) из расширителя 6 в расширитель 7. Импульс с выхода ячейки 31 регистра сдвига через элемент 25 и ИЛИ 28 поступает на установку триггера 29, запоминающего сигнал ошибки. Так как сброс

триггера 29 производится только при наличии на входе элемента 26 разрешающего сигнала с выхода расширителя 6, то триггер 29 «запоминает сигнал ошибки до следующего цикла. В следующем цикле блок 3 оцробывает

символы на позиции, на которой блок 4 уже обнаружил символы, не соответствующие символам синхросигнала цикла, при этом независимо от того, какие символы оцробывает блок 3 опробывания импульс с выхода ячейки 30

регистра сдвига через элемент И 27 устанавливает расширитель 6 в состояние, соответствующее сигналу ошибки. Если блок 2 снова опробывает символы, не соответствующие символам синхросигнала цикла, то «торможение делителя-распределителя 8 производится на две или три позиции, в зависимости от «аличия разрешающего сигнала на выходе расширителя 7. Следовательно, перезапись сигнала несоответствия опробуемых символов

символам синхросигнала цикла, сигнала ощибки, также приводит к сокращению времени вхождения в синхронизм.

После цоявления сигнала ошибки на выходе расщирителя 6 становится возможным сброс

триггера 9 в исходное состояние. Сброс тригrepa 29 осуществляется импульсом с выхода ячейки 31 регистра сдвига.

В третьем режиме блоки 2 и 3 опробывают символы, которые не соответствуют символам Синхросигнала цикла, а блок 4 опробывания-символы, соответствующие символам синхросигнала цикла. Импульс сигнала ощибки, появляющийся на выходе блока 3 опробывания, проходит через элемент ИЛИ 28 и устанавливает триггер 29 в состояние, при котором разрешается прохождение импульса с выхода ячейки 30 регистра сдвита через элемент ИЛИ 27, на установку расширителя 6 в единичное состояние. После этого расширитель 6 оазрешает прохождение через элемент И-ИЛИ 9 импульса с выхода ячейки 31 регистра сдвига.

Таким образом, на выход элемента И- ИЛИ 9 и элемента ИЛИ 0 проходят импульсы с выходов ячеек 30 и 31 регистра сдвига, в результате «торможение делителя-распределителя 8 пооизводится на две позиции, а блоки 2-4 опробывают и запоминают символы на позициях, задержанных от первоначально Опообуемых на два периода тактовой частоты.

После этого импульсами с выходов ячейки 32 (через элемент И 26). ячейки 33 (через элемент И 12) и ячейки 34 регистра сдвига осуществляется сброс триггера 29 и расширителей 6 и 5 в исходное состояние.

В четвертом режиме все блоки 2-4 опробывают символы, которые не соответствуют символам синхросигнала цикла. В этом случае ВСе рашсирители 5-7 устанавливаются в единичное состояние. Импульс с выхода ячейки 31 регистра сдвига, появляющийся на выходе элемента И 25 и проходящий через элемент ИЛИ 28, на работу триггера 29 влияния не оказывает, так как триггер 29 уже находится в единичном состоянии после прохождения через элемент ИЛИ 28 импульса сигнала ошибки с выхода блока 3 опробываиия. В этом Случа е «торможение делителя-распределителя 8 производится на три позиции, а сброс триггера 29, расширителей 6 и 7 и расширителя 5 осуществляется в этом же цикле

импульсами с выходов соответственно ячеек 32-34 регистра сдвига.

Таким образом, процесс поиска продолжается до тех пор, пока не будет достигнут синхронизм по циклам.

Формула изобретения

Устройство синхронизации по циклам, содержащее на входе формирователь тактовых

импульсов и п блоков опробывания импульсных позиций с расширителями, а также делитель-распределитель и последовательно соединенные элементы И-ИЛИ, ИЛИ и элемент задержки, вход и выходы которого подключены к соответствующим входам блоков опробывания импульсных позиций, причем выход и вход первого расширителя подключены к соответствующим входам элемента И непосредственно и через накопитель, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, введены регистр сдвига, узел перезаписи сигналов несоответствия и элемент Запрета, при этом выход формирователя тактовых импульсов непосредственно и через последовательно соединенные элемент Запрет и делитель-распределитель подключен к соответствующим входам регистра сдвига, одна группа выходов которого подключена к соответствующим входам блоков опробывания импульсных позиций,,кроме первого, узла перезаписи сигналов несоответствия и элемента И-ИЛИ, а другая группа выходов - к входу первого расширителя непосредственно, а к входам (п-I) расширителей - через элемент И, причем выходы расширителей непосредствен-но подключены к соответствующим входам элемента И-ИЛИ, выход которого подключен к второму входу элемента запрета, а выход узла перезаписи

сигналов несоответствия подключен к дополнительному входу одного из расширителей.

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР № 279701, кл. Н 04L 7/00, 1964,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1980 |

|

SU944134A2 |

| Устройство синхронизации по циклам | 1982 |

|

SU1075434A2 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМЫ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1970 |

|

SU279701A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU725257A2 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU300955A1 |

| Устройство синхронизации по циклам | 1976 |

|

SU618858A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ | 1971 |

|

SU305578A1 |

| Приемник синхросигнала | 1986 |

|

SU1424129A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

Авторы

Даты

1977-07-15—Публикация

1974-12-26—Подача