Предлагаемое устройство относится к технике передачи информации с помощью бинарных сигналов, а именно: к технике обеспечения синхронизма источников и приемников информации в системах передачи дискретных сообщений и в системах с импульсно-кодовой модуляцией речевых и других аналоговых сигналов. Оно может быть использовано на радиотехнических предприятиях, разрабатывающих и изготавливающих импульсные системы связи. Особенно целесообразно применение его в системах с временным уплотнением и разделением нескольких каналов нередачи информации.

Известны устройства для синхронизации по циклам систем передачи дискретной информации, содержащие делитель-распределитель подциклов, распределитель символов в подциклах, управляемый делитель тактовой частоты, схем корректирования фазы делителей и индикатор состояния сихронизма.

Предлагаемое устр ойство отличается тем, что оно содержит схему управления первым опознавателем циклических сдвигов по подциклам маркерной группы и группу опознавателей циклических сдвигов по подциклам маркерной группы, входы которых объединены и подключены ко входному зажиму. Выход расширителя каждого онознавателя подсоединен ко входу схемы запоминания

последующего опознавателя, причем выход расширителя первого опознавателя подключен к индикатору состояния синхронизма, выход которого соединен со схемами корректирования фазы делителей и со схемой управления первым опознавателем. Выходы делителяраспределителя подциклов подключены к схеме запоминания каждого опознавателя, а входы-к выходам схемы корректирования фазы

делителя-распределителя подциклов. Кал :дый из выходов распределителя символов в подциклах соединен соответственно со входом схемы запоминания каждого опознавателя, а выходы схемы управления первым опознавателем нодключены ко входам схемы корректирования фазы делителя-распределителя и ко входам узла обнарулсения циклических сдвигов маркерной группы первого опозпавателя, выходы которого подсоединены ко входам узла коммутации схемы управления первым онознавателем и ко входам узла обнаружения циклических сдвигов маркерной группы кал;дого опознавателя.

Онознаватель циклических сдвигов по подциклам маркерной группы содержит схему запоминания, узел обнаружения циклических сдвигов маркерной группы и расширитель, входы которого соединены с выходами узла

ляющин вход ооъединеы с одним из запрещающих входов схемы заиоминания.

Это позволяет ускорить вхождение в синхронизм и сократить чиСоТО позиций, отводимых в подциклах на передачу синхросигнала.

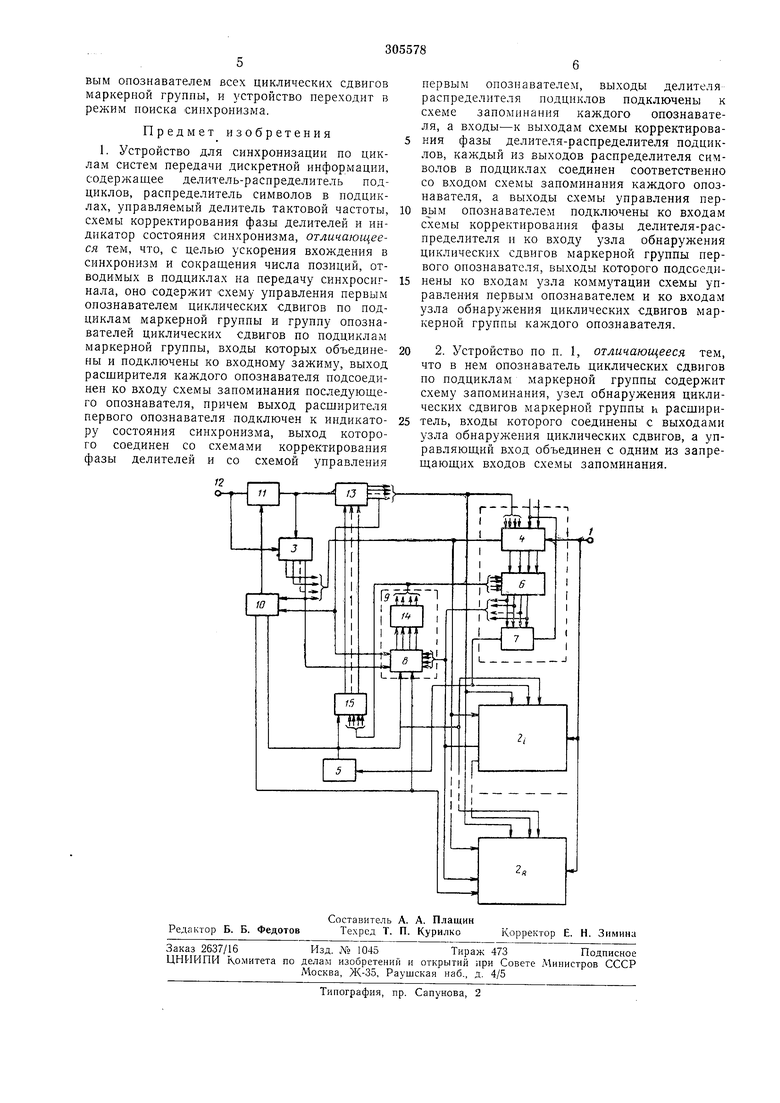

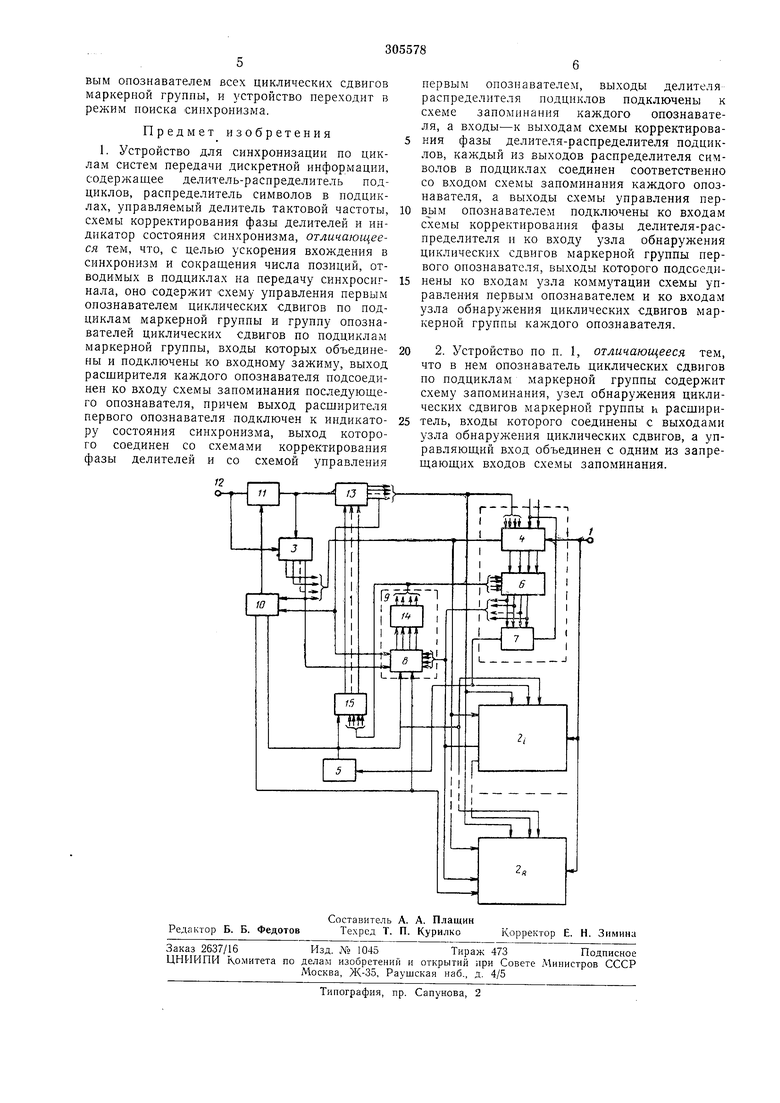

Блок-схема предлагаемого устройства представ п:ена па чертеже.

Принимаемый сигнал со входа I подается на опознаватели 2 синхрогрупп, которые опробуют позиции (по Числу символов в маркермой группе) нрпнима.-емого сигнала, распределенные во времени аналогично маркерным позициям цикла. Момент выбора опробуемых позиций принимаемого сигнала для ка/кдого из R опознавателей определяется последовательностями импульсов и, (i 1,2,...,./) с распределителями 3, следующих с частотой следования подциклов, и последовательностями dj (,2,...,m), представляющими собой последовательности разрещающих подставок, с частотой следования, равной частоте следования ПОДЦИКЛОБ.

В онозпавателе синхрогрупп символы, выделенные последовательностями а, и dj из принимаемого сигнала записываются в схему запоминания 4 при наличии на ее запрещающем входе разрещающих сигналов с индикатора состояния синхронизма 5 и с предыдущего опознавателя.

Символы, выделенные из принимаемого сигнала опознавателем 2, анализируются в узле 6 обнаружения циклических сдвигов маркерного сигнала на схемах совпадения, число которых равно числу циклических сдвигов маркерного сигнала. Сигнал об обнаружении маркерной группы или ее циклического сдвига с соответствующей схемы совпадения узла о поступает на расщиритель 7 и на узел коммутации 8 схемы 9 управления первым опознавателем синхрогрупп. С выхода расщирителя gi, расщиренный до величины, необходимой для перекрытия опробуемой в течение цикла части подцикла, он поступает на запрещающие входы схем запоминания 4 и расщирителей 7 последующих опознавателей .2,+ - 2л и запрещает их работу в течение данного цикла опробования.

Одновременно сигнал с выхода g, опознавателя 2{, пройдя через опознаватели 2i+i--2д, с выхода gR поступает на схему 10 корректирования фазы управляемого делителя // тактовой частоты до частоты повторения подциклов, обеспечивая корректирование фазы делителя на i-1 позицию тактовой частоты, и на схему 9 управления первым опознавателен синхрогрупп, запрещая опробование первым онознавателем (2i) всех циклических сдвигов маркерной группы, кроме выделенного опознавателем 2{.

Фаза делителя 11 корректируется запретом импульсов тактовой частоты со входа 12 на делитель по сигналу dm с делителя-распределителя 13, а разрещение на работу делителя приходит по фазе сигнала gi с выхода опознавателя 2i, в котором обнаружен циклический сдвиг маркерной группы и который появляется на выходе g опознавателя 2н. Если в опробуемом ци:-:ле пи OAJUI из схем опознавателей 2j - 2ц не обнаружила маркерную группу или ее циклический сдвиг, работа делителя разрещается по сигналу UK, поступающему па схему корректнровання 10 с распределителя символов в подциклах 3.

Таким образом, при следующем цикле опробование юзиций припимаемого сигнала, на которых в предыдущем цикле онознавателем 2i был обнаружен циклический сдвиг маркерной группы, производится олознавагелем . При этом узел динамической памяти 14 схемы управления 9 по сигналу с опознавателя 2г, поступающему на узел 14 через узел коммутации 8, разрешает узлу 6 обнаружения циклических сдвигов маркерной группы опознавателя 2 выделение только той циклической комбинации, которая была обнаружена в принимаемом сигпале опознавателем .2,-. Если обнаруженный ранее опознавателем

21циклический сдвиг маркерной группы выделяется при следующем цикле опробования узлом 6 опознавателя 2i, то сигнал с выхода g: расширителя 7 запрещает работу опозпавателей 2 - 2д на хданный цикл опробования. Если же циклический сдвиг маркерной группы, обнаруженный в предыдущем цикле опознавателем 2, в следующем цикле им не обнаружен, разрешается работа опознавателей 22 - 2к, а узел динамической памяти 14 разблокирует узел Б обнаружения циклических сдвигов опознавателя 2i для всех циклических

комбинаций маркерного сигнала.

Сигнал с выхода gi опознавателя 2i поступает на индикатор состояния синхронизма 5, который решает, является ли обнаруженная синхрогруииа маркерной.

Если индикатор состояния синхронизма принимает положительное решение, переводит систему в установленный режим, то сигнал с его выхода запрещает работу опознавателей

22- схемы корректирования 10 фазы управляемого делителя тактовой частоты // и,

кроме того, в соответствии со сведениями о циклическом сдвиге маркерпого сигнала, постунающими с выходов Г - г™ узла динамической памяти 14 на схе.му 15 корректироваПИЯ фазы делителя-распределителя подциклов 13, устанавливает фазу последнего.

Сигнал с выхода индикатора состояния синхронизма 5 через устройство коммутации S устанавливает узел динамической намяти в

состояние, разрешающее выделение узлом 6 обнаружения циклических сдвигов опознавателя 2i только маркерной комбинации.

Состояние синхронизма контролируется опознавателем 2 и индикатором 5 по наличию сигнала с выхода g опознавателя 2.

Если процепт нропадания и.мпульсов с выхода g превыщает допустимый, на выходе индикатора 5 появляется сигнал, который разрешает работу опознавателей 2 - 2н и схемь

вым опознавателем всех циклических сдвигов маркерной группы, и устройство переходит в режим поиска синхронизма.

Предмет изобретения

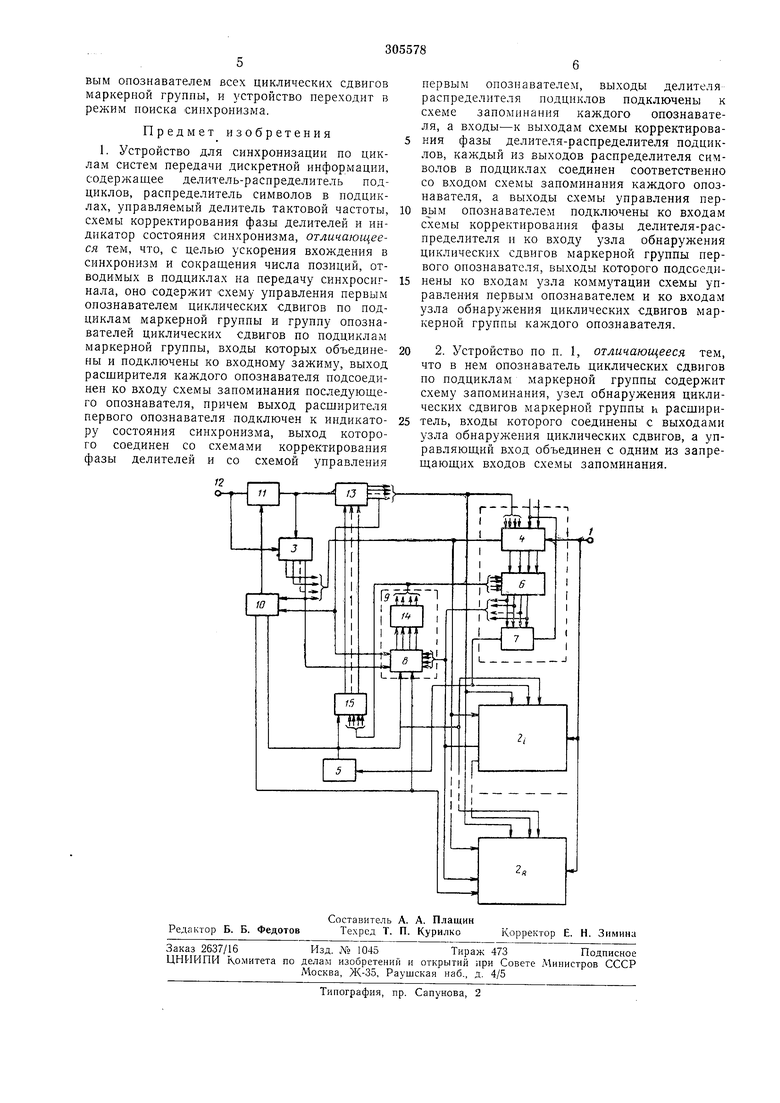

1. Устройство для синхронизации по циклам систем передачи дискретной информации, содержащее делитель-распределитель подциклов, распределитель символов в подциклах, управляемый делитель тактовой частоты, схемы корректирования фазы делителей и индикатор состояния синхронизма, отличающееся тем, что, с целью ускорения вхождения в синхронизм и сокращения числа позиций, отводимых в подциклах на передачу синхросигнала, оно содержит схему управления первым опознавателем циклических сдвигов по подциклам маркерной группы и группу опознавателей циклических сдвигов по подциклам маркерной группы, входы которых объединены и подключены ко входному зажиму, выход расщирителя каждого опознавателя подсоединен ко входу схемы запоминания последующего опознавателя, причем выход расширителя первого опознавателя подключен к индикатору состояния синхронизма, выход которого соединен со схемами корректирования фазы делителей и со схемой управления

Г2

первым опознавателем, выходы делителя распределителя подциклов подключены к схеме запоминания каждого опознавателя, а входы-к выходам схемы корректирования фазы делителя-распределителя подциклов, каждый из выходов распределителя символов в подциклах соединен соответственно со входом схемы запоминания каждого опознавателя, а выходы схемы управления первь1м опознавателем подключены ко входам схемы корректирования фазы делителя-распределителя и ко входу узла обнаружения циклических сдвигов маркерной группы первого опознавателя, выходы которого подсоединены ко входам узла коммутации схемы управления первым опознавателем и ко входам узла обнаружения циклических сдвигов маркерной группы каждого опознавателя.

2. Устройство по п. 1, отличающееся тем, что в нем опознаватель циклических сдвигов по подциклам маркерной группы содержит схему запоминания, узел обнаружения циклических сдвигов маркерной группы ь расширитель, входы которого соединены с выходами узла обнаружения циклических сдвигов, а управляющий вход объединен с одним из запрещающих входов схемы запоминания.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU300955A1 |

| Резервированное устройство цикловой синхронизации | 1972 |

|

SU443491A1 |

| Устройство синхронизации по циклам | 1975 |

|

SU544160A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство синхронизации по циклам | 1989 |

|

SU1672579A2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

Даты

1971-01-01—Публикация