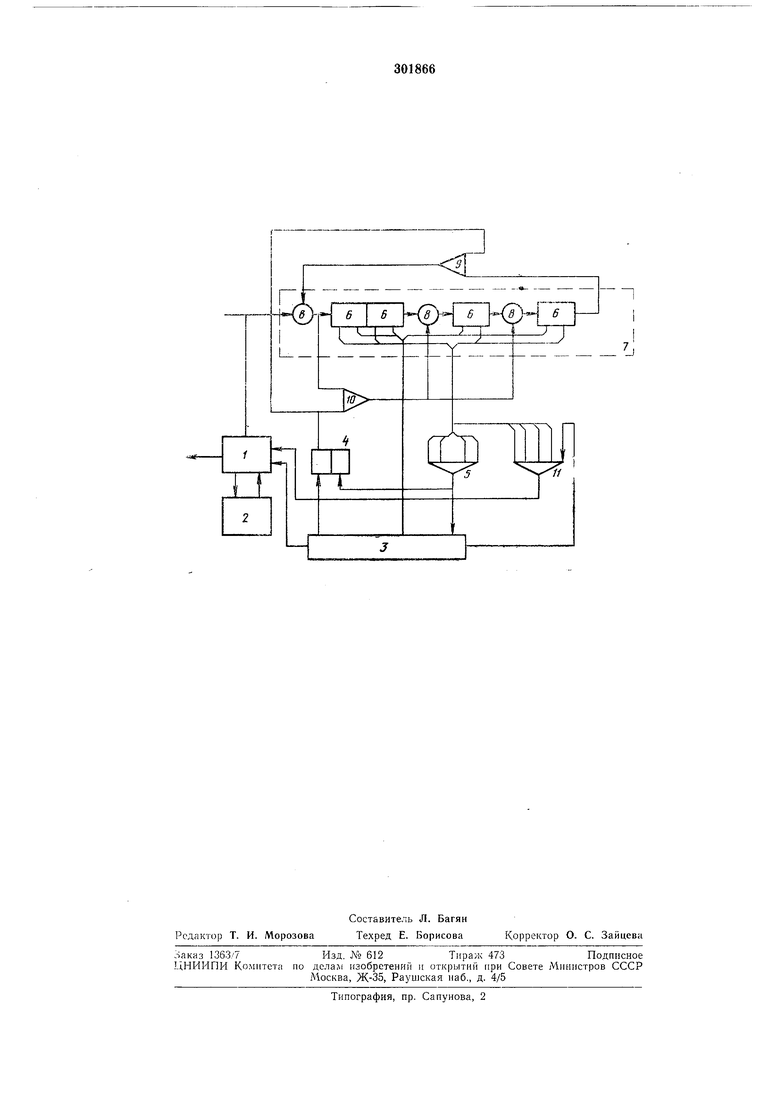

Известны устройства для повышения достоверности двоичной информации, содержащие селектор информационных импульсов, связанный с блоком запоминания информационных импульсов и с рекуррентным регистром сдвига, подсоединенным к блоку проверки достоверности информации по дополнительным разрядам, выполненным в виде регистра сдвига па триггерах со связями через сумматоры по модулю два. С целью унрош,ения устройства при одновременном обеспечении циклового фазирования в предлагаемом устройстве выходы триггеров блока проверки достоверности по дополнительным разрядам связаны через схему «И со входом сброса рекуррентного регистра сдвига, один из выходов которого подсоединен к одному из входов дополнительного триггера, другой вход которого соединен с выходом упомянутой схемы «И, а выход - со схемами «ИЛИ-НЕ, связанными с блоком проверки. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит селектор 1 информационных импульсов, блок 2 запоминающего устройства (ЗУ), рекуррентный регистр сдвига 3, триггер 4, схема «И 5, триггер 6, блок/ проверки достоверности информации по дополнительным разрядам, сумматор 8 по модулю два, схема «ИЛИ-ИЕ 9, схема «ИЛИ-НЕ W, схема «И //. Селектор / информационных импульсов подсоединен к блоку 2 запоминания информационных импульсов и к одно.му из выходов рекуррентного регистра сдвига 3, один из выходов которого подсоединен к триггеру 4, другой - к выходам сброса триггеров 6 блока 7, а вход сброса - к выходу схемы «И 5, подсоединенной к триггеру 4. Выходы схемы «И 5 соединены с триггерами 6 блока 7 проверки достоверности информации по дополнительным разрядам. Л1ел{ду триггерами 6 блока 7 встроены сумматоры 8 по модулю два. Для упрощения чертежа на нем изображен блок 7, содержащий только четыре триггера 6, хотя их количество может быть больше в зависимости от количества разрядов, входящих в состав комбинации циклового фазирования, передаваемой в начале каждого блока информационных импульсов и ;оличества проверочных разрядов, передаваемых после него. Выход одпого из триггеров 6 через схему «ИЛИ-НЕ .9 связан с одним из сумматоров 8, выход которого подключен через схему «ИЛИ-НЕ 10 к другим сумматорам 8.

«И 11, входы которой связаны с триггерами б и с регистром 3.

Информационная последовательность импульсов совместно с комбинацией циклового фазирования и проверочными разрядами поступает параллельно на заблокированные сигналом с регистра 3 вход селектора 7 и на вход одного из сумматоров 8 блока 7. Исходное положение предлагаемой схемы таково, что сигнал управления с выхода триггера 4, подаваемый на входы схем «ИЛИ-НЕ 9 и 10, разрывает цепи обратной связи регистра блока 7, при этом регистр блока 7 работает как обычный сдвигающий регистр.

Информационная последовательность импульсов заполняет регистр блока 7 до тех пор, пока на триггерах 6 этого регистра не.оявится набранная комбинация, соответствующая выбранной комбинации циклового фазирования. На выходе схемы «И 5 в момент набора появляется сигнал, поступающий на вход триггера 4 и вход сброса рекуррентного регистра 3, при этом с выхода триггера 4 на входы схем «ИЛИ-НЕ 10 н 9 поступит сигнал, вновь восстанавливающий разомкнутые до этого цепи обратной связи регистра блока 7, и этот регистр начнет осуществлять проверку правильности принимаемой информации по проверочным разрядам.

Одновременно с этим поступление сигнала с выхода схемы «И 5 на вход сброса рекуррентного регистра 3 устанавливает этот регистр в исходное состояние, и он начинает отсчет количества поступающих с входной клеммы информационных импульсов.

С началом этого отсчета снимается сигнал блокировки, поступающий с выхода рекуррентного регистра 3 на вход селектора /, информационные импульсы записываются с выхода селектора / в блок запоминающего устройства 2. С окончанием отсчета нужного числа информационных импульсов рекуррентным регистром 3 с выхода последнего на вход триггера 4 поступает сигнал, возвращающий его в исходное положение, при этом сигнал с выхода этого триггера, поступающий на входы схем «ИЛИ-НЕ 9 и W вновь разрывает цепи обратной связи регистра блока 7, переводя его в исходный режим «поиска комбинации фазирования.

Сигнал окончания счета импульсов информадии поступает так же на вход схемы «И //. Так как этот сигнал совпадает по времени с моментом возможного появления сигнала «верно, как результата проверки принятой информации по проверочным разрядам, то

сравнение его с результатом декодирования информационных импульсов, образующихся путем поступления сигналов состояния триггера 6 блока 7 на схему «И //, дает сигнал разрещения вывода информации из блока 2

ЗУ через селектор 1 абоненту, который поступает с выхода схемы «И 11 на один из входов селектора 1.

Одновременно с выводом правильно принятой информационной последовательности импульсов абоненту, регистр блока 7 снова начинает поиск и дещифрирование комбинации циклового фазирования.

Предмет изобретения

Устройство для повыщения достоверности двоичной информации, передаваемой по каналам связи, содержащее селектор информационных импульсов, связанный с блоком запоминания информационных импульсов и рекуррентным регистром сдвига, подсоединенным к блоку проверки достоверности информации по дополнительным разрядам, выполненным в виде регистра сдвига на триггерах

со связями через сумматоры по модулю два, отличающееся тем, что, с целью упрощения устройства при одновременном обеспечении циклового фазирования, выходы триггеров блока проверки достоверности информации

по дополнительным разрядам связаны через схему «PI со входом сброса рекуррентного регистра сдвига, один из выходов которого подсоединен ко входу дополнительного триггера, другой вход которого соединен с выходом упомянутой схемы «и, а выход - со схемами «ИЛИ-НЕ, связанными с упомянутым блоком проверки.

1

-(sy 6

X у j Т г

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ ИНФОРМАЦИИ, ПЕРЕДАВАЕМОЙ ЦИКЛИЧЕСКИМ КОДоМ | 1971 |

|

SU316204A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU658771A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| Приемное устройство циклового фазирования | 1983 |

|

SU1085006A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Способ фазирования при передаче информации циклическим кодом | 1973 |

|

SU465748A1 |

Даты

1971-01-01—Публикация