1

Изобретение относится к области техники измерений и может быть использовано при передаче по дискретным каналам связи информации, закодированной циклическим кодом.

Известен способ фазирования при передаче информации циклическим кодом, заключающийся в проверке отрезков принятой информационной последовательности на соответствие ее производящему полипому, получении сигнала несоответствия, который используется для определения сдвига принятой информационной последовательности до вхождения при фазировании в синхронизм.

Недостаток известного способа состоит в том, что вхождение при фазировании в синхронизм занимает много времени из-за того, что сдвиги информационной последовательности осуществляют последовательно - по одному символу за каждую проверку, что приводит к увеличению количества необходимых для вхождения в синхронизм проверок.

С целью повышения скорости вхождения в синхронизм при использовании сигнала несоответствия для определения величины сдвига принятой информационной последовательности формируют импульсный сигнал, длительность которого равна максимально возможному количеству символов сдвига, и с помощью сформированного импульсного сигнала осуществляют запрет необходимого количества

2

импульсов тактовой частоты. Операцию формирования импульсного сигнала, длительность которого равна максимально возможному количеству символов сдвига «т принятой информационной последовательности с числом символов «п в комбинации кода, числом проверочных символов кода «г и номером старщего разряда «i в записи сигнала сдвига, осуществляют в соответствии с тождествами; т.-/г - / ,2, 3 ... г

,- при/:-.1.

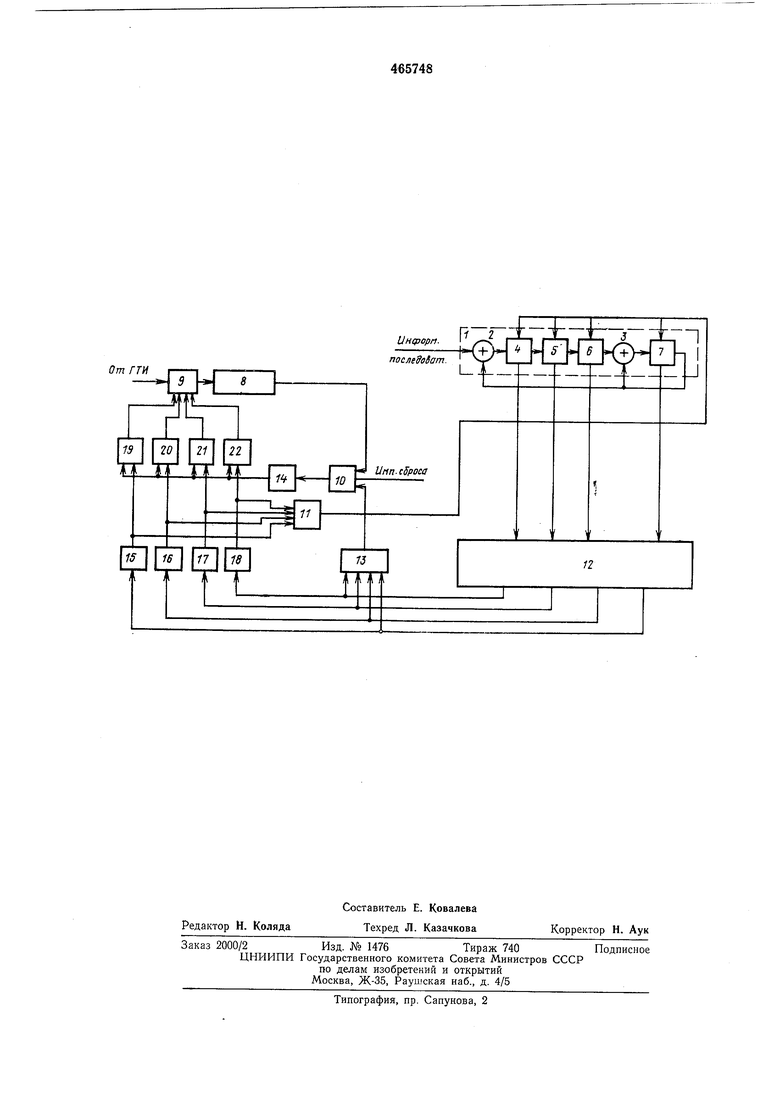

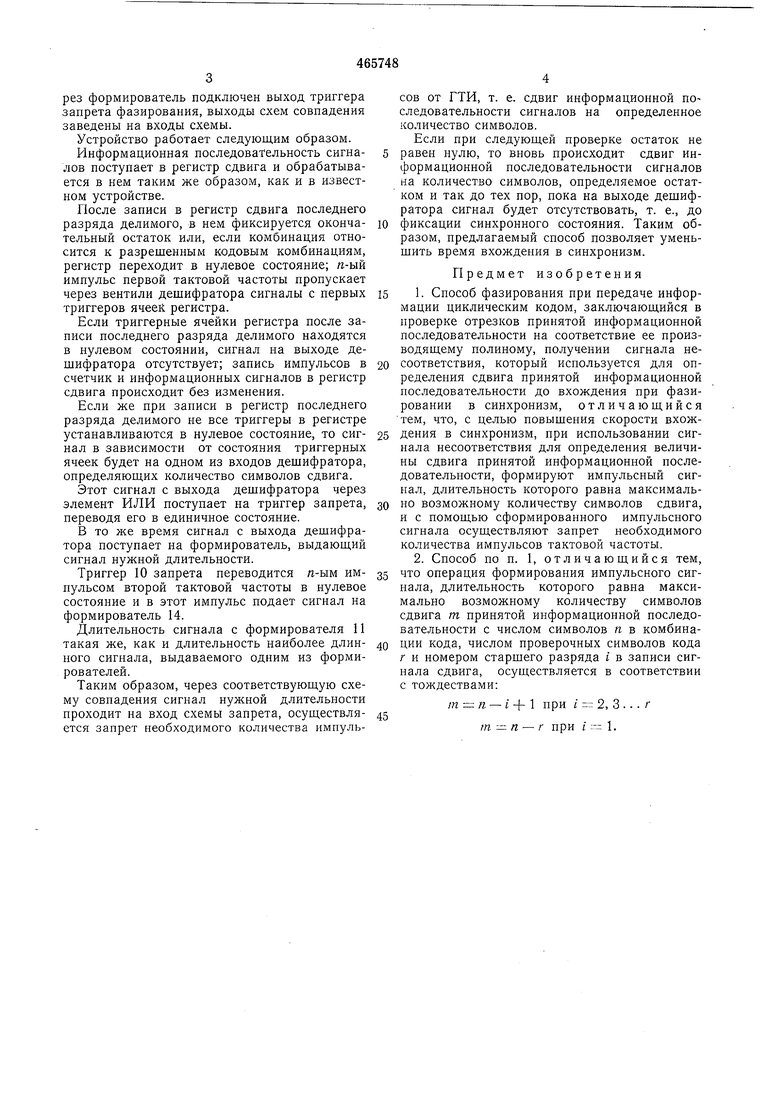

На чертеже представлена блок-схема устройства, реализующего предлагаемый способ.

Устройство содержит регистр сдвига 1, в состав которого входят сумматоры 2 и 3, триггерпые ячейки 4-7, счетчик 8 тактовых импульсов, схема запрета 9, триггер 10 запрета фазирования, формирователь импульсов сброса 11, дешифратор 12, схема ИЛИ 13, формирователи 14-18 длительности импульсов; схемы совпадения 19-22.

Входы дешифратора 12 подключены к выходам регистра сдвига 1, а выходы дешифратора, определяющие число символов сдвига, подключены к схеме ИЛИ и к формирователям, выход схемы ИЛИ подключен к входу триггера запрета фазирования, выходы формирователей соединены с первыми входами

схем совпадения, на вторые входы которых через формирователь подключен выход триггера запрета фазировапия, выходы схем совпадения заведены на входы схемы.

Устройство работает следующим образом.

Информационная последовательность сигналов поступает в регистр сдвига и обрабатывается в нем таким же образом, как и в известном устройстве.

После записи в регистр сдвига последнего разряда делимого, в нем фиксируется окончательный остаток или, если комбинация относится к разрешенным кодовым комбинациям, регистр переходит в нулевое состояние; п-ый импульс первой тактовой частоты пропускает через вентили дешифратора сигналы с первых триггеров ячеек регистра.

Если триггерные ячейки регистра после записи последнего разряда делимого находятся в нулевом состоянии, сигнал на выходе дешифратора отсутствует; запись импульсов в счетчик и информационных сигналов в регистр сдвига происходит без изменения.

Если же при записи в регистр последнего разряда делимого не все триггеры в регистре устанавливаются в нулевое состояние, то сигнал в зависимости от состояния триггерных ячеек будет на одном из входов дешифратора, определяюш.их количество символов сдвига.

Этот сигнал с выхода дешифратора через элемент ИЛИ поступает на триггер запрета, переводя его в единичное состояние.

В то же время сигнал с выхода дешифратора поступает на формирователь, выдающий сигнал нужной длительности.

Триггер 10 запрета переводится /г-ым импульсом второй тактовой частоты в нулевое состояние и в этот импульс подает сигнал на формирователь 14.

Длительность сигнала с формирователя 11 такая же, как и длительность наиболее длинного сигнала, выдаваемого одним из формирователей.

Таким образом, через соответствующую схему совпадения сигнал нужной длительности проходит на вход схемы запрета, осуществляется запрет необходимого количества импульсов от ГТИ, т. е. сдвиг информационной последовательности сигналов на определенное количество символов.

Если при следующей проверке остаток не равен нулю, то вновь происходит сдвиг информационной последовательности сигналов на количество символов, определяемое остатком и так до тех пор, пока на выходе дешифратора сигнал будет отсутствовать, т. е., до фиксации синхронного состояния. Таким образом, предлагаемый способ позволяет уменьшить время вхождения в синхронизм.

Предмет изобретения

1.Способ фазирования при передаче информации циклическим кодом, заключающийся в проверке отрезков принятой информационной последовательности на соответствие ее производящему полиному, получении сигнала несоответствия, который используется для определения сдвига принятой информационной последовательности до вхождения при фазировании в синхронизм, отличающийся тем, что, с целью повышения скорости вхождения в синхронизм, при использовании сигнала несоответствия для определения величины сдвига принятой информационной последовательности, формируют импульсный сигнал, длительность которого равна максимально возможному количеству символов сдвига, и с помощью сформированного импульсного сигнала осуществляют запрет необходимого количества импульсов тактовой частоты.

2.Способ по п. 1, отличающийся тем, что операция формирования импульсного сигнала, длительность которого равна максимально возможному количеству символов сдвига т принятой информационной последовательности с числом символов п в комбинации кода, числом проверочных символов кода г и номером старшего разряда i в записи сигнала сдвига, осуществляется в соответствии с тождествами:

т : п - г -f 1 при / ; 2, 3 .. . г т - п - г при i:- 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU658771A1 |

| Устройство для фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU478450A1 |

| Устройство фазирования аппаратуры передачи информации циклическим кодом | 1974 |

|

SU544161A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство синхронизации по циклам | 1983 |

|

SU1172053A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

Авторы

Даты

1975-03-30—Публикация

1973-04-20—Подача