Изобретение относится к области производства полупроводниковых приборов, в частности кремниевых интегральных схем.

Известен способ получения изолированных обратно сменленным р-п переходом областей монокристаллического кремния, включающий следующие последовательные операции:

создание на поверхности исходной пластины jO-типа слоя окисла;

селективное вытравливание окон в окисле до поверхности кремния;

проведение диффузии д-типа в образовавщиеся окна до создания высоколегированного слоя я+-типа кремния или образование его эпитаксиальным путем;

удаление оставшегося на поверхности пластины слоя окисла;

эпитаксиальное выращивание слоя кремния «-типа на поверхности пластины;

выращивание термического окисла кремния на поверхности эпитаксиального слоя;

селективное вытравливание окон в окисле до поверхности эпитаксиального слоя;

проведение диффузии р-типа в эпитаксиальный слой через окна в окисле до смыкания образовавя1ихся в п-слое участков кремния /7-типа с материалом подложки.

ченных между переходами областей кремния л-типа, в которых создают структуры интегральных схем. Кроме того, создается заглубленный /г+-слой, располагающийся между

эпитаксиальным слоем /i-типа и подложкой р-тпа. Создание п+-слоя преследует цель снижения последовательного сопротивления коллектора транзисторной структуры, образуемой Б л-области, что особенно важно для

транзисторов, работающих в режиме ключа. Однако проведение длительной и весьма критичной операции диффузии /9-типа для создания изолирующих р-«-переходов обходится довольно дорого. Образовавщиеся в

процессе диффузии участки р-типа, разделяющие области /г-типа, имеют в разрезе форму, расщиряющуюся к поверхности и сужающуюся в месте смыкания их с материалом подложки, в результате чего ухудшается плотность компоновки элементов интегральных схем, то есть степень интеграции. Кроме того, при диффузии примеси р-типа в эпитаксиальный tt-слой, а также при последующих высо котемпературных операциях (термическое

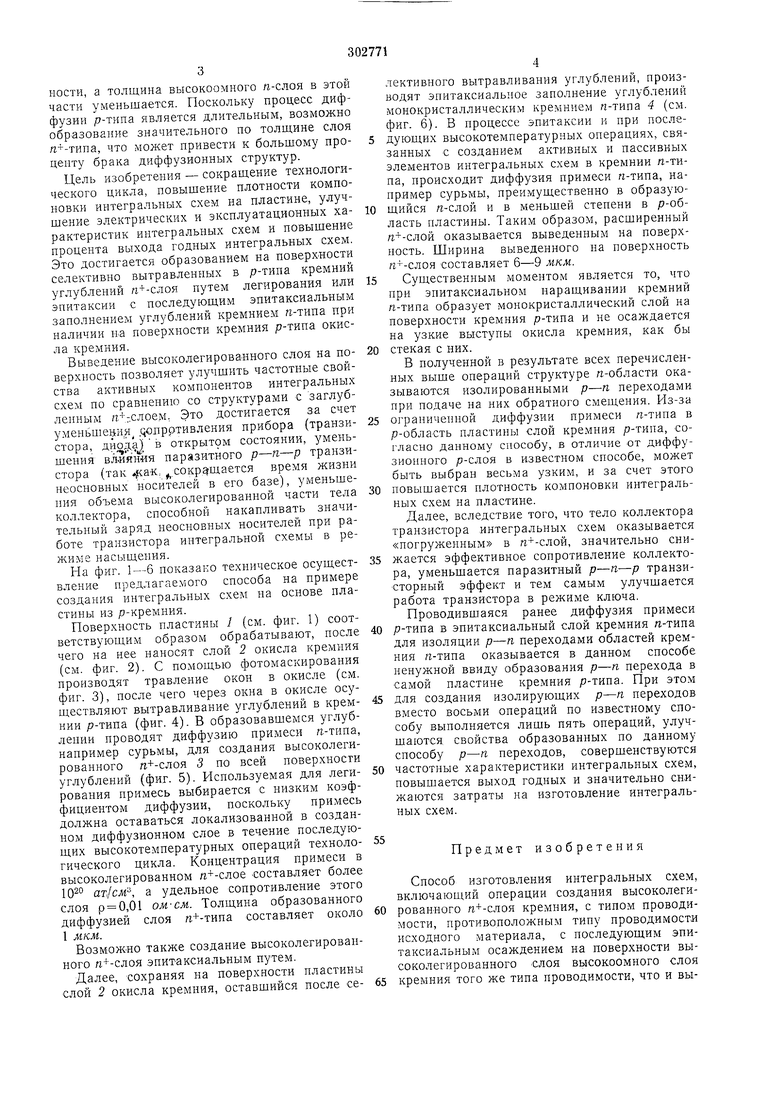

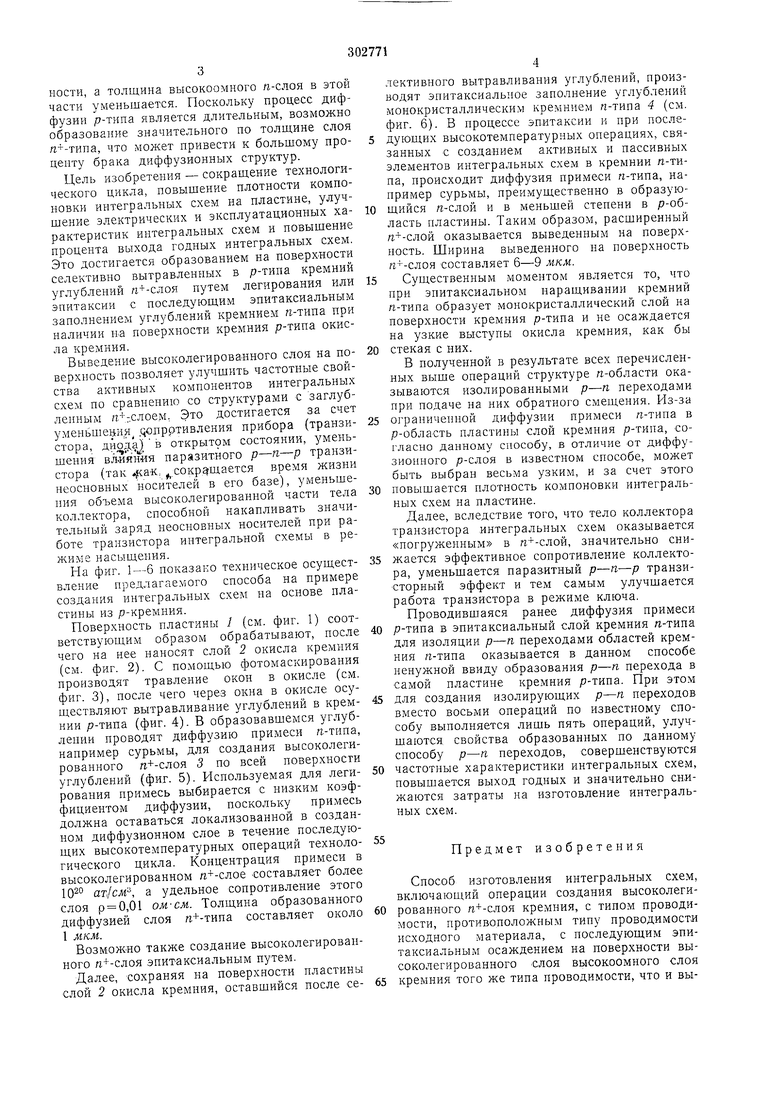

окисление, диффузия при создании активных и пассивных элементов интегральных схем) происходит одновременно диффузия примесей п-типа (например, сурьмы) из /г+-слоя в направлении поверхности, в результате чего ности, а толщина высокоомного п-слоя в этой части уменьшается. Поскольку процесс диффузии р-типа является длительным, возможно образование значительного по толш.ине слоя п+-типа, что может привести к большому проценту брака диффузионных структур. Цель изобретения - сокращение технологического цикла, повышение плотности компоновки интегральных схем на пластине, улучщение электрических и эксплуатационных ха- Ю шение электрических п л.., „, „,,v r-YpM и повышение рактеристик интегральных схем и повышение процента выхода годных интегральных схем. Это достигается образованием на поверхиости селективно вытравленных в р-типа кремний селективно вы-нао........... - ,-. углублений п+-слоя путем легирования или .,,„-0,, пргиппвания или эпитаксии с последующим эпитаксиальным заполнением углублений кремнием ft-типа цри наличии на поверхности кремния р-типа окисла кремния Выведение высоколегированного слоя на поверхность позволяет улучшить частотные свойства активных компонентов интегральных схем по сравнению со структурами с заглубпенным /г+-слоем. Это достигается за счет уменьшеаия долрртивления прибора (транзистора, диода.) в открытом состоянии, уменьшения ВЛИЯНИЯ паразитного р-п-р транзистора (так .ра-к, .сокращается время жизни неосновных носителей в его базе), уменьшеПИЯ объема высоколегированной части тела коллектора, способной накапливать значительный заряд неосновных носителей при работе транзистора интегральной схемы в режим насыщения нГ фиг. V-6 показано техническое осуществление предлагаемого способа на примере создания интегральных схем на основе пластины из р-кремния. Поверхность пластины / (см. фиг. 1) соответствующим образом обрабатывают, после ветствующим 00ра.зиж1 wvjiji v,,, ,„ от, 9 кпемния чего на нее наносят слой 2 окисла кремния (см. фиг. 2). С помощью фотомаскирования производят травление окон в окисле (см. ШИ1. 01, .v. .. „ . 3), после чего через окна в окисле осуществляют вытравливание углублений в кремществляют вытравливание углублений в кремнии р-типа (фиг. 4). В образовавщемся углубНИИ р-типа (фиг. 4). В образовавшемся углуб -л-j-,„„ ппмллрри «.-типа. лении проводят диффузию примеси п-типа, например сурьмы, для создания высоколегированного А+-СЛОЯ 3 по всей поверхности рованного П+-СЛОЯ 3 по всей поверхности углублений (фиг. 5). Используемая для леги /J- к ,rpмяя для легирования примесь выбирается с низким коэффициентом диффузии, поскольку примесь должна оставаться локализованной в созданном диффузионном слое в течение последующих высокотемпературных операций технологического цикла. Концентрация примеси в высоколегированном /г+-слое составляет более 102° аг/сж а удельное сопротивление этого слоя р 0,01 ом-см. Толщина образованного диффузией слоя п+-типа составляет около 1 мкм. „,,,. Возможно также создание высоколегированного П+-СЛОЯ эпитаксиальным путем. Далее, сохраняя на поверхности пластины ективного вытравливания углублений, произодят эпитаксиальиое заполнение углублений монокристаллическим кремнием п-типа 4 (см. фиг. 6). В процессе зпитаксии и при последующих высокотемпературных операциях, связанных с созданием активных и пассивных элементов интегральных схем в кремнии п-типа, происходит диффузия примеси п-типа, например сурьмы, преимущественно в образующийся д-слой и в меньшей степени в р-область пластины. Таким образом, расширенный /г+-слой оказывается выведенным на поверхность. Ширина выведенного на поверхность к+-слоя составляет 6-9 .икж. Существенным моментом является то, что при эпитаксиальном наращивании кремний /г-типа образует монокристаллический слой на поверхности кремния р-типа и не осаждается узкие выступы окисла кремния, как бы стекая с них. В полученной в результате всех перечисленных выше операций структуре я-области оказываются изолированными р-п переходами при подаче на них обратного смещения. Из-за ограниченной диффузии примеси п-типа в р-область пластины слой кремния р-типа, согласно данному способу, в отличие от диффузнойного р-слоя в известном способе, может быть выбран весьма узким, и за счет этого повышается плотность компоновки интегральных схем на пластине. Далее, вследствие того, что тело коллектора транзистора интегральных схем оказывается «погруженным в п+-слой, значительно снижается эффективное сопротивление коллектора, уменьшается паразитный р-п-р транзисторный эффект и тем самым улучшается работа транзистора в режиме ключа. Проводившаяся ранее диффузия примеси р-типа в эпитаксиальный слой кремния м-типа ДЛЯ изоляции р-п переходами областей кремния ге-типа оказывается в данном способе ненужной ввиду образования р-п перехода в самой пластине кремния р-типа. При этом для создания изолирующих р-/г переходов вместо восьми операций по известному способу выполняется лишь пять операций, улучшаются свойства образованных по данному способу переходов, совершенствуются частотные характеристики интегральных схем, повышается выход годных и значительно сниUUi5i31LUac IX-. . j vx.... -жаются затраты на изготовление интеграль ных схем. Предмет изобретения Способ изготовления интегральных схем, включаюашй операции создания высоколегированного п+-слоя кремния, с типом проводимости, противоположным типу проводимости исходного материала, с последующим эпитаксиальным осаждением на поверхности высоколегированного слоя высокоомного слоя

соколегированный слой, отличающийся тем, что, с целью повышения плотности компоновки интегральных схем иа пластине, улучшения электрических и эксплуатационных характеристик интегральных схем, на поверхности селективно вытравленных в кремнии р-типа у1лубленш 1 создают п+-слой с последующим эпитаксиальным заполнением углублений кремнием га-типа при наличии на поверхности кремния р-тина окисла кремния.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1990 |

|

SU1739805A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1981 |

|

SU1116919A1 |

| Способ изготовления полупроводниковых структур с высокоомными диффузионными слоями | 1981 |

|

SU986229A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ | 1990 |

|

SU1686982A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ АВТОМАСШТАБИРУЕМОГО БИПОЛЯРНОГО ТРАНЗИСТОРА | 2002 |

|

RU2234162C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ | 1982 |

|

SU1085439A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА В СОСТАВЕ БиКМОП ИС | 2001 |

|

RU2208265C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1840163A1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КОМПЛЕМЕНТАРНЫХ ВЕРТИКАЛЬНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРОВ В СОСТАВЕ ИНТЕГРАЛЬНЫХ СХЕМ | 2003 |

|

RU2244985C1 |

fua 3

Риг В «

Авторы

Даты

1971-01-01—Публикация