Изобретение относится к цифровым арифметическим устройствам для аппаратного деления итерационным методом при помощи умножений.

Метод Пьютона состоит в вычислении об- 5 ратной величины делителя по итерационной формуле:

(2-YiX),(1)

где X - делитель;10

У -обратная величина делителя;

i - номер итерации, 1 0; 1; 2 ....

При YO - начальное приближение к 15 обратной величине Y.

Итерации (1) выполняются в виде двух шагов:

1шаг: Хг+1-YiX(2) о

1+1 2-Хг+1.(3)

2шаг:Yi+, (4)

Известно цифровое устройство для умножения и деления итерационным методом Ныо- 25 тона, по два шага в итерации, с использованием умножений, содержаш,ее входные и выходные регистры, блок управления, блок для формирования и суммирования частичных произведений, блок для хранения таблицы на- ЗО

чального приближения к обратной величине делите.чя.

В известном устройстве уменьшения методической погрешности необходимо увеличить или разрядность таблицы начального приближения к обратной величине делителя или количество итераций. Первое связано с большими затратами оборудования, второе - с потерей скорости.

Цель изобретения - уменьшение методической погрешности деления ных затратах оборудования рости.

Предлагаемое устройство что оно содержит клапаны ректирующего слагаемого, входы которых соединены с для нахождения начального

ооратнои величине делителя и с выходами входного регистра, управляюгцие входы соединены с выходами блока управления. Выходы клапанов соединены со входами блока для формирования и суммирования частичных произведений.

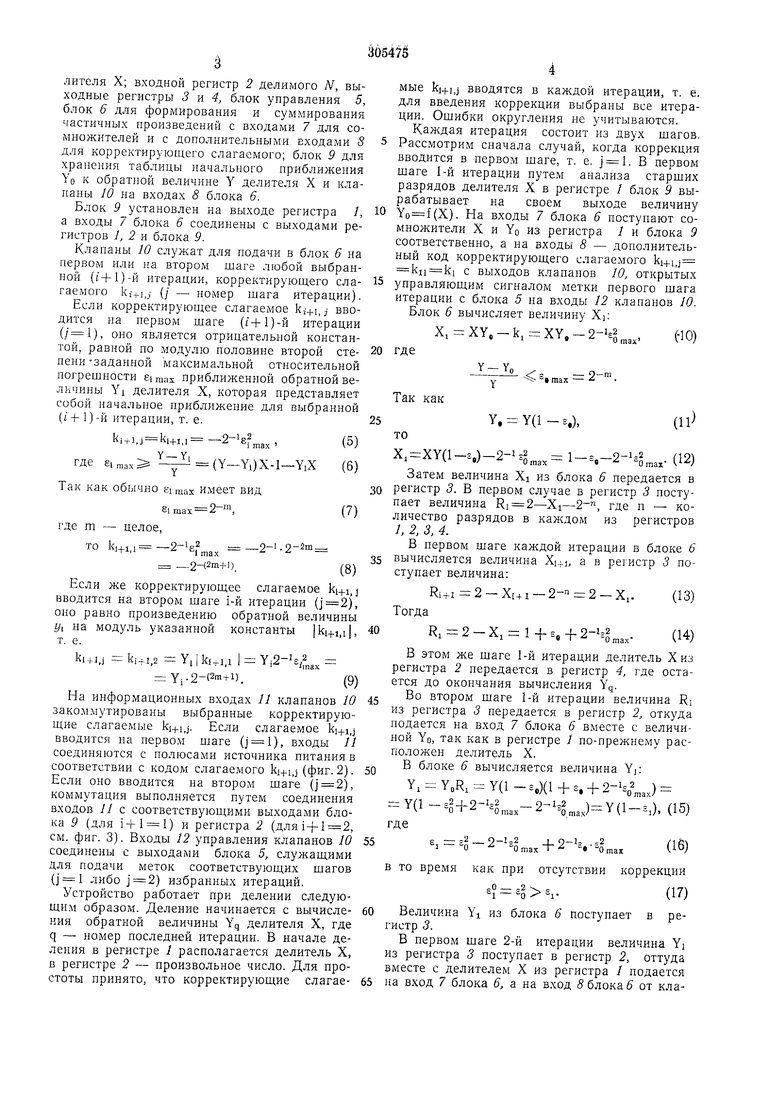

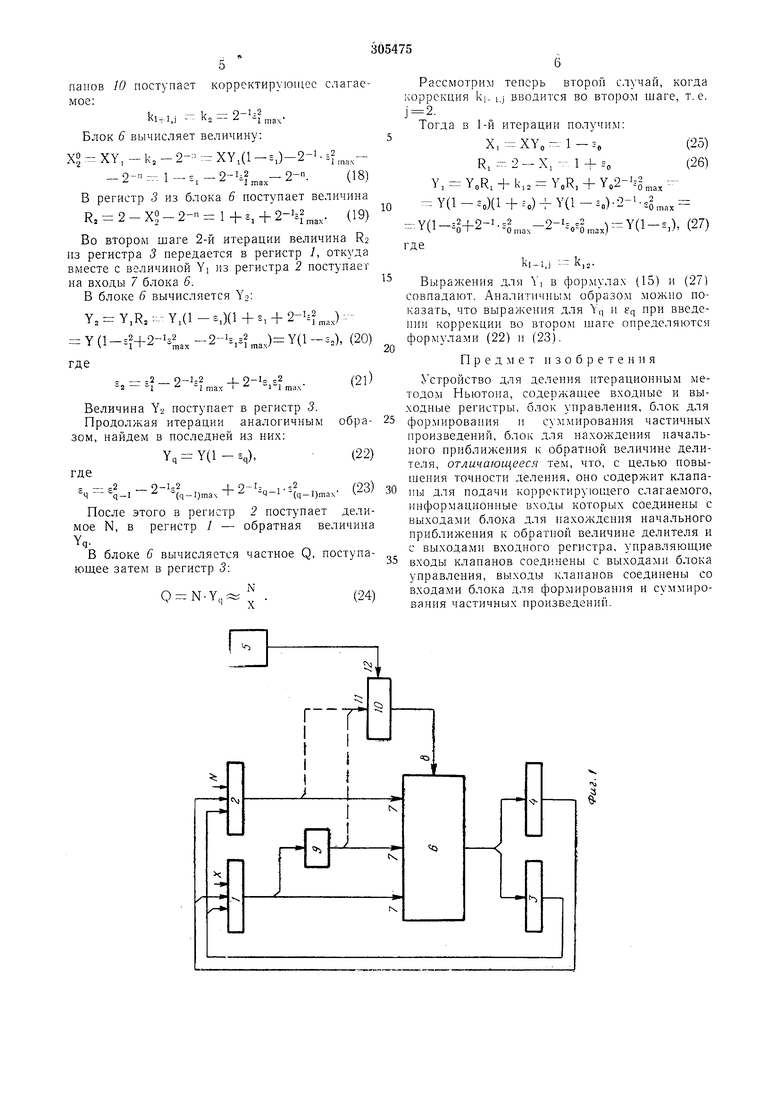

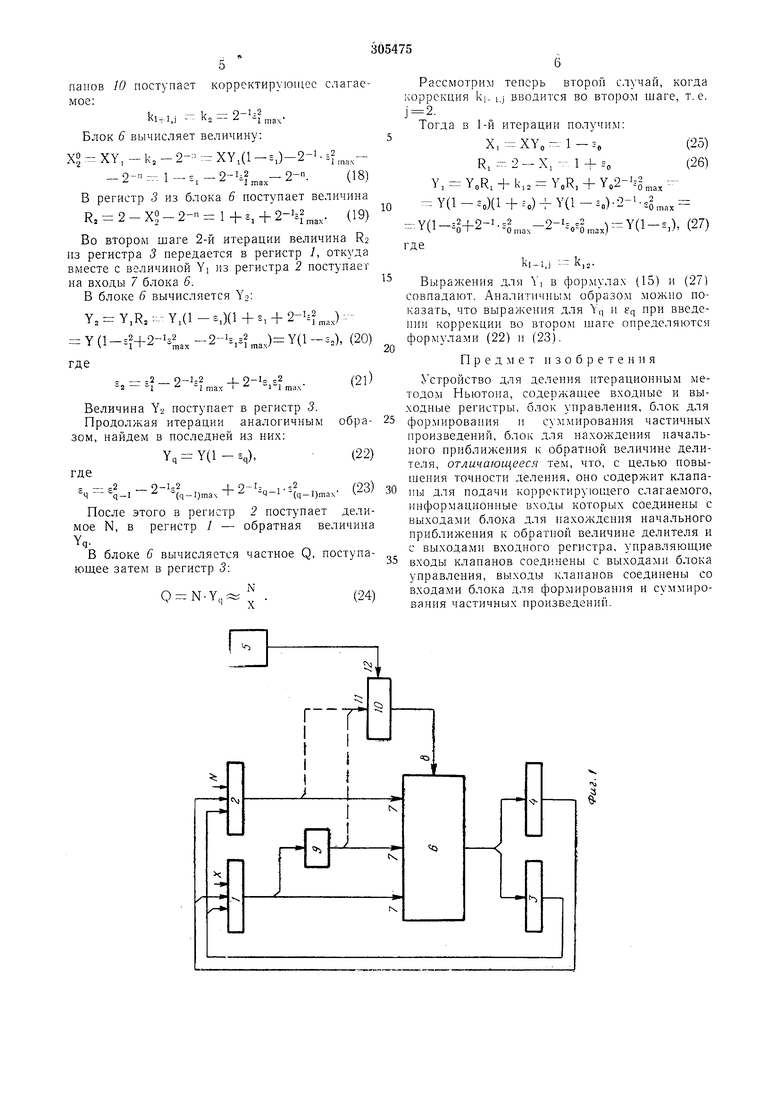

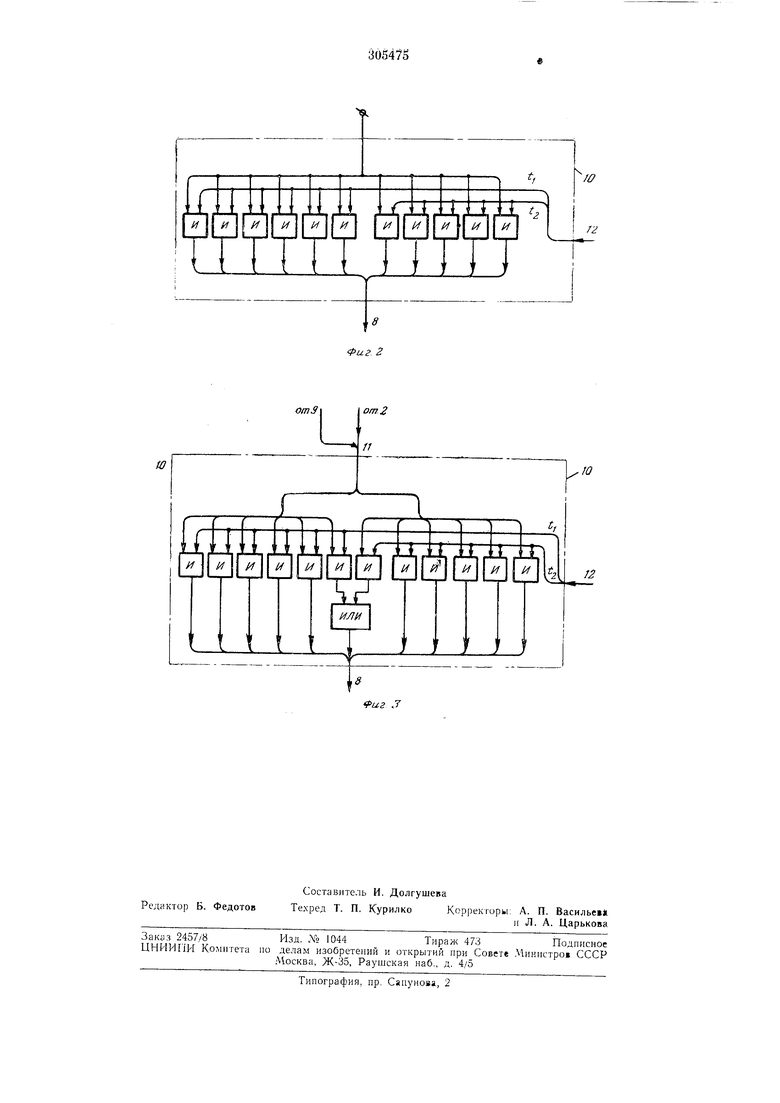

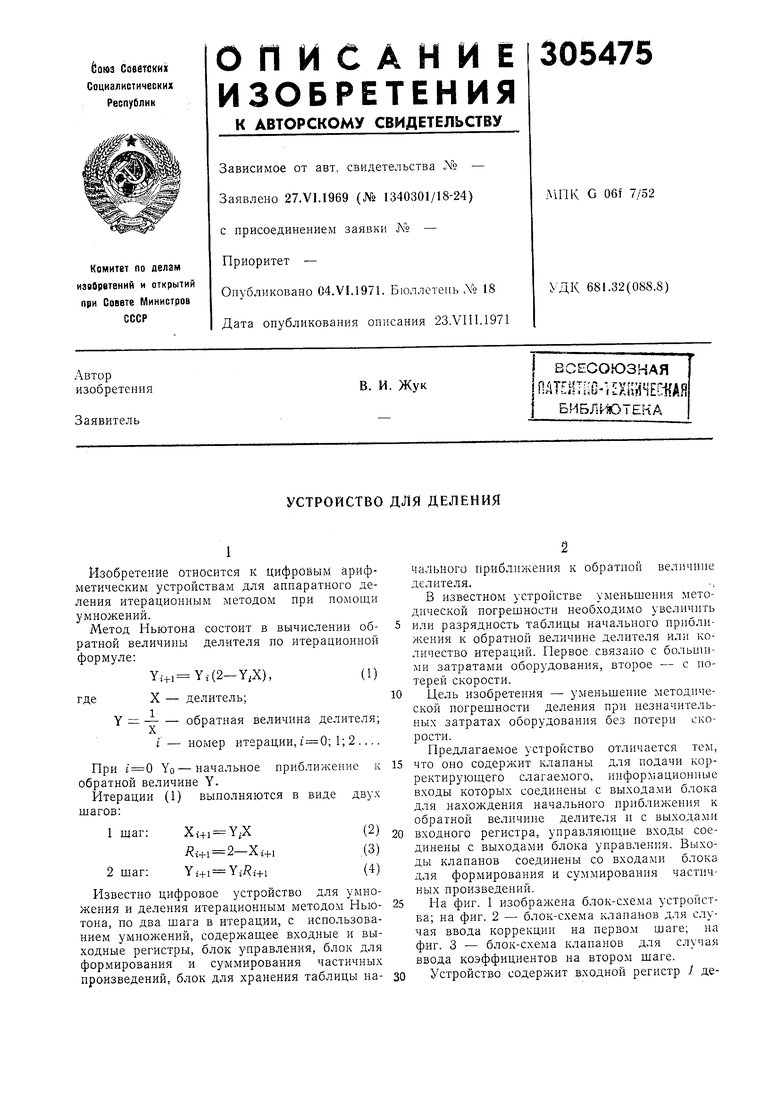

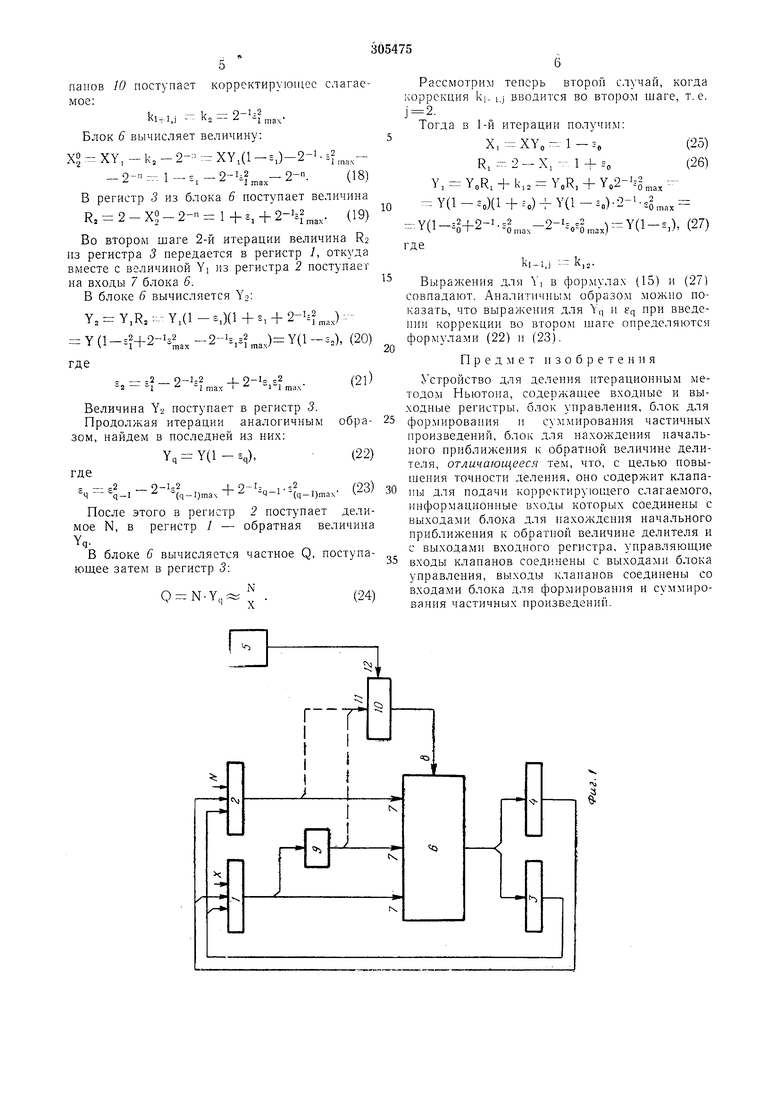

Па фиг. 1 изображена блок-схема устройства; на фиг. 2 - блок-схема клапанов для случая ввода коррекции на первом шаге; на фиг. 3 - блок-схема клапанов для случая ввода коэффициентов на втором шаге. лителя X; входной регистр 2 делимого Л/, выходные регистры и 4, блок управления 5, блок 6 для формирования и суммирования частичных произведений с входами 7 для сомножителей и с дополнительными входами 8 для корректирующего слагаемого; блок 9 для хранения таблицы начального приближения YO к обратной величине Y делителя X и клапаны W на входах 8 блока 6. Блок 9 установлен на выходе регистра /, а входы 7 блока 5 соединены с выходами регистров 7, 2 и блока 9. Клананы 10 служат для подачи в блок 6 на первом или на втором шаге любой выбранной (г+1)-й итерации, корректирующего елагаемого ki+,j {/ - номер щага итерации). Если корректирующее слагаемое ki+i,j вводится на нервом шаге (i-fl)-й итерации (), оно является отрицательной константой, равной по модулю половине второй стенени заданной максимальной относительной погрещности esmax приближенной обратной величины YI делителя X, которая представляет собой начальное приближение для выбранной (/+1)-й итерации, т. е. k..u-l.+,,, ,,.(5) Y-Y, (Y-Y,)X-I-Y,X (6) где si, Так как обЕлчно simax имеет вид Simax 2-™,(7) где m - целое, то k,+i,, 2-8f,. -2-.2-2. 2-(2п1+1),(8) Если же корректирующее слагаемое ki+i, j вводится на втором шаге i-й итерации (), оно равно произведению обратной величины У1 на модуль указанной константы jki+i,ij, т. е. ki+jj ki.,1,2 Y, i k,M I : Yi2-44, Yr2-(2ra + l).(9) Ha информационных входах 11 клапанов 10 закоммутированы выбранные корректирующие слагаемые kj+ij. Если слагаемое ki+ij вводится на нервом шаге (j l), входы 11 соединяются с полюсами источника питания в соответствии с кодом слагаемого ki+u (фиг. 2). Если оно вводится на втором шаге (j 2), коммутация выполняется путем соединения входов 11 с соответствующими выходами блока 9 (для i + l I) и регистра 2 (для 1+1 2, см. фиг. 3). Входы 12 управления клапанов 10 соединены с выходами блока 5, служащими для подачи меток соответствующих шагов (j l либо j 2) избранных итераций. Устройство работает при делении следующим образом. Деление начинается с вычисления обратной величины Yq делителя X, где q номер последней итерации. В начале деления в регистре 1 располагается делитель X, в регистре 2 - произвольное число. Для простоты принято, что корректирующие слагаемые ki+ij вводятся в каждой итерации, т. е. для введения коррекции выбраны все итерации. Ошибки округления не учитываются. Каждая итерация состоит из двух шагов. Рассмотрим сначала случай, когда коррекция вводится в первом шаге, т. е. . В первом шаге 1-й итерации путем анализа старших разрядов делителя X в регистре / блок 9 вырабатывает на своем выходе величину (X). На входы 7 блока 6 поступают сомножители X и YO из регистра I и блока 9 соответственно, а на входы 8 - дополнительный код корректирующего слагаемого ki+i,j с выходов клапанов 10, открытых управляющим сигналом метки первого шага итерации с блока 5 на входы 12 клапанов 10. Блок 6 вычисляет величину Хь X,XY.-k,,-2-4, где fgj . Y(l - g, то .3x- (12) X,-XY(l-s.)-2-4§, l-.. Затем величина Xi из блока 6 передается в регистр 3. В первом случае в регистр 5 поступает величина Ri 2-Xi-2 где п - количество разрядов в каждом из регистров 1. 2, 3, 4. В первом шаге каждой итерации в блоке 6 вычисляется величина .i, а в регистр 3 поступает величина: Ri+i 2-Xi+i-2- : 2-X,.(13) R,-2-X, l+s.+2-b2.(14) В этом же шаге 1-й итерации делитель X из регистра 2 передается в регистр 4, где остается до окончания вычисления Yq. Во втором шаге 1-й итерации величина Rj из регистра 3 передается в регистр 2, откуда нодается на вход 7 блока 6 вместе с величиной YO, так как в регистре / по-прежнему расположен делитель X. В блоке 6 вычисляется величина Yj: Y, , Y(l - s,)(l + e. + , 2 I 0-Ic2 -.). (15) . Y/. Omax Omax (16) J 9-1 .2 9-U2 0 max Omax коррекции (17) В TO время как при отсутствии 0 c2 1- -0 -1Величина YI из блока 6 поступает в регистр 3. В первом шаге 2-й итерации величина YI из регистра 3 поступает в регистр 2, оттуда вместе с делителем X из регистра / подается на вход 7 блока 6, а на вход Яблока5 от клапанов 10 поступает KoppCKTHpyioniec слагаемое:kb-l.j .. k,:r.2-32,. Блок 6 вычисляет величину: Х :. XY, - k, - : ХУ,(1 -s,)-2-. Ln.x-2--. l-s,-2-.,,-2.(18) В регистр 5 из блока 6 поступает величина R,r.2-X°-2- l+s, + 2-32. (19) Во втором шаге 2-й итерации величина Rs из регистра 3 передается в регистр /, откуда вместе с величиной YI из регистра 2 поступает на входы 7 блока 6. В блоке 6 вычисляется Yo: Y, : Y,R, ::-: Y,(l - S,)(l + S, + 2- „J v- Y(,, -2-s,s):.Y(l-3,), (20) где I 9-1- -2 T max Величина Ya поступает в регистр 3. обраПродолжая итерации аналогичным зом, найдем в последней из них: Y(l - q). ...2 Я - 1 -q-l -(q-l)max (а-Отач После ЭТОГО в регистр 2 поступает делимое N, в регистр / - обратная величина В блоке 6 вычисляется частное Q, поступающее затем в регистр 3. 0.N-Yq .(24) (22) (23) Рассмотрим теперь второй случай, когда оррекция kj. 1 i вводится во втором шаге, т. е. Тогда в 1-й итерации получим: X, r--::XYor--l-S,(25) R, ,-: l-fso(26) Y YoRi + 1,2 oR + Y(,2 --5 max -: Y(l - з„)(1 + г„) -f Y(l - г„).2-., :Y(l .,,-2-Ч„з2 Y(l-3,), (27) де ki-ij k,2Выражения для YI в формулах (15) и (27) совпадают. Апалитичиым образом можно показать, что выражения для Yq и gq при введении коррекции во втором шаге определяются формулами (22) и (23). Предмет изобретения Устройство для деления итерационным методом Ньютона, содержащее входные и выходные регистры, блок управления, блок для формирования и суммирования частичных произведений, блок для нахождения начального приближения к обратной величине делителя, отличающееся тем, что, с целью повышения точности деления, оно содержит клапаны для подачи корректирующего слагаемого, информационные входы которых соединены с выходами блока для нахол дения начального приближения к обратной величине делителя и с выходами входного регистра, управляющие входы клапанов соединены с выходами блока управления, выходы клаианов соединены со входами блока для формирования и суммирования частичных произведений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Расходомер двухфазных сред | 1990 |

|

SU1783304A1 |

| ВСЕСОЮЗНАЯ I | 1973 |

|

SU362296A1 |

| Линейно-круговой интерполятор | 1977 |

|

SU732818A1 |

| Устройство для деления | 1989 |

|

SU1665374A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| ВО СОЮЗНАЯ-:.l;Jbi.{) 'ii.K^i'-EOiiliБИБЛИОТЕКАВ. И. Жук | 1971 |

|

SU318940A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ | 1971 |

|

SU302716A1 |

| СОЮЗНАЯ Iмшшда^'"""ЙИБЛИОТЕК^ | 1972 |

|

SU331386A1 |

| Устройство для деления | 1985 |

|

SU1262480A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

2

ШП

ИНЫИ

Даты

1971-01-01—Публикация