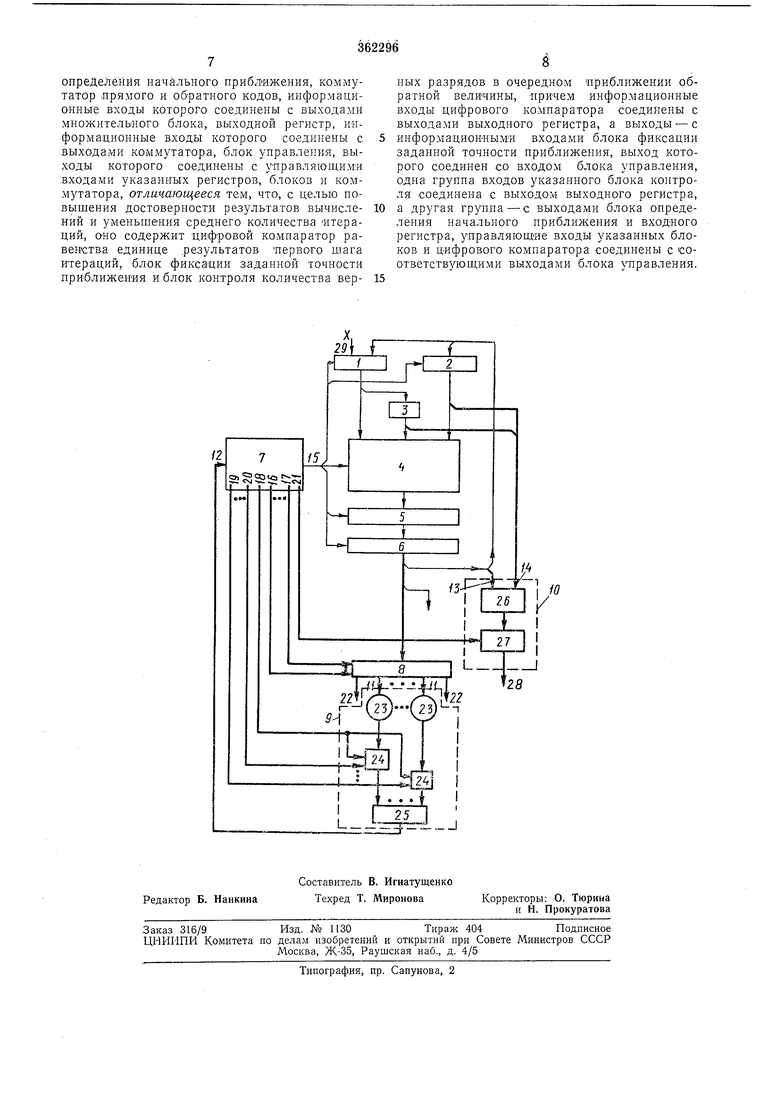

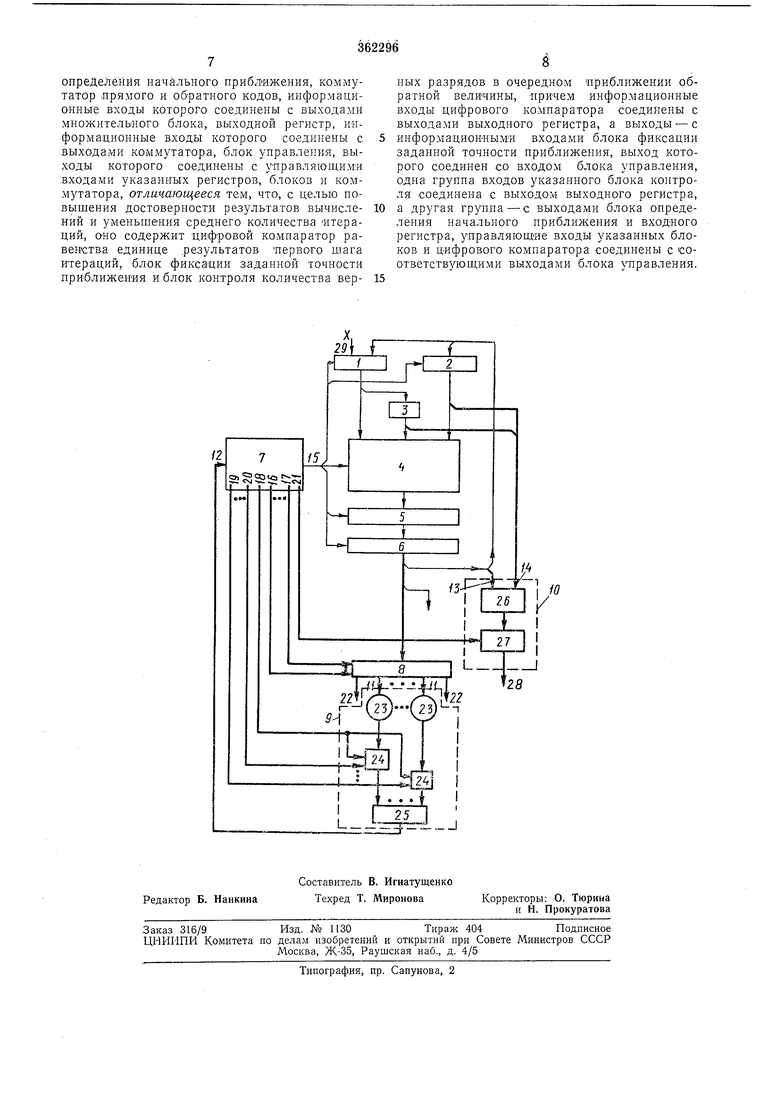

Изобретение относится к области автоматики и вычислительной техники и -предназначено для вычисления обратной величины нормализованной двоичной дроби с обнаружением ошибок. Известны устройства для вычисления обратной величины нормализованной двоичной дроби, содержащие входные регистры, блок определения начального приближения обратной величины, множительный блок, ком.мутатор прямого и обратного кодов, выходной регистр, блок управления. Предложенное устройство отличается тем, что оно содержит цифровой компаратор равенства единице результатов первого шага итераций, блок фиксации заданной точности приближения и блок контроля количества верных разрядов в очередном приближении обратной величины, причем информационные входы цифрового компаратора соединены с выходами выходного регистра, а выходы-с информационными входами блока фиксации заданной точности приближения, выход которого соединен со входом блока управления, одна группа входов указанного блока контроля соединена с выходом выходного регистра, а другая группа - с выходами блока определения начального приближения и входного регистра, управляющие входы указанных блоков и цифрового, компаратора соединены с соответствующими выходами блока управления. Это позволяет повысить достоверность результатов вычислений путем контроля результатов шагов итераций и у.меньшить среднее количество итераций путем фиксации мо.мента достижения заданной точности приблил еиия. Схема устройства изобралсена на чертеЛ е. Устройство содерл ит входные регистры Д 2, блок 3 начального приближения уо обрат1„ , . НОИ величины , .мнол ительиыи олок 4, коммутатор 5 прямого и обратного кодов, выходной регистр 6, блок 7 уиравления, цифровой компаратор 8 равенства единице результатов первого шага итераций с точностью до разряда, определяемого номером итерации, блок 9 фиксации заданной точности приближения и блок JO контроля количества верных разрядов в очередном приближении обратной величины. Выходы 11 компаратора 8 соединены с информационными входами блока 9, выход которого соединен со входом 12 блока 7 травления. Одна группа информационных входов 13 блока 10 контроля соединена с выходом регистра 6, а другая группа информационных входов 14 блока 10 соединена с выходами блока и регистра 2. Управляющие входы регистров /, 2, 6, множительного блока 4, коммутатора 5 соединены с соответствующими выходами 15 блока 7 управления. Управляющие входы компаратора 8 соединены с выходами 16; 17 блока 7 управления, служащими для подачи меток первого шага итераций, выбранных для контроля. Управляющие входы блока 9 соединены с выходами 18, 19, 20 блока 7 управления, причем выход 18 служит для подачи метки первого щага всех итераций, а выходы 19, 20 - для Подачи управляющих сигналов, задающих требуемую точность вычислений. Управляющие входы блока 10 контроля соединены с выходами 21 блока 7 управления, служащими для подачи меток второго шага итераций, выбранных для контроля. iKoMnapaTOp 8 служит для контроля количества верных разрядов результатов первого щага итера-ций лутем сравнения на равенство этих результатов и единицы с точностью, OTIределяемой номером итерации. Осуществление такого сравнения о-беспечено тем, что «омпаратор 8 выполнен в виде логического узла, определяющего несовпадение между собой значений контролируемых старщих разрядов дробной части и инверсного значения разряда целых единиц в сраВНиваемОМ результате первого тага итераций, причем указанные контролируемые разряды составляют слова переменного формата, длина которого зависит от номера итераций. В связи с этим компаратор 8 имеет переменный формат, зависящий от номера итерации. В компараторе количества выходов 11 и выходов 22 равны количеству -итераций, причем каждый выход 11 и 12 служит для выдачи в соответствующей итерации сигнала ощибки, который вырабатывается в случае «арущения указанного равенства единицы и результата первого щага этой итерации, но |формирование сигналов на выходах 11 не зависит от управляющих сигналов блока 7 управления. Блок 9 фиксации заданной точности приближения выполнен из инверторов 23, соединенных С информационными входами блока 9, элементов «И 24, у которых информацион-ные входы соединены с выходами инверторов 23, а управляющие входы - с выходами 18, 19, 20 блока 7 управления, элемента «ИЛИ 25, у которого входы соединены с выходами элементов «И 24, а выход служит выходом блока 9 и соединен со входом 12 блока 7 управления. Блок/О контроля количества верных разрядов в очередном приближении обратной величины выполнен в виде сумматора 25и цифрового компаратора 27равенства нулю результатов, получаемых в сумматоре 26 на втором щаге итераций, с точностью до разряда, определяемого номером итерации. Входы сумматора 26 служат входами блока 10, выходы сумматора 26 соединены с информационными входами компаратора 27, у которого управляющие входы соединены с выходами 21 блока 7 управления, а выходы 28 являются выходами блока 10 и служат для выдачи сигнала ощибки в случае нарущения указанного неравенства нулю результатов, получаемых в сумматоре 26 на втором щаге итераций. Для осуществления указанного сравнения с нулем ком паратор 27 выполнен с переменным форматом, зависящим от номера итерации. Устройство работает следующим образом. В исходном состоянии на одном из выходов 19, 20 блока 7 управления устанавливается сигнал «1, разрещающий работу одного из элементов «И 24. Таким образом задается требуемая точность, результирующего приближения обратной величины. В регистр / по входу 29 поступает делитель X, а на выходе блока 3 устанавливается величина УО начального приближения величины у - (). В первом щаге (такте) первой итерации с помощью множительного блока 4 вычисляется величина: 1 JCi/o,(1) которая Передается через коммутатор 5 в обратном коде. ВследстБие этого на выходе коммутатора получается первый множитель R бесконечного произведения: 1,:2-Х,2-ху,.(2) Множитель RI принимается в регистр 6. В формулах (1), (2) и в последующем изложении для простоты не учтены погрешности умножения и вычитания. Множитель RI, определяемый формулой (2), может быть выражен через относительную погрешность so начального приближения УО: 1 + е„,(3) , .(4) Максимальное по модулю значение погрешности определяется конструкцией блока 3 и равно где /По - целое число, . С учетом выражений, (3), (5) результат первого щага первой итерации должен удовлетворять двойному неравенству: 1 - 2- , 1 + ,(6) Компаратор 8 проверяет двойное неравенство (6) путем сравнения на равенство единицы и множителя R с точностью до величи:чы , т. е. с точностью до ki-ro разряда дробной части множителя Ri, где ki tno-1. При. этом контролируемые разряды множителя RI составляют число формата, соответствующего первой итерации. Это число содержит разряд целых единиц и fti разрядов дробной части множителя Ri. В случае нарущения

неравенства (6) компаратор 8 вырабатывает сигнал ошибки на одном из своих выходов 22, соответствующем первой итерации.

В «ачале второго шата (такта) пе;рвой итерации множитель из регистра 6 передается в регистр 2. В регистре /по-прежнему сохраняется делитель х, а блок 3 вырабатывает величину г/о. Множительный блок 4 вычисляет первое приближение обратной величины г/i;

-г/: г/о/,,(7)

Величина yi в прямом коде передается через коммутатор 5 и принимается в регистр 6.

В соответствии с выражениями (3), (4), (7) величины УО и г/i можно представить в виде: где

у, у( - So);(8)

,)-(9)

s,-sg,(10)

Гарантированные количества верных разрядов в величинах г/о и r/i с учетом (5) соответственно будут:

Я,Хт„-1;(11

Р, т,-1 2„„-1,(12)

На вход сумматора 26 подаются: число у

из регистра 6 и число г/о с выхода блока 5.

Сумматор вычисляет модуль разности этих

чисел:

-г/о| г/К -s,|,(13)

С учетом (5), (10) получим при г/тах 2:

, у, - г/„| 2- (-0-1) 2-о. (14)

Компаратор 27 проверяет выполнение неравенства (14) путем сравнения на равенство нулю величины 5i с точностью до величины 2 , т. е. с точностью до ро-то разряда дробной части величины Si. Это сравнение основано на проверке равенства нулю числа, расположенного в то старших разрядов величины Si, включая разряд целых единиц. В случае нарушения неравенства (14) компаратор 27 вырабатывает на выходе 28 сигнал ошибки в гервой итерации.

В первом шаге второй итерации величина .(/1 из регистра 6 передается в регистр 2. В регистре / сохраняется делитель х. С помощью множительного блока 4 и коммутатора 5 вычисляется второй множитель бесконечного произведения:

3 2 - ху,,(15)

который принимается в регистр 6.

С учетом (9), (10) множитель Rz можно представить в виде:

/, 1 + S, : 1 + е2.(16)

С учетом (5), (16) должно выполняться условие:

1-2- - 5 1+2- ,(17)

где

т 2то.(18)

Компаратор 8 проверяет условие (18) ив случае его невыполнения вырабатывает сигнал ошибки на одном из своих выходов 22, соответствующем второй итерации. При этом контролируемые разряды множителя R составляют число формата, соответствующего второй итерации. Это число содержит nii разрядов, включая разряд целы.х единиц, и /г2 старших разрядов дробной части, где k nil - 1.

Во втором шаге второй итерации множитель 2 поступает с регистра 1, а в регистре 2 сохраняется число г/i. С помощью множительного блока 4 и коммутатора 5 вычисляется второе приближение г/2 обратной величины:

У. УЛ-(19)

которое поступает в регистр 6.

На вход сумматора 26 подаются число г/2 из регистра 6 и число г/i из регистра 2. Сумматор вычисляет модуль разности этих чисел:

S, y,-y,.(20)

При этом с учетом (12) должно выполняться условие:

О 5j -(-) .(21

Компаратор 27 проверяет неравенство (21) и в случае его невыполнения вырабатывает на выходе 28 сигнал ошибки во второй итерации.

В первом шаге третьей итерации В регистр / поступает делитель х, а ъ регистр 2 передается число г/2 из регистра 6, и итерационный процесс продолжается, как во второй итерации.

Контроль и фиксация момента достижения требуемой точности приблил ения z/j+i на (/-+-1)-й итерации, производится блоком 9 следующим образом.

При отсутствии ошибок в первом шаге некоторой итерации на соответствующем этой итерации выходе 11 компаратора 8 формируется сигнал «О, а на выходе инвертора 23, соединенного с указанным выходом компаратора 8, формируется сигнал «1. Когда этот сигнал «1 появится в первом щаге некоторой итерации на входе этого элемента «И 24, который выбран в исходном состоянии устройства управляющими сигналами с выходов 19, 20 блока 7 управления, то на выходе элемента «ИЛИ 25 сформируется сигнал «1, который подается на вход 12 блока 7 управления и останавливает итерационный процесс после выполнения второго шага этой итераци.

Предмет изобретения

Устройство для вычисления обратной величины нормализованной двоичной дроби, содержащее входные регистры, блок определения начального приближения обратной величины, входы которого соединены с выходами одного из входных регистров, множительный блок, информационные входы которого соеди-, нены с выходами входных регистров и блока

| название | год | авторы | номер документа |

|---|---|---|---|

| СОЮЗНАЯ Iмшшда^'"""ЙИБЛИОТЕК^ | 1972 |

|

SU331386A1 |

| Функциональный преобразователь | 1986 |

|

SU1456951A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для определения обратной величины числа | 1989 |

|

SU1649536A1 |

| Функциональный преобразователь | 1980 |

|

SU924714A1 |

Авторы

Даты

1973-01-01—Публикация