Изобретение относится к области цифровой вычислительной техники, в частности к цифровым арифметическим устройствам для вычисления обратной величины итерационным методом с использованием умножения. Аппаратное вычисление обратной величины используется в цифровых арифметических устройствах для реализации операции деления.

В известном цифровом устройстве для вычисления обратной величины аргумента итерационным методом Ньютона с использованием умножения, содержащем входные и выходные регистры, блок управления, дешифраторы множителя, коммутаторы частичных произведений, преобразователь многорядного кода частичных произведений в двухрядный код, сумматор для преобразования этого двухрядного кода в однорядный, блок для определения начального приближения к обратной величине аргумента, в одной итерации требуются два умножения, и, вследствие этого, - большие затраты времени.

Метод Ньютона состоит в вычислении обратной величины делителя по итерационной формуле:

j/i. (2-i/; Я ),(1)

где л; - аргумент;

t - номер итерации.

При , Z/0 - начальное приближение к обратной величине у.

Итерация (1) выполняется в виде двух шагов, требуюш.их по одному умножению. . 1-й шаг:

X; -,- ; yi X(-2

Ri .2-X; i(3

2-й шаг: г/, i// ,(4)

Предлагаемое устройство, с целью повышения скорости вычислений, дополнительно содержит квадратор начального приближения и группы клапанов, выход блока определения начального приближения соединен со входом квадратора начального приближения и со входами первой группы клапанов, выход квадратора начального приближения соединен со входом дешифратора .множителя, выходы первой и второй групп клапанов соединены со входами преобразователя многорядного кода в двухрядный, выходы которого через третью группу клапанов соединены со входами сумматора, вход младшего разряда которого дополнительно соединен с выходом четвертой группы клапанов, управляющие входы всех групп клапанов соединены с соответствующими выходами блока управления.

жений в 1-ой «итерации в два раза, т. е. выполнить первую итерацию за один шаг (такт).

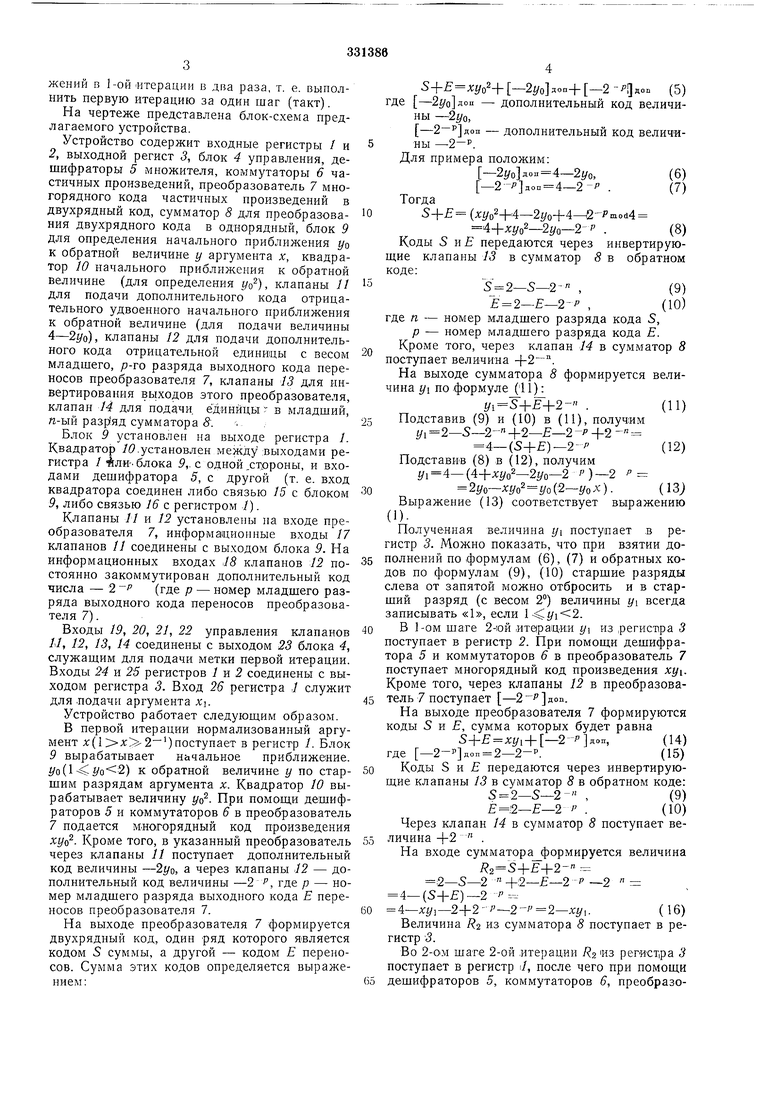

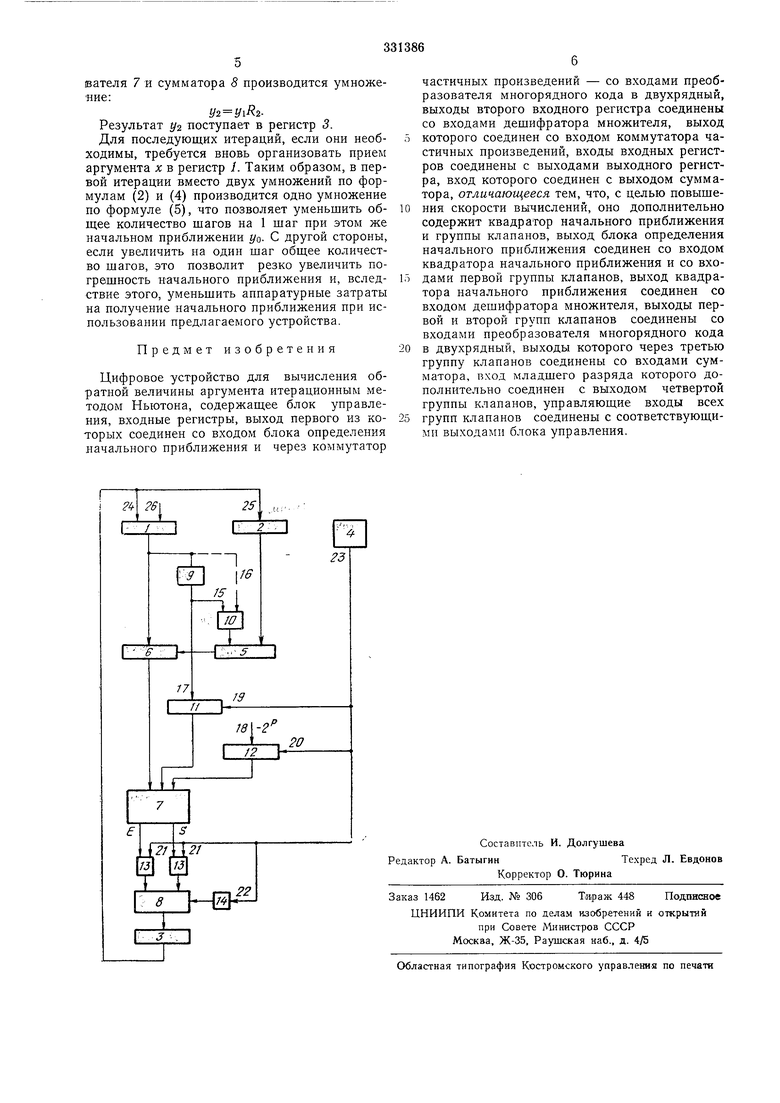

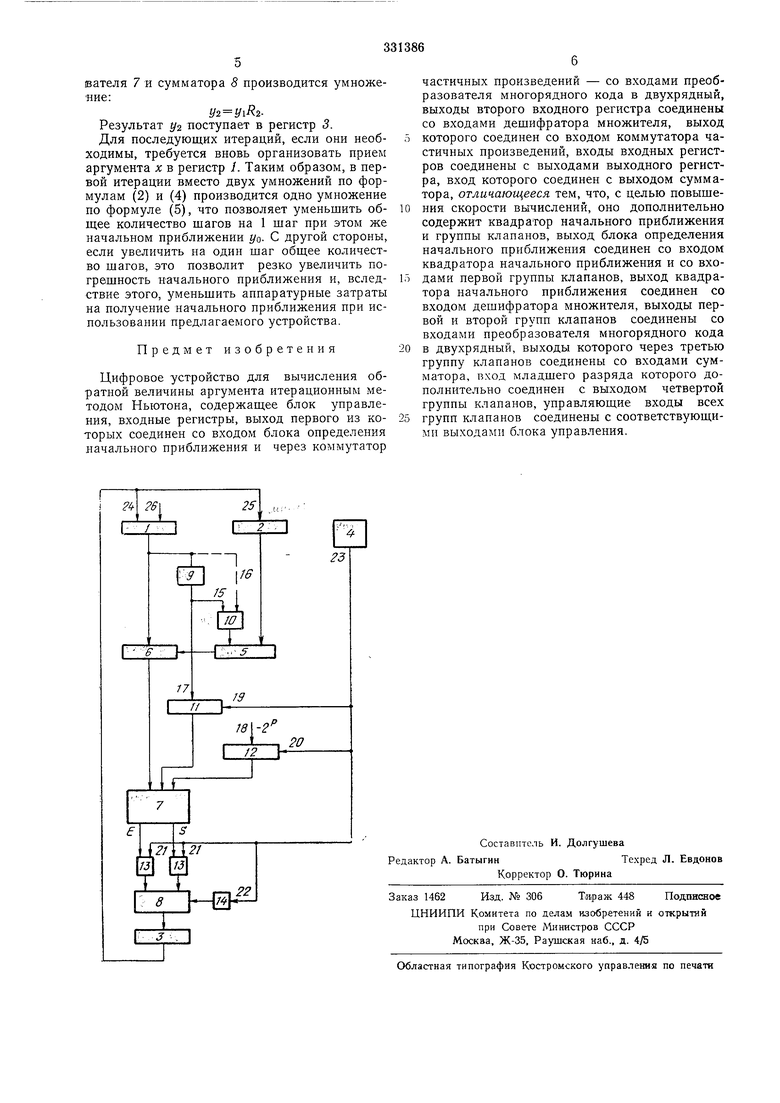

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит входные регистры / и 2, выходной регист ,3, блок 4 управления, дешифраторы 5 множителя, коммутаторы 6 частичных произведений, преобразователь 7 многорядного кода частичных произведений в двухрядный код, сумматор 5 для преобразования двухрядного кода в однорядный, блок 9 для определения начального приближения г/о к обратной величине у аргумента х, квадратор 10 начального приближения к обратной величине (для определения уо), клапаны 11 для подачи дополнительного кода отрицательного удвоенного начального приближения к обратной величине (для подачи величины 4-2г/о), клананы 12 для подачи донолнительного кода отрицательной единицы с весом младшего, р-го разряда выходного кода переносов преобразователя 7, клапаны 13 для инвертирования вцходов этого преобразователя, клапан 14 для подачи, единицы в младший, п-ый разряд сумматора 5:

Блок 9 установлен на выходе регистра 1. Квадратор 7(9.установлен между .выходами регистра . блока Р,. с одной .стороны, и входами дешифратора 5, с другой (т. е. вход квадратора соединен либо связью 15 с блоком 9, либо связью 16 с регистром /).

Клананы 11 и 12 установлены па входе преобразователя 7, информационные входы 17 клапанов 11 соединены с выходом блока 9. На информационных входах J8 клапанов 12 постоянно закоммутирован дополнительный код числа - 2 (где р - номер младшего разряда выходного кода переносов нреобразователя 7).

Входы 19, 20, 21, 22 управления клапанов //, 12, 13, 14 соединены с выходом 23 блока 4, служащим для подачи метки первой итерации. Входы 24 и 25 регистров 1 к 2 соединены с выходом регистра 3. Вход 26 регистра ,1 служит для .подачи аргумента хь

Устройство работает следующим образом. В первой итерации нормализованный аргумент л:(1 ) поступает в регистр /. Блок 9 вырабатывает начальное приближение. Уо(1 .) к обратной величине у по старшим разрядам аргумента х. Квадратор 10 вырабатывает величину УО. При помощи дешифраторов 5 и коммутаторов 6 в преобразователь 7 подается многорядный код произведения Кроме того, в указанный преобразователь через клапаны / поступает дополнительный код величины -2г/о, а через клапаны J2 - дополнительный код величины -2 , где р - номер младшего разряда выходного кода переносов преобразователя 7.

На выходе преобразователя 7 формируется двухрядный код, один ряд которого является кодом 5 суммы, а другой - кодом Е переносов. Сумма этих кодов определяется выражением:

5+ А;г/о2+ -2//о доп+ -2-/ |доп (5) где - дополнительный код величины -2уо,

-2- доп - дополнительный код величины -2-Р.

Для примера положим:

2уо яоп 4-2уо,(6)

-2-Р пои 4-2Р .(7)

Тогда 5+(д:г/о2+4-2t/o+4 2Pniod4

4-}-хуо -2уо-2-Р .(8)

Коды 5 и передаются через инвертируюш;ие клапаны 13 в сумматор 8 в обратном коде:

5 2-5-2 ,(9)

Е 2-Е-2 ,(10)

где п - номер младшего разряда кода S, р - номер младшего разряда кода Е. Кроме того, через клапан 14 в сумматор 8 поступает величина -}-2.

На выходе сумматора 8 формируется величина г/1 по формуле |С11)

г/1-5+ +2- .(11)

Подставив (9) и (10) в (И), получим У 2-S--2- -f -Р +2 «

4-(S+)(12)

Подставив (8) в (12), получим

г/1 4- (4+хуо -2уо-2 )-2

(1з;

(2-г/о х).

Выражение (13) соответствует выражению

(1)Полученная величина г/i поступает .в регистр 3. Л1ожно показать, что при взятии дополнений по формулам (6), (7) и обратных кодов по формулам (9), (10) старшие разряды слева от запятой можно отбросить и в старший разряд (с весом 2°) величины z/i всегда записывать «1, если . В 1-ом шаге 2-юй -итарации г/i из региспра 3 поступает в регистр 2. При помощи дешифратора 5 и коммутаторов 6 в преобразователь 7 поступает многорядный код произведения xyi. Кроме того, через клапаны 12 в преобразователь 7 поступает .

На выходе преобразователя 7 формируются коды S и , сумма которых будет равна

+ ,(14)

где 2-2-Р.(15)

Коды S и передаются через инвертирующие клапаны 13 в сумматор 8 в обратном коде: S 2-S-2- ,(9)

.(10)

Через клапан 14 в сумматор 8 поступает величина +2 .

На входе сумматора формируется величина

. 2-5-2 -f -р -2 4-(S+)--2 4-хг/1-2+2-- -2- 2-л;г/,.(16)

Величина R из сумматора 8 поступает в регистр 3.

вателя 7 и сумматора 8 производится умножение:

г/2 г/1 2Результат у2 поступает в регистр 5. Для последующих итераций, если они необходимы, требуется вновь организовать прием аргумента х в регистр /. Таким образом, в первой итерации вместо двух умножений по формулам (2) и (4) производится одно умножение по формуле (5), что позволяет уменьшить общее количество щагов на 1 щаг при этом же начальном приближении г/о. С другой стороны, если увеличить на один шаг общее количество шагов, это позволит резко увеличить погрешность начального приближения и, вследствие этого, уменьшить аппаратурные затраты на получение начального приближения при использовании предлагаемого устройства.

Предмет изобретения

Цифровое устройство для вычисления обратной величины аргумента итерационным методом Ньютона, содержащее блок управления, входные регистры, выход первого из которых соединен со входом блока определения начального приближения и через коммутатор

частичных произведений - со входами преобразователя многорядного кода в двухрядный, выходы второго входного регистра соединены со входами дешифратора множителя, выход которого соединен со входом коммутатора частичных произведений, входы входных регистров соединены с выходами выходного регистра, вход которого соединен с выходом сумматора, отличающееся тем, что, с целью повышения скорости вычислений, оно дополнительно содержит квадратор начального приближения и группы клапанов, выход блока определения начального приближения соединен со входом квадратора начального приближения и со входами первой группы клапанов, выход квадратора начального приближения соединен со входом дешифратора множителя, выходы первой и второй групп клапанов соединены со входами преобразователя многорядного кода

в двухрядный, выходы которого через третью группу клапанов соединены со входами сумматора, вход младшего разряда которого дополнительно соединен с выходом четвертой группы клапанов, управляющие входы всех

групп клапанов соединены с соответствующими выходами блока управления.

l

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU684551A1 |

| Устройство для вычисления обратной величины 48-разрядных чисел | 1983 |

|

SU1173412A1 |

| Конвейерное устройство для деления итерационного типа | 1987 |

|

SU1462296A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1405050A1 |

| Вычислительное устройство | 1981 |

|

SU993270A1 |

| Цифровое устройство для вычисления обратной величины | 1983 |

|

SU1171783A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

20

/2

Даты

1972-01-01—Публикация