17

ON О СЛ

00

VI

N

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе арифметических устройств цифровых вычислительных машин.

Целью изобретения является сокращение аппаратурных затрат.

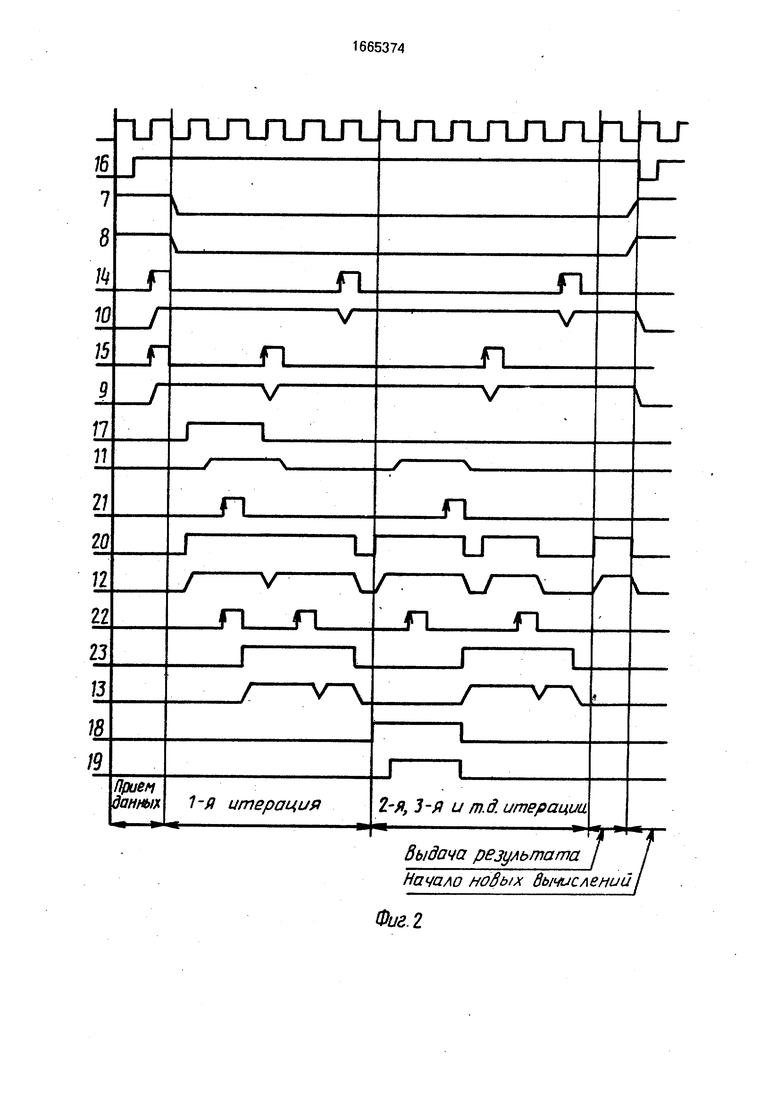

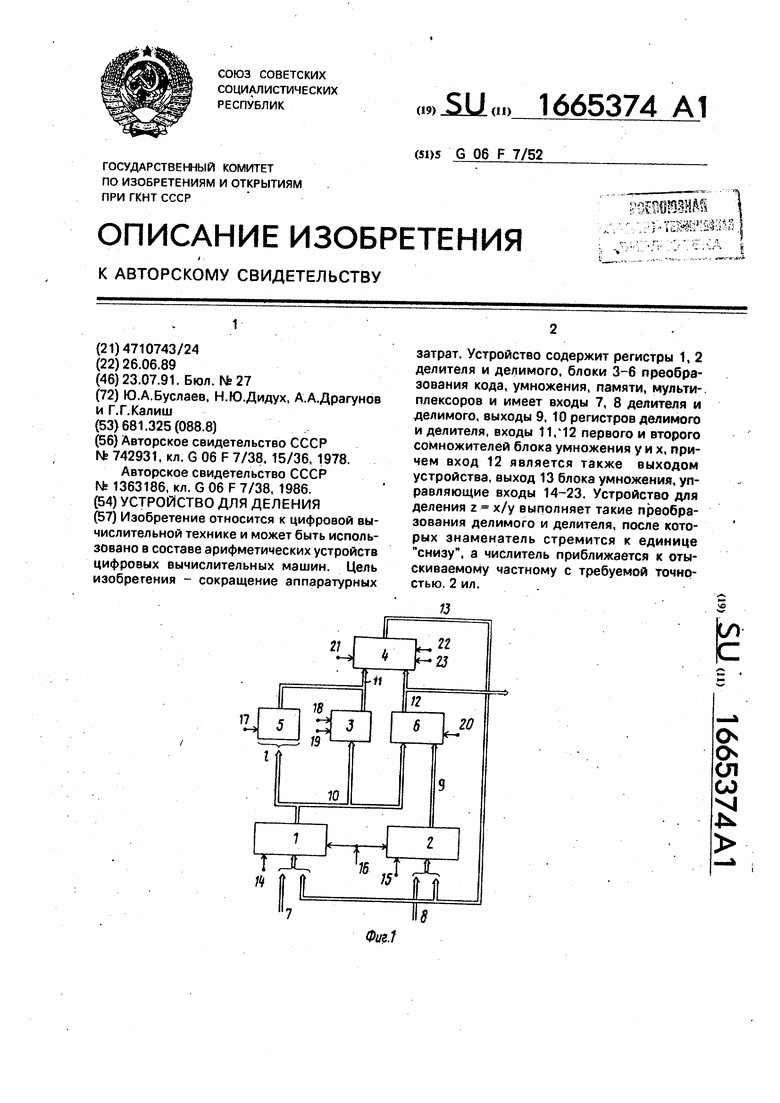

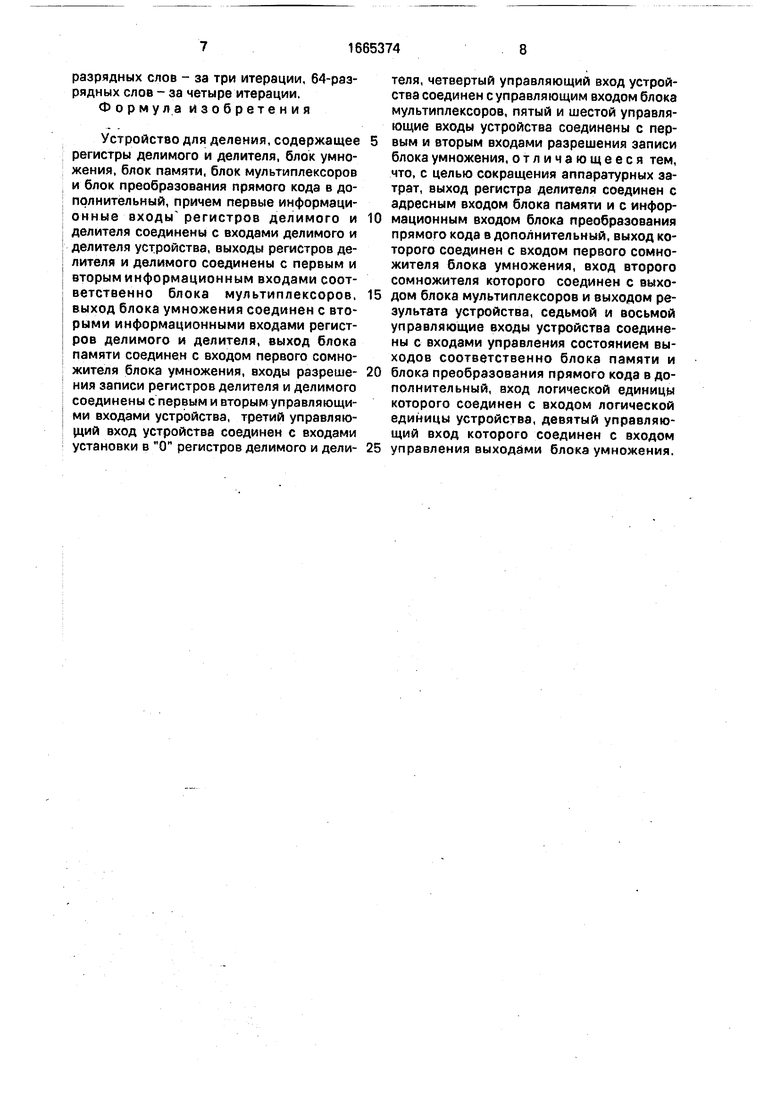

На фиг.1 показана сторуктурная схема устройства для деления; на фиг.2 - временная диаграмма работы устройства.

Устройство содержит регистр 1 делителя, регистр делимого, блок 3 преобразования прямого кода в дополнительный, блок 4 умножения, блок 5 памяти, блок 6 мультиплексоров, входы 7 и 8 делителя и делимого устройства, выходы 9 и 10 регистра делимого и регистра делителя, вход 11 первого сомножитепя блока умножения, вход 12 является входом второго сомножителя блока умножения и выходом устройства, выход 13 блока умножения, (входы-выходы 9-13 соответствуют шинам), первый, второй, третий управляющие входы 14-16 устройства, седьмой и восьмой управляющие входы 17 и 18 устройства, вход 19 логической единицы устройства, четвертый, девятый, пятый и шестой управляющие входы 20-23 устройства.

Регистр 1 делителя предназначен для

хранения исходного значения делителя,

получаемого из входной шины у устройства

и преобразованных значений делителя,

получаемых из блока 4 умножения.

Регистр 2 делимого предназначен для хранения исходного значения делимого, получаемого из входной шины х устройства, и преобразованных значений делимого, полученных из блока 4 умножения.

Блок 4 умножения предназначен для перемножения сомножителей xi и yi.

Блок 5 предназначен для хранения сомножителей, необходимых для проведения первой итерации алгоритма деления.

Блок 6 мультиплексоров предназначен для выбора одной из двух шин, поступающих от регистра 1 делителя или регистра 2 делимого на вход xi блока 4 умножения и на выходную информационную шину устройства.

Принцип действия устройства для деления z х/у основан на использовании того факта, что после выполнения каждого этапа вычислений над делителем в его старших разрядах имеется гарантированное число единиц, а каждое преобразование делимого позволяет увеличить точность отыскиваемого частного.

Устройство для деления выполняет вычисление частного за несколько итераций и работает следующим образом.

Перед началом работы регистр 1 и. регистр 2 устанавливаются в О сигналом, поступающим от шины управления устройства. Затем на входы делителя 7 и делимого

8 поступают соответственно исходные значения делителя и делимого от внешних информационных шин устройства. Исходное значение делителя у записывается на регистр 1 делителя сигналов с входа 14. Исходное значение делимого х записывается на регистр 2 делимого сигналом с входа 15. Затем устройство начинает работать по следующему алгоритму. Первая итерация,

Шаг 1: определение множителя ki, который рассчитывается заранее. Полученное значение записывается в блок 5 памяти, откуда считывается при выполнении первой итерации.

Множитель ki рассчитывается так, чтобы выполнялось условие

2° 2

-1

-п-1

0.

где р п - гарантированное число единиц,

которое будет получено в первой итерации;

х - полноразрядное слово.

В устройстве для деления считывание

множителя ki из блока 5 памяти происходит

следующим образом. Старшие разряды делителя из регистра 1 делителя по информационной шине 10 подаются на адресные входы блока 5 памяти. Информационное слово, считываемое из блока 5 памяти, поступает на информационную шину 11. Шина 11 имеет третье (высокоимпеданское) состояние, управление которым осуществляется сигналом по входу 17. Таким образом, сигнал с входа 17 открывает доступ считываемой из блока 5 информации на информационную шину 11. Информационые выходы блока 3 преобразования кода в это время находятся в третьем (высокоимпеданс- ном) состоянии, которое управляется сигналом, поступающим от управляющего входа 19 устройства. Информация, поступающая по информационной шине 11, записывается на входной внутренний регистр блока 3 умножения сигналом с входа 23.

Шаг 2: перемножение считанного из блока 5 памяти множителя ki, который уже находится во внутреннем регистре у блока 4 умножения, и делимого х:

ki х xi - z. Полученное произведение дает первое грубое приближение к требуемому результату и гарантирует верное значение нескольких старших разрядов.

Исходное значение делимого х по информационной шине 9 через блок 6

мультиплексоров передается на информационную шину 12. Блок 6 мультиплексоров управляется сигналом с входа 20. Информация, поступающая по информационной шине 12, записывается на входной внутренний регистр х блока 4 умножения сигналом по входу 22. Блок 4 умножения содержит матрицу умножения, которая производит эту операцию с содержимыми внутренних регистров х и у. Выходы блока 4 умножения имеют третье состояние, которое управляется сигналом с входа 21.

Полученное произведение xi поступает на информационную шину 13, по которой оно подается на вход регистра 2 делимого. Запись в регистр 2 осуществляется сигналом на входе 15.

Шаг 3: перемножение считанного из блока 5 памяти и находящегося уже во внутреннем регистре блока 4 множителя ki и делителя у:

ki y yi .

Полученное произведение yi приближает знаменатель к единице снизу и гарантирует требуемое количество двоичных единиц после знакового разряда:

ki у yi О.Л...1ьх х.-.х.

U, P.-I

п

В этом случае устройство работает следующим образом. Исходное значение делителя по информационной шине 10 через блок 6 мультиплексоров подается на информационную шину 12. Исходное значение делителя у записывается во входной внутренний регистр х блока 4 сигналом на входе 22. Полученное произведение yi по шине 13 поступает на вход регистра 1 делителя, запись в который осуществляется сигналом на входе 14.

Вторая итерация.

Шаг 1: вычисление коэффициента К2:

ка Дополнение yi до единицы + 1

ИЛО...Х

:х...х.

Данная операция осуществляется следующим образом: записанное в регистр 1 делителя значение yi no информационной шине 10 поступает на блок 3 преобразования кода. В этом блоке информация инвертируется, затем по сигналу на входе +1 t8 к младшему разряду полученного кода прибавляется единица. Вычисленное таким образом значение К2 по информационной шине 11 записывается на входной внутренний регистр у блока 4 умножения сигналом на входе 23.

Шаг 2: перемножение вычисленного множителя k2 и результата первой итерации xi:

k2 xi - Х2 .

Считанное из регистра 2 делимого значение xi по шине 9 через блок 6 мультиплек- соров поступает на шину 12. Код, 5 поступающий по шине 12, записывается сигналом на входе 22 на входной внутренний регистр блока 4 умножения. Полученное произведение хз выдается на шину 13 сигналом на входе 21. Данная информация, 10 считанная с шины 13, записывается на регистр 2 делимого сигналом на входе 15.

Шаг 3: перемножение вычисленного множителя k2 и yi:

yi k2 V2s0.11......1 хх...х .

IKiД-Р7. J

10n

Умножение yi на k2 позволяет увеличить в делителе количество двоичных единиц после знакового разряда минимум вдвое. Действительно, так как yi 1 ,то его мож- 0 но представить как yi 1 - |у I, тогда k2 1 + |у| и произведение равно

к2 yi(1+ 1у1)(1-1у1)1- lyl2. Таким образом, кажое подобное преобразование увеличивает количество послез- 5 наковых единиц в знаменателе в два раза. Значениеу1 считывается на информационную шину 10с регистра 1 делителя и через блок 6 мультиплексоров поступает на шину 12. Запись информации с шины 12 произво- 0 дится сигналом на входе 22 на входной внутренний регистр блока 4 умножения. Произведение считывается сигналом на входе 21 из блока 4 умножения на информационную шину 13 и записывается на регистр 5 1 делителя сигналом на входе 14.

Вычисления прекращаются, как только достигается требуемая точность частного, т.е. если yi становится равным

.IL.Jj 0пГ

Такое значение yi гарантирует точное значение частного либо возможную ошибку в младшем разряде вне зависимости от разрядности и значения чисел. 5 Третья и последующие итерации аналогичны второй.

Считывание результата производится следующим образом: частное , записан0 ное в регистре 2 делимого, поступает на информационную шину 9 через блок б мультиплексоров и передается на шину 12, которая соединена с информационной шиной устройства.

5 Приведенный алгоритм при условии использования блока 5 постоянной памяти емкостью 2048 шестнадцатиразрядных слов позволяет определить частное при делении: 16-разрядных слов - за две итерации, 32разрядных слов - за три итерации, 64-разрядных слов - за четыре итерации. Формула изобретения

Устройство для деления, содержащее регистры делимого и делителя, блок умножения, блок памяти, блок мультиплексоров и блок преобразования прямого кода в дополнительный, причем первые информационные входы регистров делимого и делителя соединены с входами делимого и делителя устройства, выходы регистров делителя и делимого соединены с первым и вторым информационным входами соответственно блока мультиплексоров, выход блока умножения соединен с вторыми информационными входами регистров делимого и делителя, выход блока памяти соединен с входом первого сомножителя блока умножения, входы разрешения записи регистров делителя и делимого соединены с первым и вторым управляющими входами устройства, третий управляющий вход устройства соединен с входами установки в О регистров делимого и делителя, четвертый управляющий вход устройства соединен с управляющим входом блока мультиплексоров, пятый и шестой управляющие входы устройства соединены с первым и вторым входами разрешения записи блока умножения, отличающееся тем, что, с целью сокращения аппаратурных затрат, выход регистра делителя соединен с адресным входом блока памяти и с информационным входом блока преобразования прямого кода в дополнительный, выход которого соединен с входом первого сомножителя блока умножения, вход второго сомножителя которого соединен с выходом блока мультиплексоров и выходом результата устройства, седьмой и восьмой управляющие входы устройства соединены с входами управления состоянием выходов соответственно блока памяти и

блока преобразования прямого кода в дополнительный, вход логической единицы которого соединен с входом логической единицы устройства, девятый управляющий вход которого соединен с входом

управления выходами блока умножения.

Начало новых Вычислений ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Арифметическое устройство | 1980 |

|

SU885993A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе арифметических устройств цифровых вычислительных машин. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит регистры 1, 2 делителя и делимого, блоки 3 - 6 преобразования кода, умножения, памяти, мультиплексоров и имеет входы 7, 8 делителя и делимого, выходы 9, 10 регистров делимого и делителя, входы 11, 12 первого и второго сомножителей блока умножения Y и X, причем вход 12 является также выходом устройства, выход 13 блока умножения, управляющие входы 14 - 23. Устройство для деления Z = X/Y выполняет такие преобразования делимого и делителя, после которых знаменатель стремится к единице "снизу", а числитель приближается к отыскиваемому частному с требуемой точностью. 2 ил.

Фиг. 2

| Устройство псевдоделения | 1978 |

|

SU742931A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-23—Публикация

1989-06-26—Подача