Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования число-импульсного кода в двоичный код.

Известны многоканальные интегрирующие (суммирующие) преобразователи последовательности импульсов (число-импульсного кода) в двоичный код, содержащие формирователи, арифметическое устройство (сумматор), запоминающее устройство и устройство управления.

Предложенное устройство отличается тем, что в нем выходы всех формирователей через схему «ИЛИ соединены с единичным входом приемного триггера, выходы которого соединены со входом сумматора и через схему «ИЛИ со входом формирователя импульсов обращения к запоминающему устройству, а единичный выход этого триггера через схемы «ИЛИ соединен также с единичными входами триггера блокировки генератора опроса формирователей и триггера признака операции, выход переноса старшего разряда сумматора через схемы «ИЛИ соединен с единичным входом приемного триггера и со входом старщего разряда регистра адреса запоминающего устройства.

шой частотой следования, а также упростить схему устройства за счет использования я-разрядного сумматора для получения 2празрядного двоичного кода по каждому входному каналу.

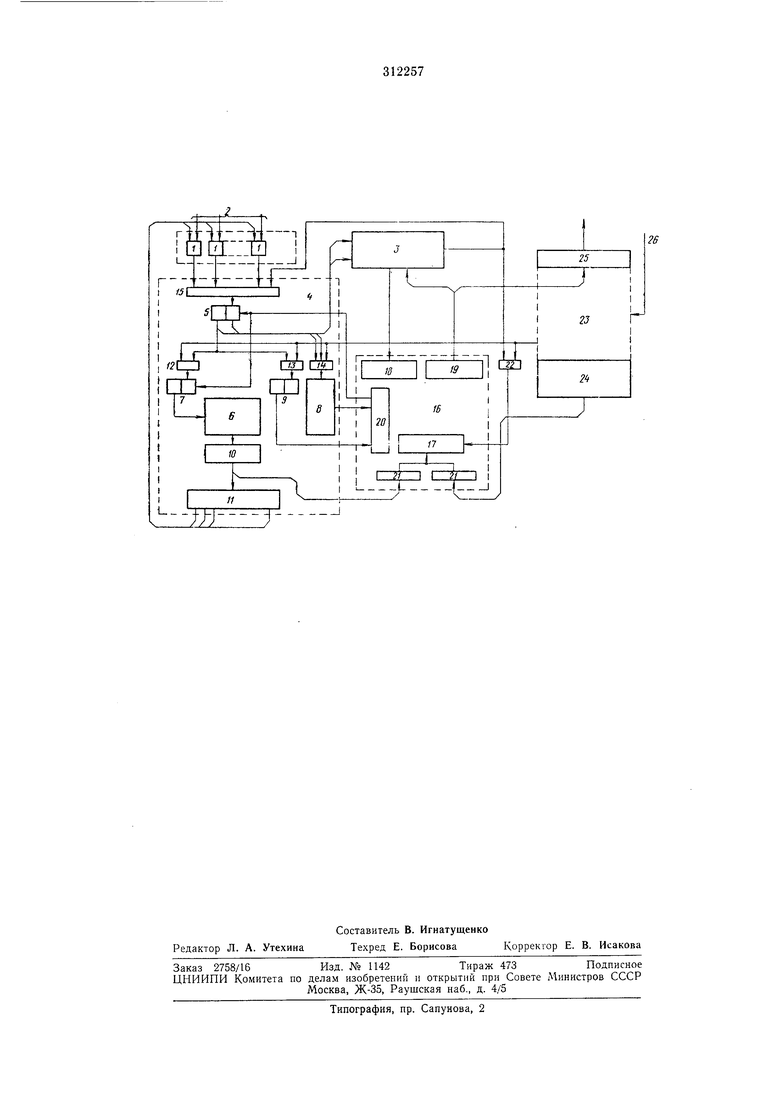

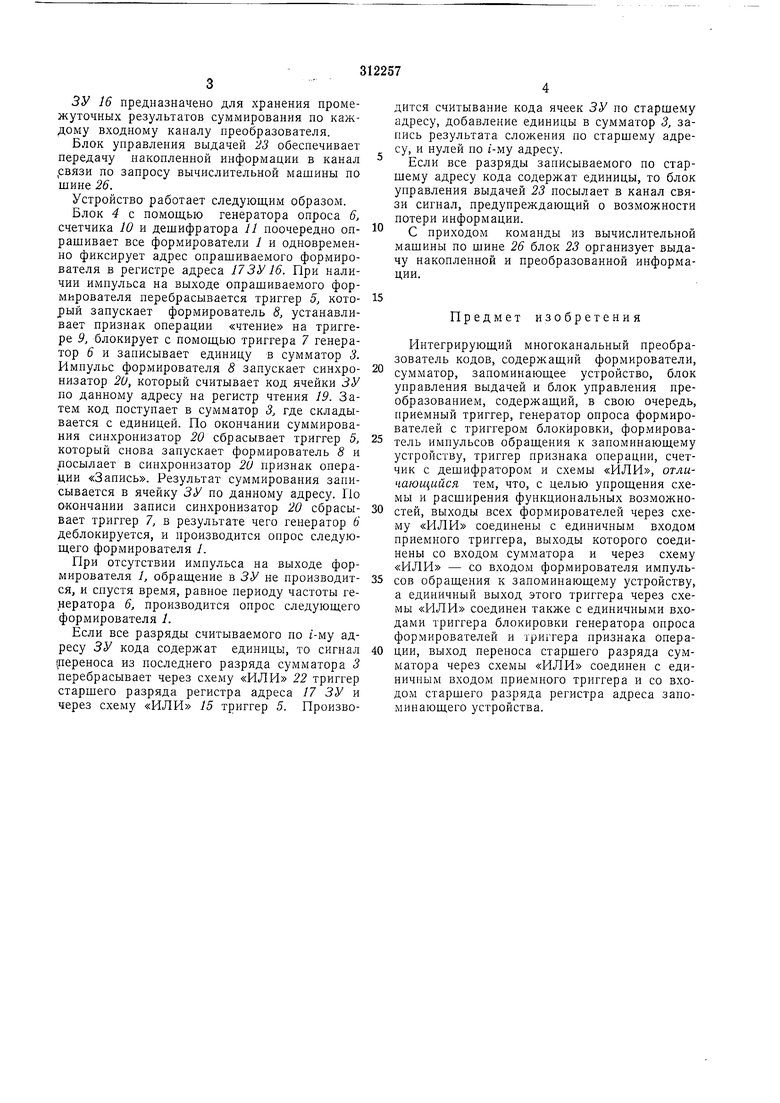

Схема устройства изображена на чертеже.

Устройство содержит формирователи 1, на

которые подаются сигналы датчиков по шина.м 2; сумматор 3; блок управления преобразованием 4, состоящий из приемного триггера 5, генератора опроса формирователей 6 с триггером блокировки 7, формирователя 8 импульсов обращения к запоминающему устройству, триггера признака операции 9, счетчика 10, дешифратора 11 и схем «ИЛИ 12-15; запоминающее устройство (ЗУ) 16, содержащее регистр адреса 17, регистр записи 18, регистр чтения 19, синхронизатор 20, клапаны 27; схему «ИЛИ 22; блок управления выдачей 23 с регистром-счетчиком кода адреса 24, выходным регистром 25 и щиной запроса 26.

Формирователи / осуществляют ирием входных сигналов от датчиков, формируют

одиночный импульс из каждого входного сигнала и однократно выдают его по сигналу опроса.

ЗУ 16 предназначено для хранения нромежуточных результатов суммирования по каждому входному каналу преобразователя.

Блок управления выдачей 23 обеспечивает передачу накопленной информации в канал рвязи по запросу вычислительной машины по шине 26.

Устройство работает следуюш,им образом.

Блок 4 с HOMOHJtbro генератора опроса 6, счетчика 10 и дешифратора П поочередно опрашивает все формирователи 1 и одновременно фиксирует адрес опрашиваемого формирователя в регистре адреса 17ЗУ 16. При наличии импульса на выходе опрашиваемого формирователя перебрасывается триггер 5 который запускает формирователь 8, устанавливает признак операции «чтение на триггере 9, блокирует с помощью триггера 7 генератор в и записывает единицу в сумматор 3. Импульс формирователя 8 запускает синхронизатор 2U, который считывает код ячейки ЗУ по данному адресу на регистр чтения 19. Затем код поступает в сумматор 3j где складывается с единицей. По окончании суммирования синхронизатор 20 сбрасывает триггер 5, который снова запускает формирователь 8 и посылает в синхронизатор 20 признак операции «Запись. Результат суммирования записывается в ячейку ЗУ по данному адресу. По окончании записи синхронизатор 20 сбрасывает триггер 7, в результате чего генератор 6 деблокируется, и производится опрос следующего формирователя 1.

При отсутствии импульса на выходе формирователя 1, обращение в ЗУ не производится, и спустя время, равное периоду частоты генератора 6, производится опрос следующего формирователя 1.

Если все разряды считываемого по i-му адресу ЗУ кода содержат единицы, то сигнал (переноса из последнего разряда сумматора 3 перебрасывает через схему «ИЛИ 22 триггер старшего разряда регистра адреса 17 ЗУ и через схему «ИЛИ 15 триггер 5. Производится считывание кода ячеек ЗУ по старшему адресу, добавление единицы в сумматор 3, запись результата сложения по старшему адресу, и нулей по г-му адресу.

Если все разряды записываемого по старшему адресу кода содержат единицы, то блок управления выдачей 23 посылает в канал связи сигнал, предупреждающий о возможности потери информации.

С приходом команды из вычислительной машины по шине 26 блок 23 организует выдачу накопленной и преобразованной информации.

Предмет изобретения

Интегрирующий многоканальный преобразователь кодов, содержащий формирователи,

сумматор, запоминающее устройство, блок управления выдачей и блок управления преобразованием, содержащий, в свою очередь, приемный триггер, генератор опроса формирователей с триггером блокировки, фор.мирователь импульсов обращения к запоминающему устройству, триггер признака операции, счетчик с дешифратором и схемы «ИЛИ, отличающийся тем, что, с целью упрощения схемы и расширения функциональных возможностей, выходы всех формирователей через схему «ИЛИ соединены с единичным входом приемного триггера, выходы которого соединены со входом сумматора и через схему «ИЛИ - со входом формирователя импульсов обращения к запоминающему устройству, а единичный выход этого триггера через схемы «ИЛИ соединен также с единичными входами триггера блокировки генератора опроса формирователей и триггера признака операции, выход переноса старшего разряда сумматора через схемы «ИЛИ соединен с единичным входом приемного триггера и со входом старшего разряда регистра адреса запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для моделирования экстремальных путей на графе | 1983 |

|

SU1129617A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР С ПАРАЛЛЕЛЬНЫМ СДВИГОМ | 1969 |

|

SU250544A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Устройство для определения времени фибринолизиса | 1985 |

|

SU1323566A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

Даты

1971-01-01—Публикация