Изобретение относится к аналого-цифровым преобразователям управляющих вычислительных машин и к цифровым электроизмерительным приборам.

Известны аналого-цифровые преобразователи, содержащие схемы сравнения, цифроаналоговый преобразователь, ключи, аналоговые запоминающие схемы, оперативный запоминающий блок, блок анализа результатов сравнения и регистр ошибок.

Недостатком известных преобразователей является, то, что повышение точности преобразования ведет к снижению достоверности результата преобразования.

Целью изобретения является повышение точности преобразования при сохранении достоверности результата.

Эта цель достигается тем, что предложенный аналого-цифровой преобразователь содержит арифметический блок и дополнительные схему сравнения и цифро-аналоговый преобразователь, выход которого соединен через ключ с .одним из входов дополнительной схемы сравнения, его управляющий вход подключен к выходу дополнительной схемы сравнения, а цифровой выход соединен со входом оперативного запоминающего блока. Входы арифметического блока подключены к выходу основного цифро-аналогового преобразователя и оперативного запоминающего

блока. Входы блока анализа результатов сравнения соединены с выходами основной, и дополнительной схем сравнения, а выход - с регистром ошибок.

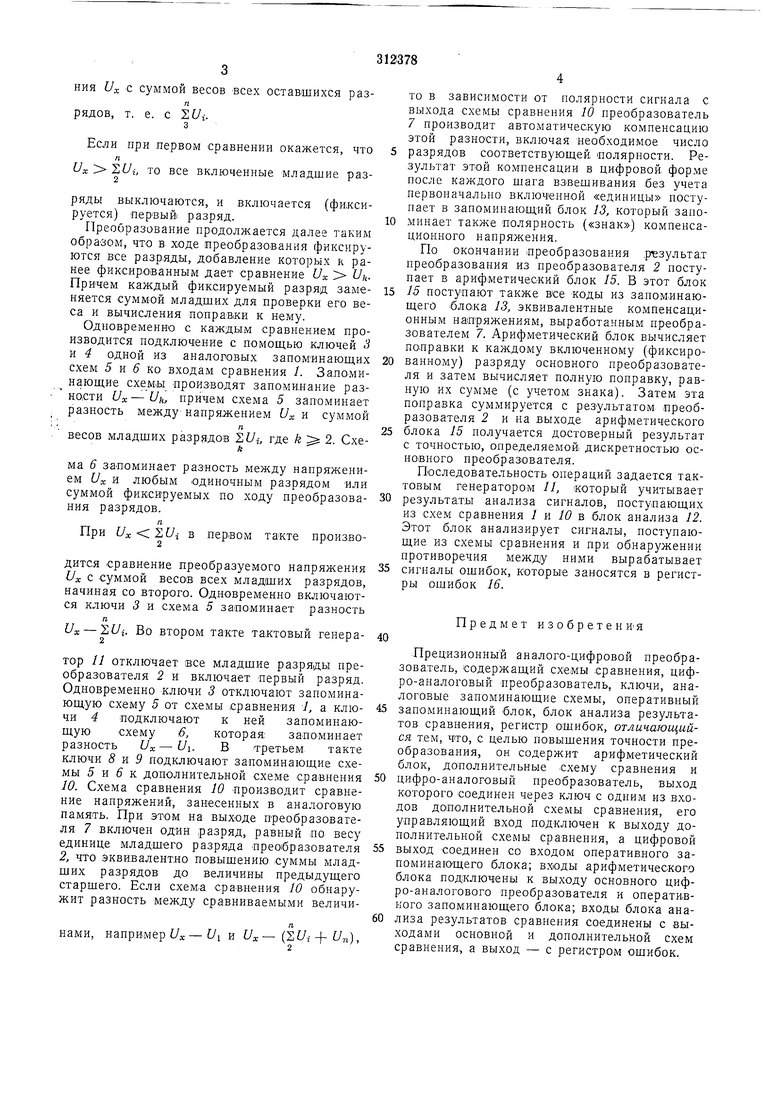

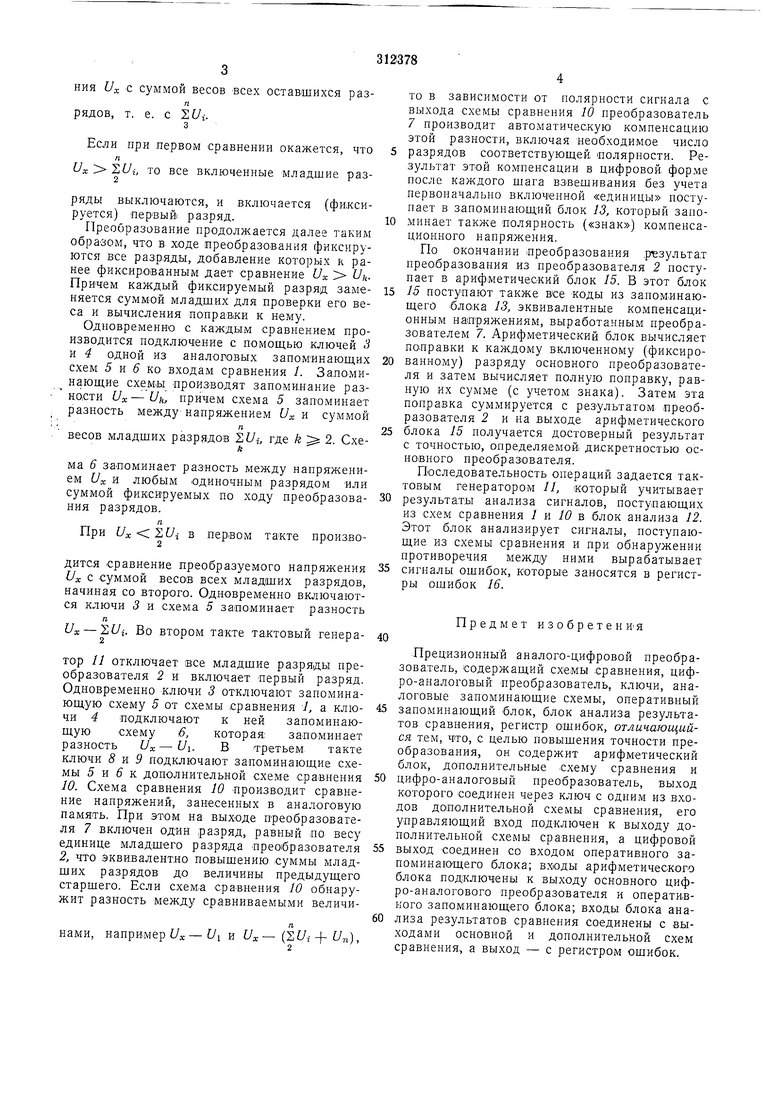

На чертеже дана схема преобразователя,. Он содержит основную схему сравнения /, основной цифро-аналоговый преобразователь 2, работающий по принципу взвешивания,

ключи 3, 4, аналоговые запоминающие схемы 5, 6, дополнительный цифро-аналоговый преобразователь 7, ключи 8, 9, дополнительную схему сравнения 10, тактовый генератор 11, блок 12 анализа результатов сравнения и

выработки сигналов ошибок, оперативный запоминающий блок 13, блок 14 приема команд из ЦВМ, арифметический блок 15 и регистр ошибок 16.

Преобразователь работает следующ1 м образом.

Взвешивание начинается с включения всех разрядов основного преобразователя 2, кроме первого. Схема сравнения 1 сравнивает напряжение Ux с суммой весов всех разрядов,

л

начиная со второго, т. е. с Е(/г.

2 п

ния Vx с суммой весов всех оставшихся разрядов, т. е. с 26/1.

Если при первом сравнении окажется, что

UK Sf/i, то все включенные младшие разряды выключаются, и включается (фиксируется) первый разряд.

Преобразование продолжается далее таким образом, что в ходе преобразования фиксируются все разряды, добавление которых к ранее фиксированным дает сравнение Их UhПричем каждый фиксируемый разряд заменяется суммой младших для проверки его веса и вычисления поправки к нему.

Одновременно с каждым сравнением производится подключение с помош,ью ключей : и 4 одной из аналоговых запоминающих схем 5 и 5 ко входам сравнения /. Запоминающие схемы производят запоминание разности Ux-Uh, причем схема 5 запоминает разность между напряжением U и суммой

весов младших разрядов 2f/i, где и 2. Схема 6 запоминает разность между напряжением С/х и любым одиночным разрядом или суммой фиксируемых по ходу преобразования разрядов. II

При Ux-.ZUi в первом такте производится сравнение преобразуемого напряжения Ux с суммой весов всех младших разрядов, начиная со второго. Одновременно включаются ключи 3 и схема 5 запоминает разность

Ux - Во втором такте тактовый генератор // отключает все младшие разряды преобразователя 2 и включает первый разряд. Одновременно ключи 3 отключают запоминающую схему 5 от схемы сравнения 1, а ключи 4 подключают к ней запоминающую схему 6, которая. запоминает разность Ux - Ui. В третьем такте ключи S и 9 подключают запоминающие схемы 5 и 5 к дополнительной схеме сравнения 10. Схема сравнения 10 производит сравнение напряжений, занесенных в аналоговую память. При этом на выходе преобразователя 7 включен один разряд, равный по весу единице младшего разряда преобразователя 2, что эквивалентно повышению суммы младших разрядов до величины предыдущего старшего. Если схема сравнения 10 обнаружит разность между сравниваемыми величинами, например i/a;- и и Ux- (Sf/i-f- n),

то в зависимости от полярности сигнала с выхода схемы сравнения 10 преобразователь 7 производит автоматическую компенсацию этой разности, включая необходимое число

разрядов соответствующей полярности. Результат этой компенсации в цифровой фор.ме после каждого шага взвешивания без учета первоначально включенной «единицы поступает в запоминающий блок 13, который запоминает также полярность («знак) компенсационного напряжения.

По окончании преобразования .результат преобразования из преобразователя 2 поступает в арифметический блок 15. В этот блок

15 поступают также вСе коды из запоминающего блока 13, эквивалентные компенсационным напряжениям, выработанным преобразователем 7. Арифметический блок вычисляет поправки к каждому включенному (фиксированному) разряду основного преобразователя и затем вычисляет полную поправку, равную их сумме (с учетом знака). Затем эта поправка суммируется с результатом преобразователя 2 и на выходе арифметического

блока 15 получается достоверный результат с точностью, определяемой дискретностью основного преобразователя.

Последовательность операций задается тактовым генератором 11, который учитывает

результаты анализа сигналов, поступающих из схем сравнения 1 и 10 в блок анализа 12. Этот блок анализирует сигналы, поступающие из схемы сравнения и при обнаружении противоречия между ними вырабатывает

сигналы ошибок, которые заносятся в регистры ошибок 16.

Предмет изобретен и-я

Прецизионный аналого-цифровой преобразователь, содержащий схемы сравнения, цифро-аналоговый преобразователь, ключи, аналоговые запоминающие схемы, оперативный

запоминающий блок, блок анализа результатов сравнения, регистр ошибок, отличающийся тем, что, с целью повышения точности преобразования, он содержит арифметический блок, дополнительные схему сравнения и

цифро-аналоговый преобразователь, выход которого соединен через ключ с одним из входов дополнительной схемы сравнения, его управляющий вход подключен к выходу дополнительной схемы сравнения, а цифровой

выход соединен со входом оперативного запоминающего блока; входы арифметического блока подключены к выходу основного цифро-аналогового преобразователя и оперативного запоминающего блока; входы блока анализа результатов сравнения соединены с выходами основной и дополнительной схем сравнения, а выход - с регистром ошибок.

Katmandu

из ЦВМ Результат

прео5разодс1ни}1 Код ошибки

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU936420A2 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Грозопеленгатор-дальномер | 1984 |

|

SU1201790A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU383206A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1978 |

|

SU744970A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1991 |

|

SU1800617A1 |

Даты

1971-01-01—Публикация