(5) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с самоконтролем | 1978 |

|

SU744970A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| ПРЕЦИЗИОННЬШ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU312378A1 |

| Способ преобразования кода угла в напряжения,пропорциональные синусу и косинусу угла, и устройство для его осуществления | 1985 |

|

SU1345346A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU949800A1 |

| Устройство для исправления двух ошибок в кодовой комбинации с самоконтролем в системах контроля и передачи информации | 1984 |

|

SU1239721A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

1

Изобретение относится к аналого-цифровым преобразователям управляющих вычислительных устройств и может быть использовано в системах автоматического управления, в которых требуется обеспечение: высокой достоверности преобразования информации. .

По основному авт. св. № из вестен аналого-цифровой преобразователь с самоконтролем, в котором обеспечивается автоматическап коррекция одиночных неисправностей, содержащий преобразователь цифра-аналог, вход которого соединен с первым выходом тактового генератора, второй выход которого соединен с регистром готовности, третий выход с первым входом регистра ошибок, четвертый выход соединен с первыми входами первого, второго, третьего и четвертого ключей, первый вход с выходом блока ввода команд, выход перовго ключа соединен с вхоДОМ первого запоминающего блокл , выход которого соединен со входной шиной, а выход с первымвходом блока сравнения, выход второго ключа соединен со входом второго запоминающего блока, выход которого соединен со вторым входом четвертого ключа, выход которого соединен со вторым входом блока сравнения, а его выход соединен со входом регистра ошибок, выход преобразователя цифра-аналог соединен со вторыми входами первого, второго ключей, с третьим входом четвертого ключа, второй выход с первым входом выходного регистра, при этом выход блока сравнения соединен с первым входом тактового генератора, второй вход которого соединен с выходом регистра ошибок, а пятый выход соединен со вторым входом выходного регистрах Автоматическая коррекция одиночных неисправностей обеспечивается за счет компенсации

веса неисправного разряда с помощью включения всех последующих за неисправным разрядов цифро-аналогобого преобразователя СП.

Недостатком преобразователя является низкая точность автоматической коррекции при множественных неисправностях.

Цель изобретения - повышение точности при автоматической коррекции неисправностей.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь с самоконтролем, содержа щий преобразователь цифра-аналог, первый выход которого через последовательно соединенные первый ключ, первый запоминающий блок и третий ключ подключен к первому входу блока сравнения и через последовательно соединенные второй ключ, второй запоминающий блок и четвертый ключ подключен ко второму входу блока сранения, выход которого подклйчен к первому входу тактового генератора и первому входу регистра ошибок, второй вход которого соединен с первым выходом тактового генератора, а выход подключен ко второму входу тактового генератора, третий вход которого соединен с выходом блока ввода команд, а второй, третий и четвертый выходы.подключены соответств нно к регистру готовности, к первому входу выходного регистра и ко входу преобразователя цифра-аналог при этом пятый выход подключен ко вторым входам с первого по четвертый ключей, введены суммирующий блок, пятый ключ, блок коррекции, причем выход преобразователя цифра-аналог соединен со вторым входом выходного регистра через суммирующий блок, второй вход которого соединен с выходом блока коррекции, третий вход - с выходом пятого ключа, четвертый - с выходом выходного регистра, а пятый вход t шестым выходом тактового генератора, седьмой выход которого соединен с первым входом блока коррек ции, восьмой выход- с первым входом пятого ключа, второй вход которого соединен с третьим выходом регистра ошибок, а выход блока сравнения соединен со вторым входом блока коррекции.

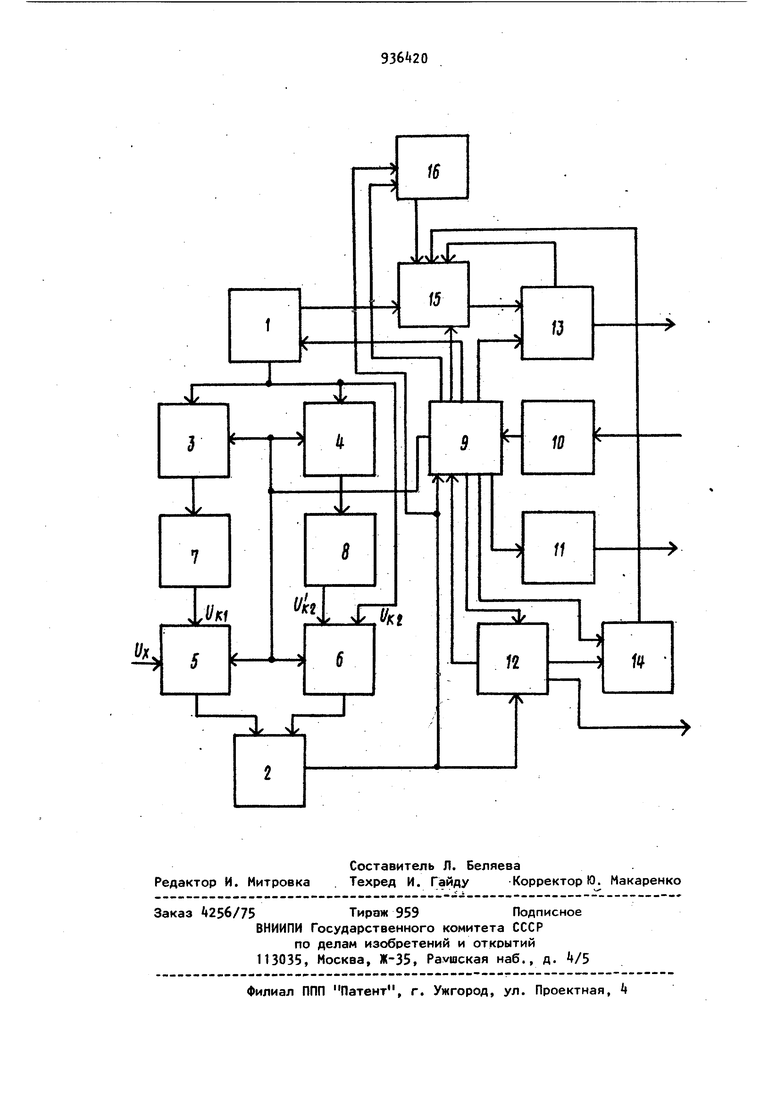

На чертеже представлена структурная схема аналого-цифрового преобразователя с самоконтролем.

Преобразователь содержит преобразователь цифра-аналог 1, блок 2 сравнения, с первого по четвертый ключи 3-6, запоминающие блоки 7 и 8,

тактовый генератор 9, блок ввода команд 10, регистр готовности 11, ре гистр ошибок 12, выходной регистр 73, пятый ключ 1, суммирующий блок 15, блок коррекции 16.

Устройство работает следующим образом.

В начале процесса преобразования через ключи 3 выход преобразователя цифра-аналог 1 подключен к запоминаS ющему блоку 7. В первом такте включается старший разряд преобразователя цифра-аналог 1 и на блок 2 сравчерез ключи б и 5 подаются соответственно аналоговая величина с выхода преобразователя цифра-аналог 1, соответствующая весу включенного разряда () и ранее зафиксированная величина с выхода аналогового запоминающего блока 7 .(Ц() (в начале преобразования - нулевая ). В случае исправного включения разряда блок 2 сравнения сработает и тактовый генератор 9, следующим тактом разрешает выдачу на аналоговый запоминающий блок 7.аналоговой величины с преобразователя цифра-аналог 1 и од новременно подключает через ключи 5 и 6 к блоку 2 сравнения измеряемое напряжение DX и выход преобразователя цифра-аналог 1. Таким образом, в этом случае блок 2 сравнения в зависимости от его состояния через логические ячейки тактового генератора Э оставляет включенными или отключает соответствующий разряд преобразователя цифра-аналог 1,. в результате чего происходит формирование соответствующего разряда. В том случае, если не происходит включения разряда преобразователя цифра-аналог 1, сравниваемые напряжения с выходов преобразователя цифра-аналог 1 и аналогового запоминающего блока 7 равны (Ц( U ), блок 2 сравнения записывает единицу в соответствующем разряде регистра ошибок 12, управляемого тактовым генератором 9 и через логические ячейки тактового генератора 9 включает все последующие разряды преобразователя цифра-аналог 1 (в этом случае вес всех включенных разрядов должен с точностью до единицы младшего разряда соответствовать весу неисправного разряда) и через 4 выход преобразователя цифра-аналог 1 подключается ко входу аналогового запоминающего блока 8. Следующим тактом ко входам блока 2 ср нения через ключи 5 подается измеряемое напряжение, а через ключи 6 выход аналогового запоминающего блока 8 (). В зависимости от со стояния блока 2 сравнения происходит формирование в выходном регистре 13 соответствующего разряда. При формировании нуля отключа ются все разряды преобразователя цифра-аналог 1, включенные для ком пенсации неисправного, происходит возврат к предыдущему уровню, кото рый запоминается в аналоговом запоминающем блоке 8. При формирова нии единицы происходит сохранение с(оомиоованного уровня в аналоговом запоминающем блоке В при отклю чении разрядов преобразователя циф ра-аналог 1, включенных для компен сации неисправного. Далее процесс преобразования пов торяется, формируются все последующие разряды, причем при формировании разрядов участвуют и запомненный уровень, соответствующий весу неисправного разряда преобразователя цифра-аналог 1. Разрешение подключения этого уровня осуществля-ется с логических ячеек тактового генератора Э на который поступает сигнал с регистра ошибок 12. После окончания всего цикла преобразования производится определение истинной величины результатов. Если по каким-либо причинам вышло из строя несколько разрядов преобразователя цифра-аналог 1 (что определяется в каждом единичном включении и фиксируется в регистре ош бок 12) , то результат преобразования оказывается завышенным на вели1 пчину С 2. К, где К определяет место разряда в регистре ошибок 12, а п определяет число неисправных разря,дов прео бразователя цифра-аналог 1, причем принадлежит области, значений Р, в которой начинается формирование результата с участием неисп равных разрядов, при этом указанная сумма определяется только с учетом разрядов, включаемых для компенсации. Из этого следует, что из 20 результатов необходимо вычитать число, определяемое указанной обла--стью и регистром ошибок 12 не с первого неисправного разряда, а со второго. Вычитание производится на суммирующем блоке 15 по управляющим импульсам тактового генератора 9 (суммирование с обратным или дополнительным кодом с учетом единицы циклического пеоеноса1. Накапливающая сумл ti-l ма частных вычитаний . К. |опреде - . ляется несколькими вычитаниями с последовательным маскированием (с помощью ключей It, управляемых такто ,вым генератором 9 каждого следующего неисправного разряда. Например,в регистре ошибок зафиксирован код 010110. Результат начинает формиро ваться с первого разряда (1), . следовательно в первом цикле вычитается код 000110. во втором цикле код 000010. Однако на этом цикл определения правильного результата не заканчивается, поскольку в каждом цикле коооекции неисправности поеобоазователя цифра- аналог 1 включаются все последующие разряды, то в результате накапливается ошибка, определяемая весом младшего разряда, причем величина этой ошибки определяется именно числом оставленных при коррекцим величин, т.е. если в результате коррекции определяется перекомпенсация, то вес младшего разряда не включается в накапливающуюся ошибку. Следовательно, из полученного резуль тата необходимо еще вычесть число md, где m - число разрядов, оставленных включенными при коррекциях, djj-Bec младшего разряда. Эта величина формируется в блоке коррекции 1б, который, например, может состоять из счетчика, управляемого блоком сравнения 2. Таким образом, производится определение, истинного результата . Однако в ряде случаев возможно следующее : определяется результат с учетом всех циклов вычитаний, а перекомпенсации в младшем разряде не происходит, т.е. результат еще не соответствует действительному. В этом случае производятся следующие циклы оаботы преобоазователя совместно с включением уже запомненной в аналоговом запоминающем локе 8 аналоговой 79 величиной. Затем производится новый цикл вычитаний и результат суммирует ся на суммирующем блоке 15 с предварительно полученным результатом, хранящимся в выходном регистре 13. После определения результата с ре гистра готовности 11 выдается сигнал готовности и по сигналу с блока 10 ввола команд производится выдача кода с выходного регистра 13с одновременной выдачей кода ошибок с регистра ошибок 12. При отказах младшего разряда может производиться снижение точности результата, если это допускается режимом работы. Таким образом, предлагаемый преобразователь с самоконтролем позволяет автоматизировать процесс автокоррекции, что повышает надежность работы преобразователя. Зто позволяет исключить ремонтные затраты при отказе нескольких разрядов и связанные с этим затраты на простой оборудования, что повышает эффектив ность работы преобразователя. 8 Формула изобретения Аналого-цифровой преобразователь с самоконтролем по авт. св. . ff , отличающийся тем, что, с целью повышения точности при автоматической коррекции неисправностей, введенк суммирующий блок, блок коррекции и пятый ключ, причем выход преобразователя цифрааналог соединен с вторым входом выходного регистра через суммирующий блок, второй вход которого соединен с выходом блока коррекции, третий вход - с выходом пятого ключа, четвертый - с рыходом выходного регистра, пятый вход - с шестым выходом тактового генератора,седьмой выход которого соединен с первым входом блока коррекции, восьмой выход - с первым входом пятого ключа, второй вход которого соединен с третьим выходом регистра ошибок, а выход блока сравнения соединен с вторым входом блока коррекции. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № , кл. Н 03 К 13/17, 06.01.78.

Авторы

Даты

1982-06-15—Публикация

1980-10-13—Подача