Изобретение относится к области передачи данных.

Известны устройства тактовой синхронизацни с пропорциональным регулированием, содержащие задающий генератор, делитель частоты, узелуправления коэффициентом деления, фазовый дискриминатор, формирователь фронтов. В известных устройствах используются сложные узлы усреднения.

С целью упрощения аппаратуры при сохранении точности синхронизации, в предлагаемом устройстве делитель частоты выполнен с дополнительным числом К. разрядов. Выход /С-го разряда делителя частоты подключен ко входу фазового дискриминатора.

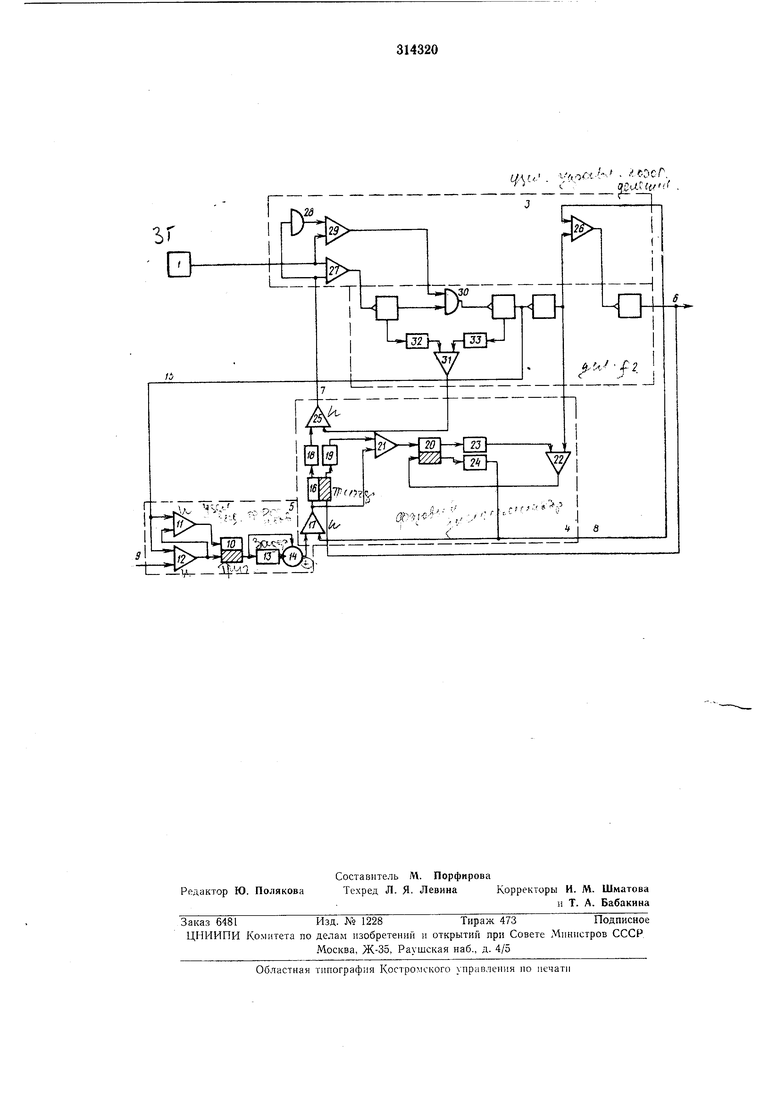

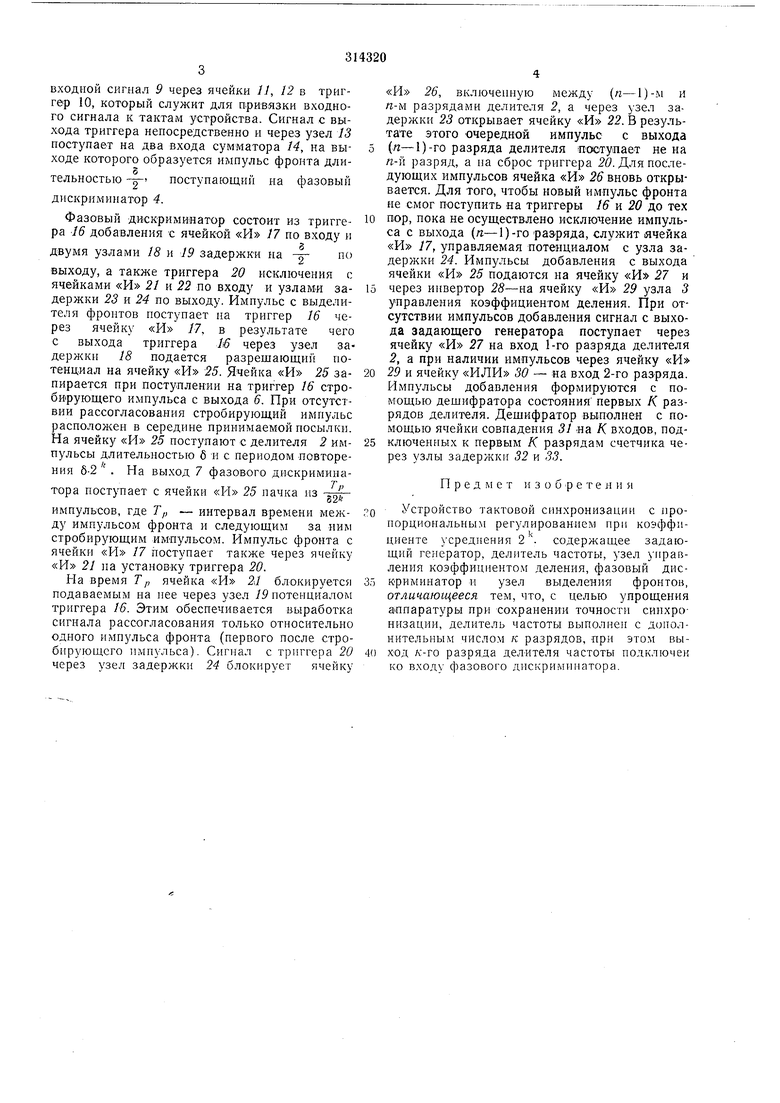

На чертеже изображена схема предлагаемого устройства.

Устройство содержит задающий генератор /, делитель частоты 2, узел 5 управления коэффициентом деления, фазовый дискриминатор 4, узел 5 выделения фронтов.

Импульсы с задающего генератора / с периодом повторения б поступает на делитель 2 с коэффициентом деления 2 . На выходе 6 устройства вырабатывается последовательность стробирующих импульсов с периодом Т (Т- длительность элементарной посылки принимаемого сигнала), синфазная с фронтами принимаемого сигнала. Б узле 5 выделения фронтов выделяются передние и задние фронты посылок принимаемого сигнала и подаются на фазовый дискриминатор 4. В дискриминаторе сравнивается момент прихода импульса фронта ti с узла о и момент (z прихода импульса с выхода 6. На выходе 7 дискриминатора 4

//

выраоатывается - - -

пачка из г

имS . 2

пульсов, которая поступает на узел 3 управления коэффициентом деления. При этом происходит добавление г импульсов на вход делителя 2. Кроме того, с дискриминатора 4 на узел 3 по цепи 8 поступает с приходом каждого фронта сигнал, вызывающий как бы исключение импульсов иа входе делителя 2. Таким образом, в режиме синхронизма на выходе фазового дискриминатора вырабатывается 2 импульсов добавления, сдвигающих стробирующий импульс вперед на время . На эту же величину происходит сдвиг вперед стробирующего импульса вследствие исключения одного импульса на входе (п-1)-го разряда делителя.

Сигнал 9с выхода радиоприемника поступает в узел 5, состоящий из триггера /О с раз5дельным входом 11 двумя ячейками совпадеПИЯ «и // и 12, узла /3 задержки на -,-,входной сигнал 9 через ячейки 11, 12 в триггер 10, который служит для привязки входного сигнала к тактам устройства. Сигнал с выхода триггера неносредственно и через узел 13 поступает на два входа сумматора 4, на выходе которого образуется импульс фронта длительностью -g- поступающий на фазовый дискриминатор 4.

Фазовый дискриминатор состоит из триггера 16 добавления с ячейкой «И 17 но входу и

двумя узлами 18 и 19 задержки на -|- по

выходу, а также триггера 20 исключения с ячейками «И 21 и 22 по входу и узлам-и задержки 23 и 24 по выходу. Импульс с выделителя фронтов поступает на триггер 16 через ячейку «И /7, в результате чего с выхода триггера М через узел задержки 18 подается разрешающий потенциал на ячейку «И 25. Ячейка «И 25 запирается нри поступлении на триггер 16 стробирующего импульса с выхода 6. При отсутствии рассогласования стробирующий импульс расположен в середине принимаемой посылки. На ячейку «И 25 поступают с делителя 2 импульсы длительностью б и с периодом повторения 6-2 . На выход 7 фазового дискримингь

Т

тора поступает с ячейки «И 25 пачка из -ggfимпульсов, где Г/, - интервал времени между импульсом фронта и следующим за ним стрОбирующим импульсом. Импульс фронта с ячейки «И 17 поступает также через ячейку «И 21 на установку триггера 20.

На время Т/, ячейка «И 2/ блокируется подаваемым на нее через узел 19 потенциалом триггера 16. Этим обеспечивается выработка сигнала рассогласования только относительно одного импульса фронта (первого после стробирующсго импульса). Сигнал с триггера 20 через узел задержки 24 блокирует ячейку

«И 26, включенную между (п-1)-м и п-м разрядами делителя 2, а через узел задержки 23 открывает ячейку «И 22. В результате этого очередной импульс с выхода

(л-1)-го разряда делителя иоступает не на л-й разряд, а на сброс триггера 20. Для последующих импульсов ячейка «И 26 вновь открывается. Для того, чтобы новый импульс фронта не смог поступить на триггеры 16 и 20 до тех

пор, пока не осуществлено исключение импульса с выхода (rt-1)-го-разряда, служит ячейка «И 17, управляемая потенциалом с узла задержки 24. Импульсы добавления с выхода ячейки «И 25 подаются на ячейку «И 27 и

через инвертор 28-на ячейку «И 29 узла 5 управления коэффициентом деления. При отсутствии импульсов добавления сигнал с выхода задающего генератора поступает через ячейку «И 27 на вход 1-го разряда делителя 2, а при наличии имлульсов через ячейку «И

29 и ячейку «ИЛИ 30 - на вход 2-го разряда. Импульсы добавления формируются с помощью дешифратора состояния первых К разрядов делителя. Дешифратор выполнен с помощью ячейки совпадения 31 на К входов, подключенных к первым К разрядам счетчика через узлы задержки 32 и 33.

Предмет и з о б р е т е л и я

Устройство тактовой синхронизации с пропорциональным регулированием при коэффициенте усреднения 2 содержащее задающий генератор, делитель частоты, узел управления коэффициентом деления, фазовый дисКриминатор и узел выделения фронтов, отличающееся тем, что, с целью упрощения аппаратуры при сохранении точности синхронизации, делитель частоты выполнен с дополнительным числом /V разрядов, при этом выХОд к-го разряда делителя частоты подключен ко входу фазового дискриминатора. t//,o« (- . a aCffyiC

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации с пропорциональным регулированием | 1978 |

|

SU731604A2 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ | 1973 |

|

SU375772A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство синхронизации | 1982 |

|

SU1083392A1 |

| Устройство тактовой синхронизации | 1987 |

|

SU1555892A1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

Авторы

Даты

1971-01-01—Публикация