Предложенное устройство предназначено для использования в дискретных струйных вычислительных и управляющих системах.

Струйные обегающие устройства, построенные на сдвигающих регистрах, каждый из которых содержит элементы памяти и логические элементы, известны.

Основным недостатком известных устройств является то, что в них в каждом регистре использовано звено запуска, состоящее из трех элементов «НЕ-ИЛИ, «И и «Память, а каждая ячейка содержит пассивный элемент «НЕ-ИЛИ, что снижает быстродействие регистра и его надежность.

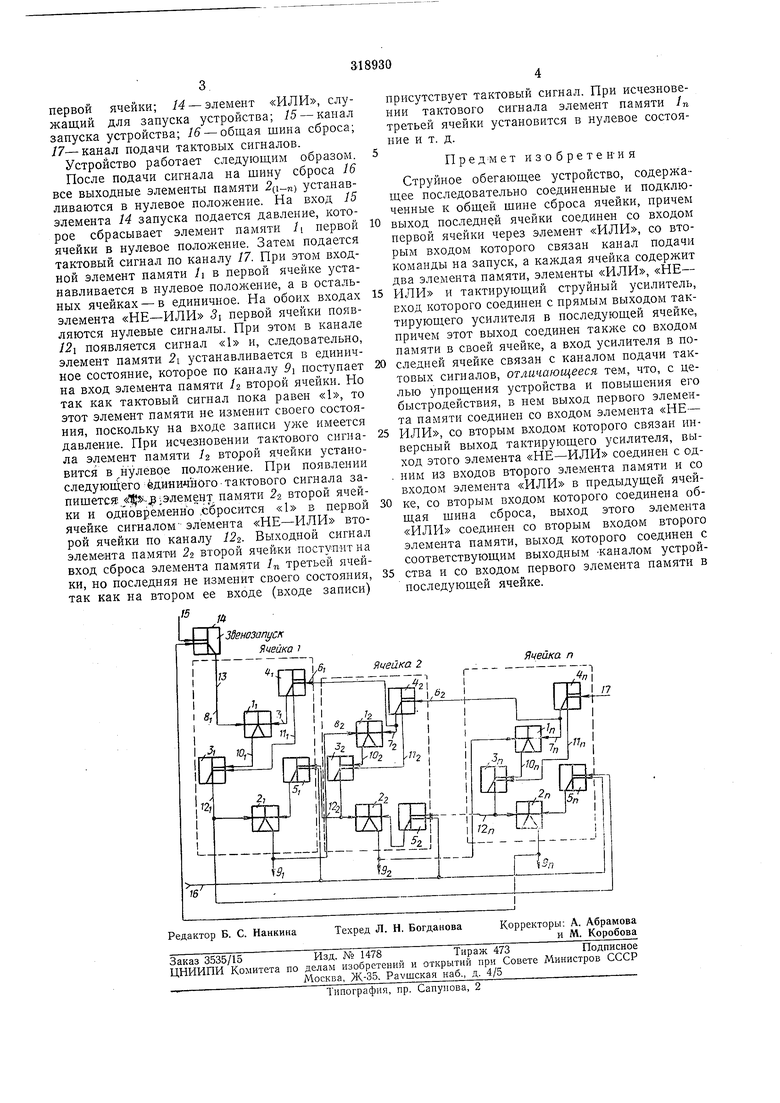

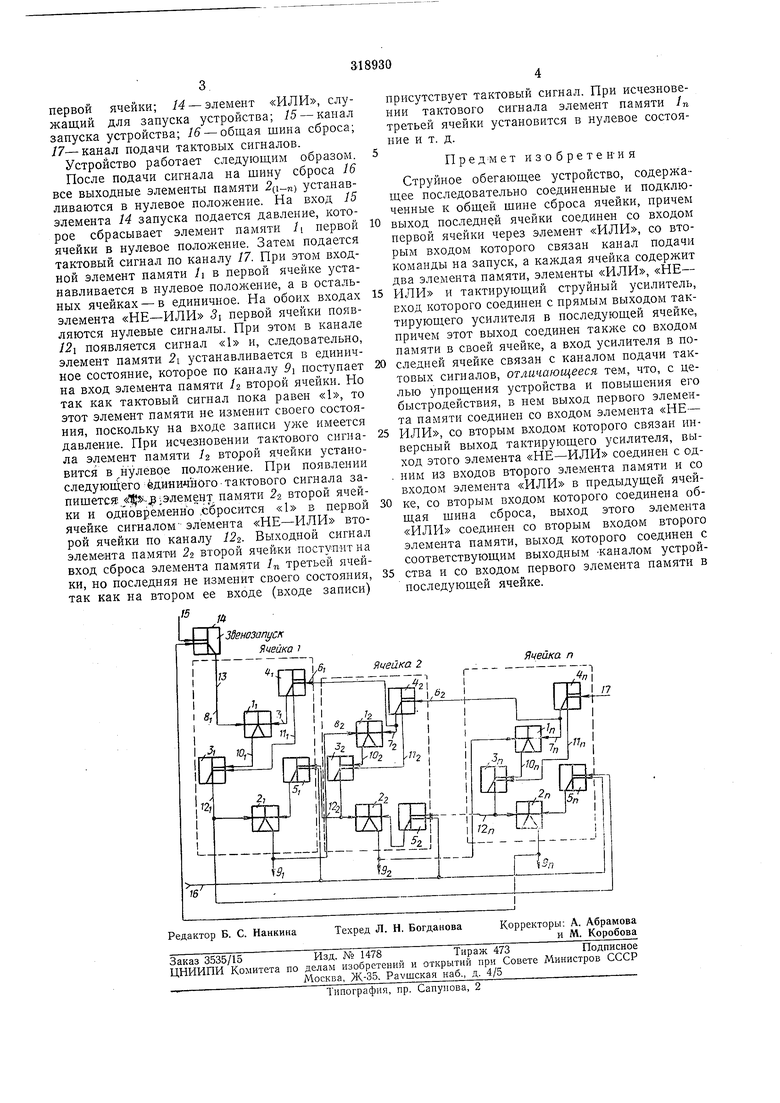

Предложенное струйное обегающее устройство содержит последовательно соединенные и подключенные к общей шине сброса ячейки, причем выход последней ячейки соединен со входом первой ячейки через элемент «ИЛИ, со вторым входом которого связан канал подачи команды на запуск; каждая ячейка содержит два элемента памяти, элементы «ИЛИ, «НЕ-ИЛИ и тактирующий струйный усилитель, вход которого соединен с прямым выходом тактирующего усилителя в последующей ячейке, причем этот выход соединен такл-:е со входом памяти в своей ячейке, а вход зсилителя в последней ячейке связан с каналом нодачи тактовых сигналов. Устройство отличается от известных тем, что в нем выход первого

элемента памяти соединен со входом элемента «НЕ-ИЛИ, со вторым входом которого связан инверсный выход тактирующего усилителя; выход этого элемента «НЕ-ИЛИ соединен с одним из входов второго элемента памяти и со входом элемента «ИЛИ в предыдущей ячейке, со вторым входом которого соединена общая щина сброса; выход этого элемента «ИЛИ соединен со вторым входом второго элемента памяти, выход которого соединен с соответствующим выходным каналом устройства и со входом первого элемента памяти в последующей ячейке. Такое выполнение устройства позволяет

упростить схему каждой ячейки, что повышает надел ность и быстродействие устройства.

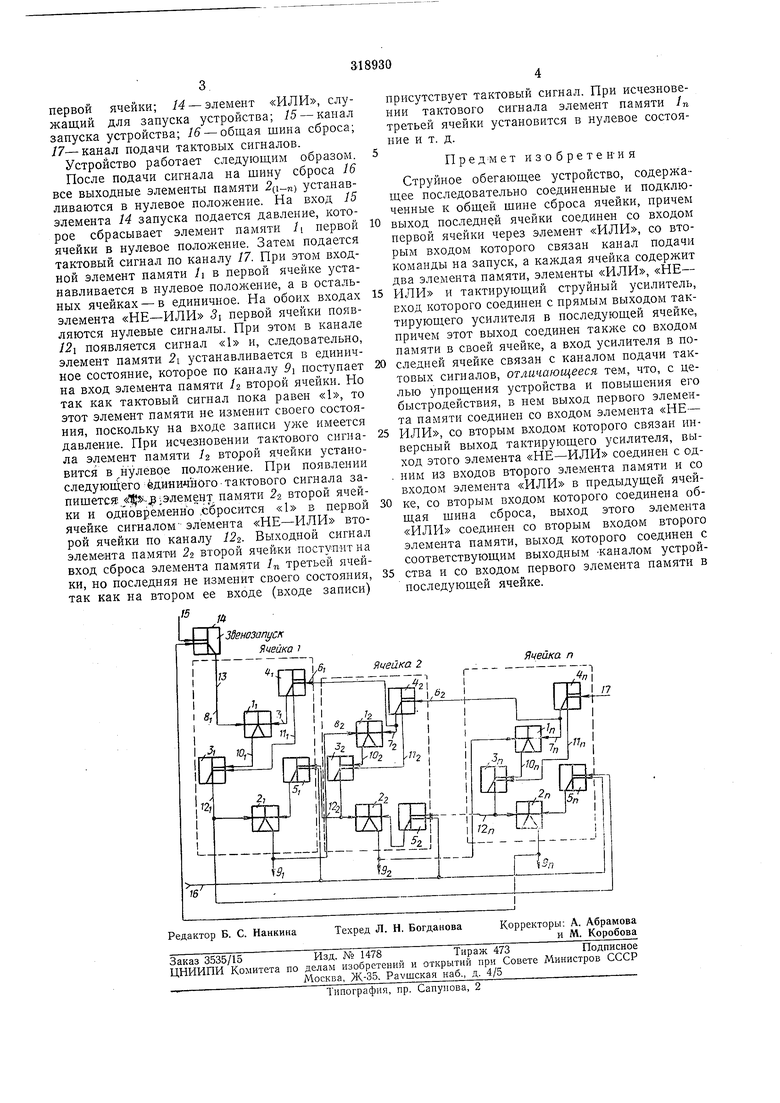

Схема предлагаемого зстройства представлена на чертеже, где приняты следующие условные обозначения (индексы, расположенные у цифр, соответствуют номеру ячейки, к которой относятся данные элементы): , . - входные и выходные элементы памяти соответственно; i-Зп - элементы «НЕ- 4i-4п - тактирующие усилители;

5п - элементы 6i-62 - каналы передачи тактирующего сигнала; 7;-7п, 8i-82 - управляющие каналы входного элемента памяти; 9i-9п - вЕзГходные каналы устройства; Wi-10„, 111-tin, 2i-}2п - каналы свяпервой ячейки; 14 - элемент «ИЛИ, служащий для запуска устройства; 15 - канал запуска устройства; 16 - общая шина сброса; 17- канал подачи тактовых сигналов. Устройство работает следующим образом. 5 После подачи сигнала на щину сброса 16 все выходные элементы памяти 2() устанавливаются в нулевое положение. На вход 15 элемента 14 запуска подается давление, которое сбрасывает элемент памяти Л первойЮ ячейки в нулевое положение. Затем подается тактовый сигнал по каналу 17. При этом входной элемент памяти li в первой ячейке устанавливается в нулевое полон ение, а в остальных ячейках -в единичное. На обоих входах15 элемента «НЕ-ИЛИ 3i первой ячейки появляются нулевые сигналы. При этом в канале 12i появляется сигнал «1 и, следовательно, элемент памяти 2i устанавливается в единичное состояние, которое по каналу PI поступает20 на вход элемента памяти /2 второй ячейки. Но так как тактовый сигнал пока равен «1, то этот элемент памяти не изменит своего состояния, поскольку на входе записи уже имеется давление. При исчезновении тактового сигна-25 ла элемент памяти h второй ячейки установится в нулевое положение. При появлении следуюпдего ёдиничного-тактового сигнала запишется .J ;Элeмeнx памяти 2 второй ячейки и одновременно .сбросится «1 в первой30 ячейке сигналом-элемента «НЕ-ИЛИ второй ячейки по каналу 122. Выходной сигнал элемента памяти 2 второй ячейки ноступитна вход сброса элемента памяти In третьей ячейки, но последняя не изменит своего состояния,35 так как на втором ее входе (входе записи) присутствует тактовый сигнал. При исчезновении тактового сигнала элемент памяти In третьей ячейки установится в нулевое состояние и т. д. П р е ДМ ет изобретения Струйное обегающее устройство, содержащее последовательно соединенные и подключенные к общей шине сброса ячейки, причем выход последней ячейки соединен со входом первой ячейки через элемент «ИЛИ, со вторым входом которого связан канал подачи команды на запуск, а каждая ячейка содержит два элемента памяти, элементы «ИЛИ, «НЕ- ИЛИ и тактирующий струйный усилитель, вход которого соединен с прямым выходом тактирующего усилителя в последующей ячейке, причем этот выход соединен также со входом памяти в своей ячейке, а вход усилителя в последней ячейке связан с каналом подачи тактовых сигналов, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, в нем выход первого элемента памяти соединен со входом элемента «НЕ- ИЛИ, со вторым входом которого связан инверсный выход тактирующего усилителя, выход этого элемента «НЕ-ИЛИ соединен с одним из входов второго элемента памяти и со входом элемента «ИЛИ в предыдущей ячейке, со вторым входом которого соединена общая шина сброса, выход этого элемента «ИЛИ соединен со вторым входом второго элемента памяти, выход которого соединеннее соответствующим выходным -каналом устройства и со входом первого элемента памяти в последующей ячейке.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИОГЕНД | | 1971 |

|

SU318929A1 |

| О-ОСНАЯш.тЕн:во--Т1Х1!Н"Е; ш | 1973 |

|

SU367411A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| УСТРОЙСТВО для ТРАНСЛЯЦИИ ИНФОРМАЦИИ о ДВИЖУЩИХСЯ ОТЦЕПАХ НА СОРТИРОВОЧНЫХ ГОРКАХ | 1969 |

|

SU255342A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| РЕГИСТР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1968 |

|

SU219888A1 |

| Устройство для ввода информации | 1990 |

|

SU1756878A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

Авторы

Даты

1971-01-01—Публикация