Изобретение относится к импульсной технике и может быть Использовано в цифровом синтезаторе частот.

Известны делители частоты с дробным переменным коэффициентом деления, содержащие декады с постоянными и переменными коэффициентами деления, триггеры памяти и схемы «И.

Недостаток известного делителя состоит в его сложности, особенно, если число декад с переменными коэффициентами деления больше двух.

Предлагаемое устройство отличается от из-, вестных тем, что идентичные декады с переменным коэффициентом деления связаны через включенные параллельно схемы «И с шиной входных сигналов, причем управляющие входы схем «И соединены с соответствующими выходами триггеров памяти, вход каждого из которых соединен с выходом соответствующей декады с постоянным коэффициентом деления.

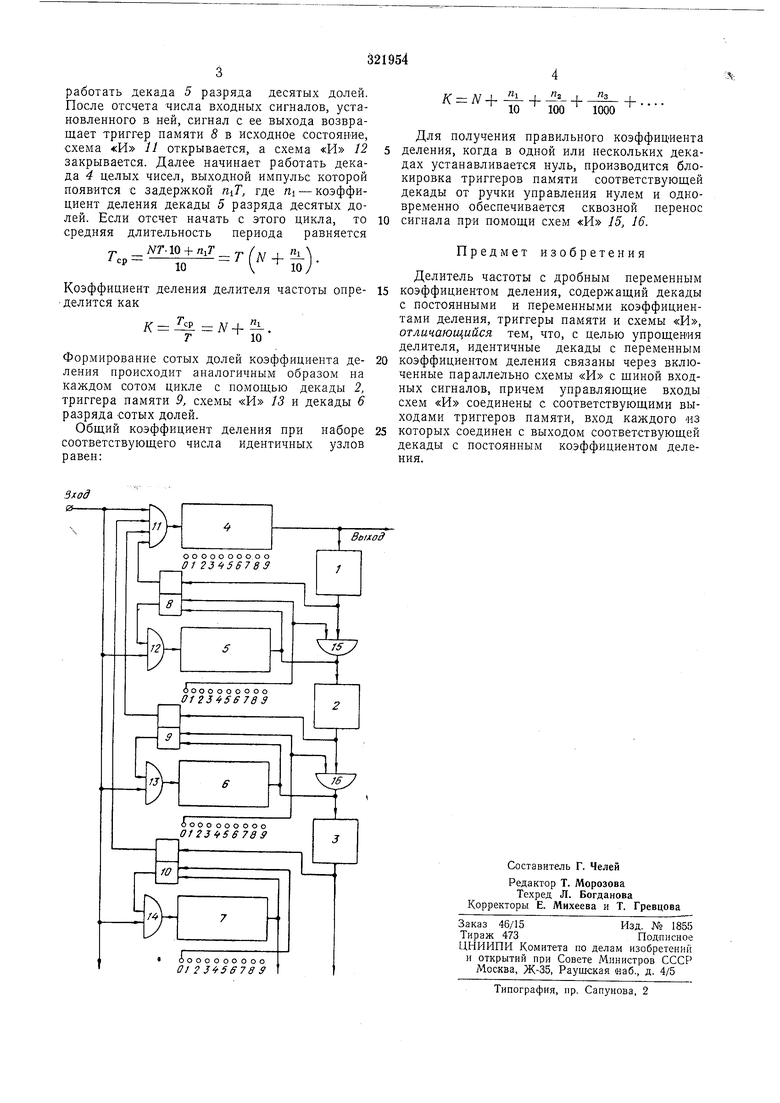

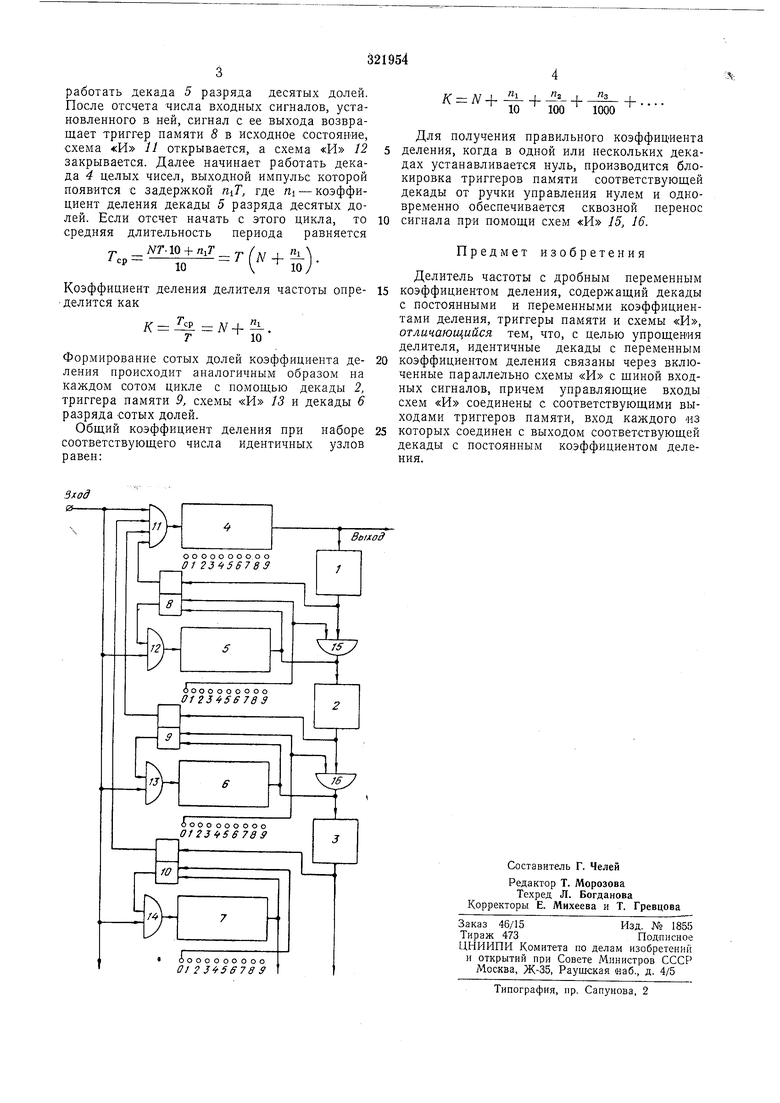

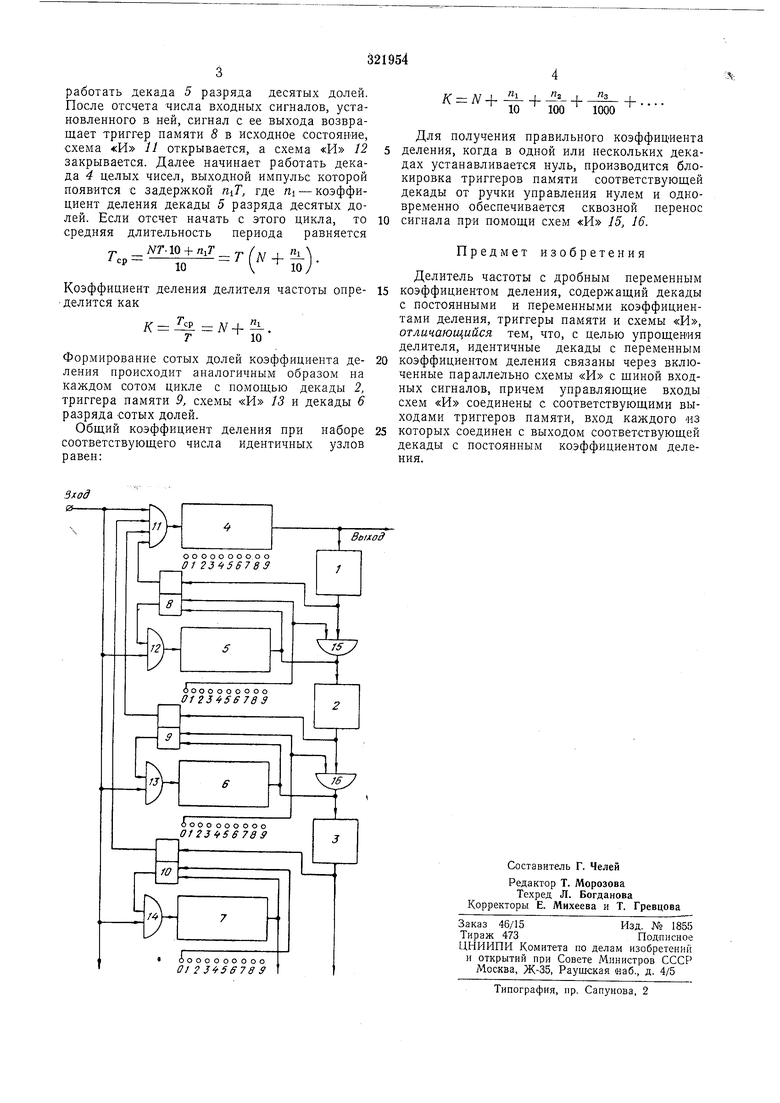

На чертеже представлена блок-схема предлагаемого делителя частоты с дробным переменным коэффициентом деления.

Делитель частоты содержит декады I-5 с постоянными коэффициентами деления, декады 4-7 с переменными коэффициентами деления, в которых производится установка числа от нуля до девяти в разряде целых чисел, десятых, сотых и тысячных долей набираемого коэффициента деления, триггеры памяти 5, 9 и /О и схемы «И //-16. Идентичные декады 4-7 с переменным коэффициентом деления связаны через включенные параллельно схемы «И 11-14 i соответствующими выходами триггеров памяти 8, 9, 10, вход каждого из которых соединен с выходом соответствующей декады /, 2, 3 с постоянным коэффициентом деления. Схемы «И 15, 16 служат для сквозного переноса сигнала при установлении нуля в одной или нескольких декадах.

Так как делитель частоты представляет собой набор идентичных декад, триггеров памяти и схем «И, то для уяснения работы делителя достаточно рассмотреть формирование двух знаков коэффициента деления.

В первый момент времени на выходе декады 4 разряда целых чисел существует последовательность импульсов с периодом TN, где Т - период следования входных сигналов, N - коэффициент деления декады 4 (предполагается, что триггеры памяти 8, 9, 10 разрещают прохождение сигнала на вход декады разряда целых чисел и запирают входы других декад). После десяти циклов счета заполнится декада 1, выходной сигнал с нее опрокинет триггер памяти 8, схема «И 11

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1972 |

|

SU344590A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1976 |

|

SU571914A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Делитель частоты следованияиМпульСОВ C дРОбНыМ КОэффициЕНТОМдЕлЕНия | 1979 |

|

SU818021A1 |

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| Программируемый делитель частоты | 1976 |

|

SU657615A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ | 1971 |

|

SU436446A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843245A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

Даты

1971-01-01—Публикация