Изобретение относится к области радиолокации и может быть использовано при измерении допплеровских частот.

Известны цифровые устройства фазовой подстройки частоты, содержащее счетчик с перестраиваемым коэффициентом деления, кварцевый генератор с формирователем импульсов, триггер, схему «И, схемы совпадения, регистр числа, дешифратор, два делителя частоты, две линии задержки и индикатор отслеживаемой частоты.

Однако в известных устройствах используются некоторые аналоговые элементы, имеющие нестабильные параметры, что приводит к недостаточной стабильности и надежности работы и снижает точность измерения при большом времени наблюдения.

С целью повыщения стабильности и надежности работы в предлагаемом устройстве к выходу схемы «И подключен счетчик дискриминатора, который через схемы совпадения, регистр числа и дешифратор подсоединен ко входу счетчика с перестраиваемым коэффициентом деления, а его выход соединен со входом триггера.

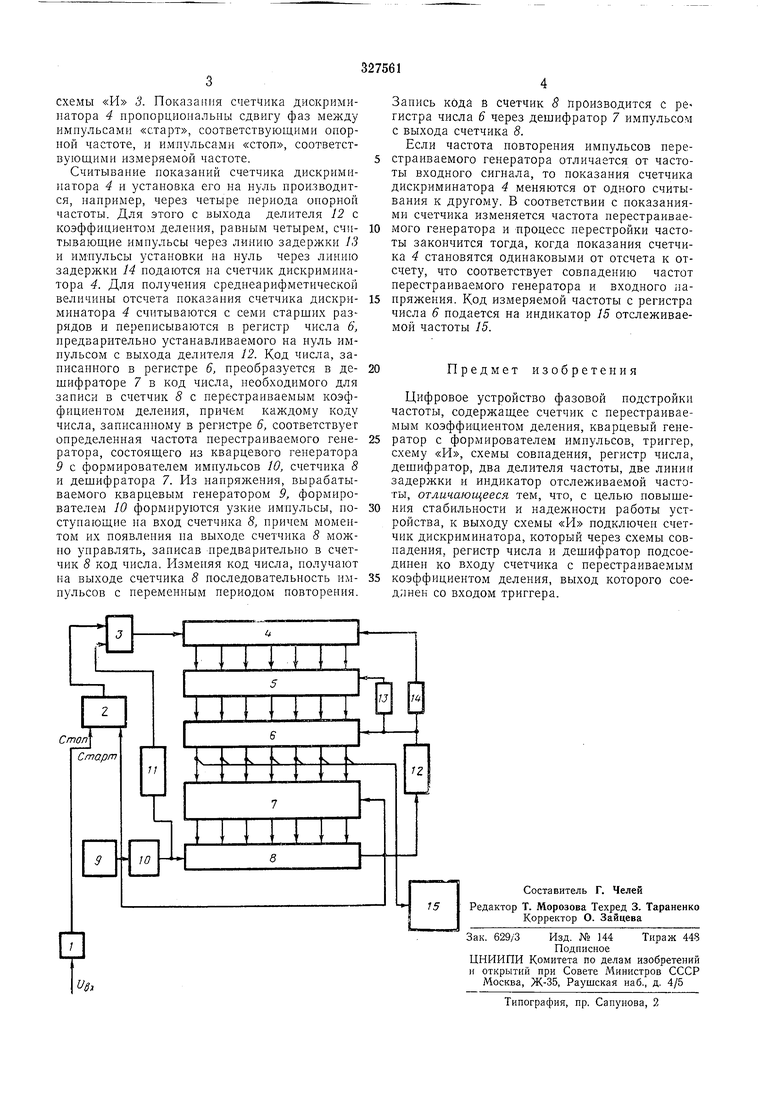

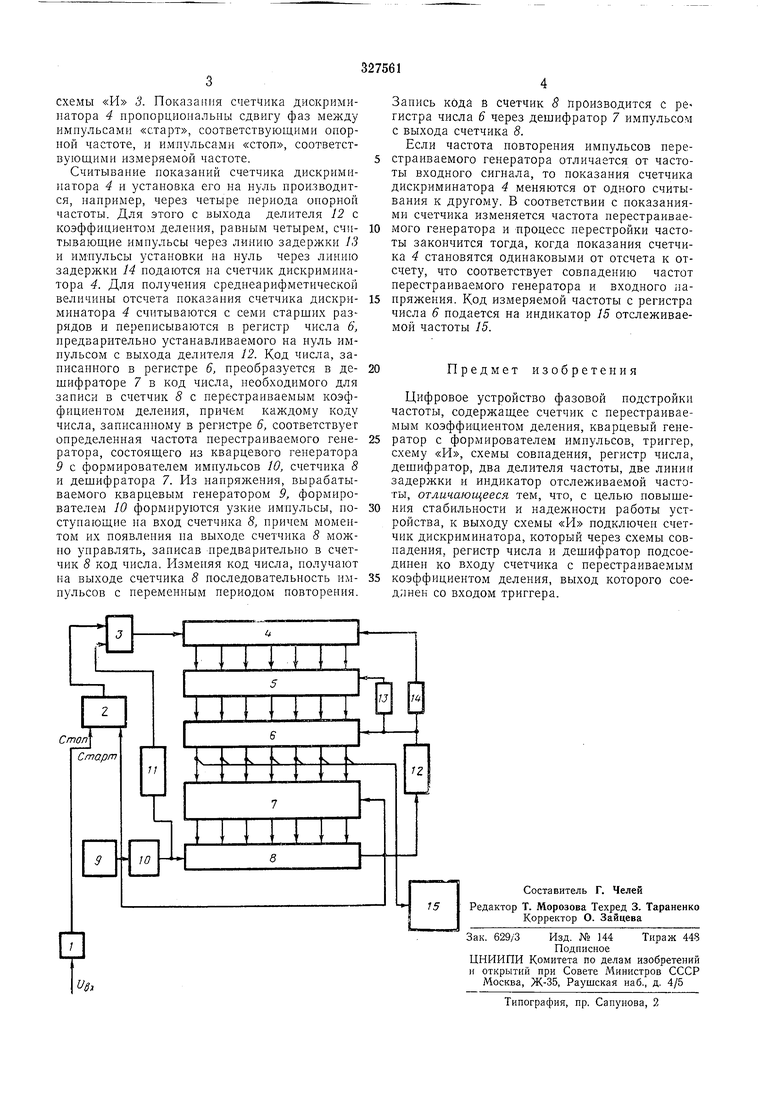

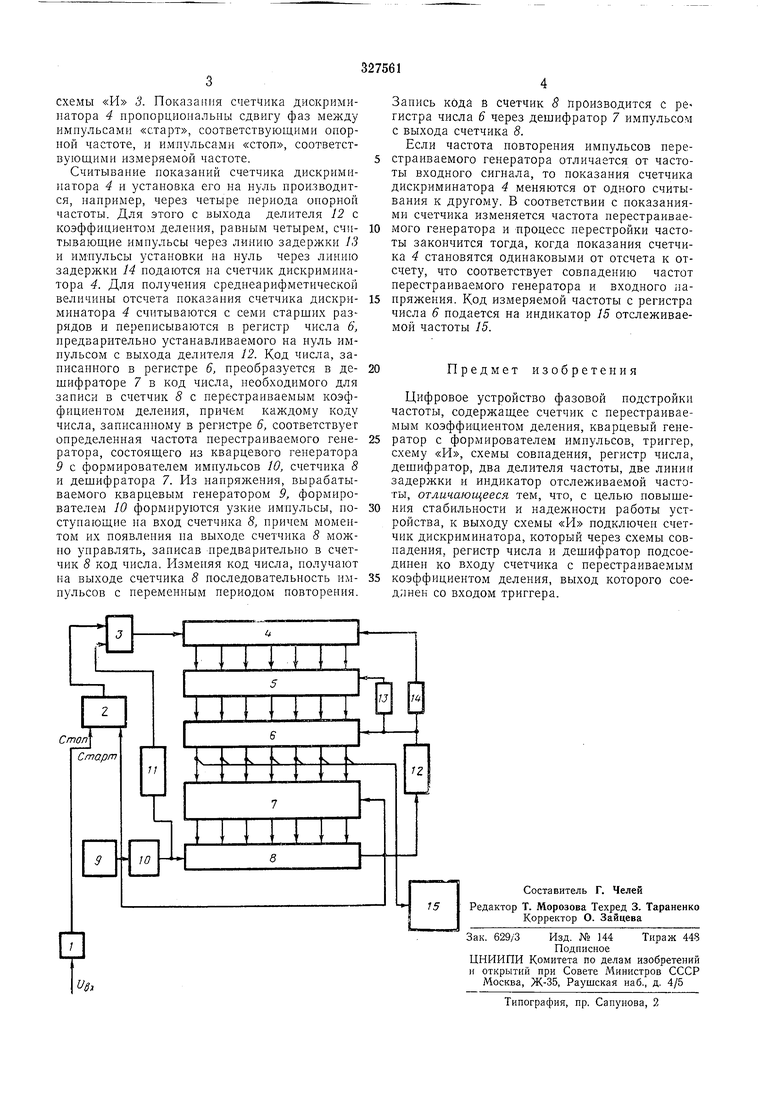

На чертеже дана блок-схема предлагаемого цифрового устройства фазовой подстройки частоты.

схемы совпадения 5, регистр числа 6, дешифратор 7, счетчик 8 с перестраиваемым коэффициентом деления, кварцевый генератор 9 с формирователем импульсов 10, делители частоты //, 12, линии задержки 13, 14 и индикатор 15 отслеживаемой частоты. К выходу схемы «Р1 3 подключен счетчик дискриминатора 4, который через схемы совпадения 5, регистр числа 6 и дешифратор 7 подсоединен ко входу

счетчика 8 с перестраиваемым коэффициентом деления, выход которого соединен со входом триггера 2.

Устройство работает следующим образом. Импульс «старт с вы.хода счетчика 8 поступает на один вход триггера 2 и опрокидывает его. С выхода триггера 2 разрешающий потенциал подается па схему «II 3, которая открывается и импульсы, поступающие на второй вход схемы «И с делителя частоты 11,

проходят на вход девятиразрядного счетчика дешифратора 4. Импульс «стоп формируется детектором 1 нулей из входного синусоидального сигнала при переходе его через нулевой уровень с отрицательной крутизной. Этот импульс поступает на второй вход трнггера 2 и приводит его в исходное состояние. Схема «1Ь 3 закрывается, и счет импульсов счетчиком дискриминатора 4 прекращается. Далее процесс повторяется, счетчпк дискршшнатора

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ | 1973 |

|

SU375772A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ АППАРАТУРЫ ПРИЕМА и ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU308533A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Анализатор плотности распределения случайной фазы сигнала | 1980 |

|

SU879500A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ | 1970 |

|

SU285066A1 |

| Фазометр | 1978 |

|

SU765750A1 |

| УСТРОЙСТВО ЧАСТОТНОЙ АВТОПОДСТРОЙКИ | 1972 |

|

SU342275A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

Даты

1972-01-01—Публикация