1

Изобретение относится к области запоминающих устройств.

Известио запоминающее устройство (ЗУ), содержащее регистр адреса, соединенный со входами перестраиваемого дещифратора, выходы которого соединены с управляющими входами адресных ключей, другие входы которых Объединены и подключены через общие адресные ключи к источникам напряжения поляризации и считывания, дополнительный общий адресный ключ, лодсоединепный к одному источнику напряжения частичной ноляризации, матрицу за:поми1нающих пьезотрансформаторов, адресные шины которых подключены к выходам адресных ключей, экранирующие шины - к .выходам разрядных ключей, входы которых объединены и соединены через общие разрядные ключи соответственно с источником напряжения поляризации и другим источником напряжения частичной поляризации, разрядные шины - ко входам дифференциональиых усилителей считывания.

Предложенное ЗУ отличается от известного тем, что содержит вономогательиьп оби;ий адресный ключ, вход которого подсоединен ко входам адресных ключей, а выход - к выходу дополнительного общего адресного ключа и Через резисторы - к адресным шинам.

Эти отличия позволяют снизить мощность, потребляемую устройством.

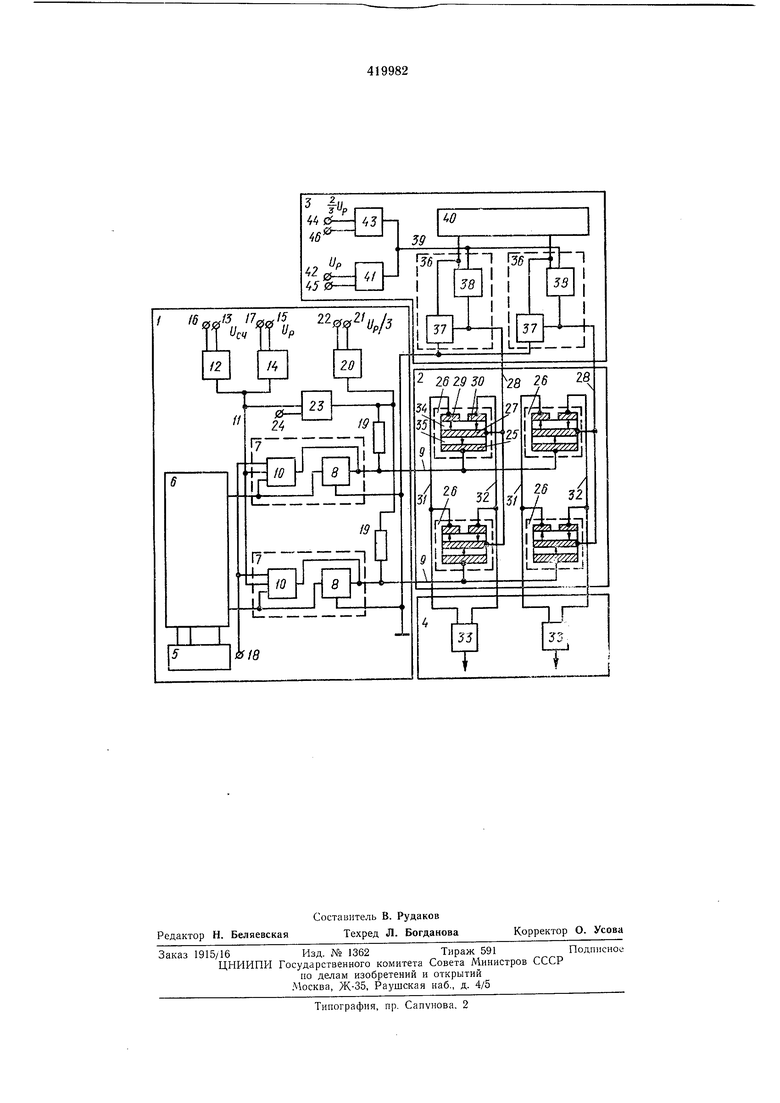

На чертеже изображена блок-схема устройства.

Устройство содержит блок 1 управления но адресу, матрицу 2 запоминающих ujHpoKonoлосных пьезотрансформаторов, блок 3 управления по разряду и блок 4 усилителей считывания.

Блок 1 управления ,по адресу содержит регистр 5 адреса, перестраиваемый дешифратор

6 с представлением выходных переменных в системе высоких и низких лотеициалов, выходы которого соединены с управляющими входами составных адресных ключей 7. Каждьп из составных адресных ключей состоит из

ключа 8, через который адресные шины 9 матрицы 2 соединены с тиной нулевого потенциала, и из ключа 10, через которьп адресные шины 9 1иодключены к шине 11 управляющих напряжений. Шина 11 через обидий адресный

ключ 12 соединена с источником напряжении считываиия - бч-ч (клемма 13) и через другой общий адресный ключ 14 соединена с источником напряжения поляризации - lj, (клемма 15). Клеммы 16 и 17 являются управляющими входами соответственно ключей 12 и 14. Кроме того, управляющие входы запрета адресных ключей 10 соединены с шиной 18 «Запрет. Адресные шины 9 через резисторы 19 подключены к выходу дополнительного

общего адресного ключа 20, вход которого

(клем.ма 21) соединен с источником напряжения частичной поляризации - Up3, составляющего одну треть нанрял ения ноляризации. Клемма 22 является управляющим входом ключа 20. Выход ключа 20 через всномогательный общий адресный ключ 23 соединен с щиной управляющих напряжений 11, т. е. с входами адресных ключей 7. Клемма 24 является управляющим входом ключа 23. В матрин 2 входные электроды 25 щироконолосных запоминающих пьезотрансформаторов 26 (запоминающих элементов) соединепы с адресными шинами 9. Экранирующие электроды 27 пьезотрансформаторов объединены но разрядам в экранирующие щипы 28. Выходные электроды 29 и 30 (то два на каждый разряд) пьезотрансформаторов объединены в разрядlibie шипы 31 и 32, которые соединепы с входами диф ферен|циальпых усилителей считывания 33 блока 4. Пьезокерамические пластины 34 генераторной секции пьезотрансформаторов имеют жесткую поляризацию, противоположного направления под выходными электродамп 29 и 30. Пластина 35 секции возбуждения может иметь различную поляризацию, направление ее определено записанной информацией. Экранирующие шины 28 подключены к выходам составных разрядных ключей 36, каждый из которых состоит из двух ключей: ключа 37, через который экранирующие щины соединены с шиной нулевого потенциала, и ключа 38, через который экранирующие щины соединены с щипой напряжений 39. Управляющие входы разрядных ключей соединены с входами регистра числа 40. Шипа 39 соединена через один ключ 41 с источником напряжения поляризации - LJy (клемма 42) и через второй ключ 43 с источником напря t/p (клемл еиия частичной поляризации

ма 44), составляющего две третьих нанряжения поляризации. Клеммы 45 и 46 являются управляющими входами соответственно ключей 41 и 43.

Запись информации по данному адресу производится с предварительной подготовкой элементов, при этом ранее записанная информация стирается, что производится следующим образом. Все разряды регистра 40 устанавливаются в «О, и потенциалы на выходных шинах регистра открывают ключи 38 и закрывают ключи 37. Дешифратор адреса перестраивается в состояние с представлением выходных переменных в системе низких потенциалов. При этом в исходном режиме положительным потенциалом на всех выходных щинах дешифратора ключи 8 закрыты, закрыты и ключи 10 положительным потенциалом на щине 18 «Запрет. По сигналу стирания потенциал на выходной шине дешифратора, соответствующий коду в регистре адреса 5, снижается до нуля, на остальных шинах потенциал остается высоким, вследствие чего открывается только ключ 8 выбранного адреса и соответствующая адресная шина 9 подключается к шине нулевого нотенциала. Одновременно сигналы стирания поступают па управляющие входы 17, 24, 45 соответственно ключей 14, 23, 41.

К экранирующим шинам через ключи 38 и к адресным шииам через резисторы 19, за исключением выбранной адресной шины, прикладывается напряжепие - U,. В выбранном адресе напряжение - Up к шине 9 не. прикладывается, так как соответствующий ключ 8 открыт и эта щина подключена к щине нулевого потенциала. Таким образом, к электродам 27 и 25 ньезотрансформаторов только выбранного адреса прикладывается разница

напряжения - Up. Под действием этого напряжения поляризация пластин 35 принимает направление, соответствующее значению «О, т. е. стирается ранее записанная информация и данный адрес подготавливается к записи

пового числа.

Записываемое число принимается в регистр 40. При этом под действием потенциалов на выходных щинах регистра экранирующие щины 28, соответствующие тем разрядам регистра, которые находятся в «1, подключаются через ключи 37 к шине нулевого потенциала, а экранирующие шины, соответствующие тем разрядам регистра, которые находятся в состоянии «О, подключаются через ключи 38 к щине 39. Дешифратор адреса перестраивается в состояние с представлением выходных перемепных в системе высоких потенциалов. В исходном состоянии нулевым потенциалом на

всех выходных щипах дещифратора ключи 10 закрыты. Снижением до нуля нанряжения смещения - бсм (на чертеже не показано) закрываются и ключи 8 всех адресов. По сигналу записи положительный импульс напряжеПИЯ на выходной щине дещифратора, соответствующей коду адреса в регистре 5, открывает выбранный ключ 10. Одновременно с этим сигналы записи прикладываются к управляющим входам 17, 22, 46 ключей, и ключи 14, 20, 43 открываются. При этом к выбранной адресной шине 9 через открытый ключ 10 прикладывается напряжение - Up, к невыбранным адресным шинам через резисторы 19 прикладывается напряжение -

-Up. К экранирующим шинам 28, которые

иодключены к шине 39.через ключи 38, открытые согласно коду регистра числа 40, при2 ,,

кладывается напряжениеUp, остальные

экранирующие щины через открытые ключи 37 иодключены к шине нулевого потенциала. Вследствие этого к электродам 27, 25 элементов невыбранных адресов приложено напряжение -|Up илиUp, к электродам элементов выбранного адреса, в которые записы1 ,, ваются нули приложено напряжение

а к электродам элементов, в которые записываются единицы, приложено напряжение i-Up. При действием напряжения изменяется направление поляризации пластин 35 соответствующих элементов, т. е. происходит запись «1. Для изменения поляризации пластин 32 напряжения - Up недостаточно, поэтому разрун ения информации в невыбранных адресах и записи ложной информации в вы бранном адресе не происходит. Таким образом после стирания предыдущей информации и записи новой пьезокерамические пластины 35 элементов выбранного адреса поляризованы в направлениях, которые соответвуют записываемому числу.

В режиме считывания информации все разряды регистра 40 находятся в состоянии «1, ключи 37 открыты и экранирующие щины подключены к щине нулевого потенциала. Дешифратор 6 находится в состоянии, при котором выходные переменные дешифратора представлены в системе высоких потенциалов. При этом в исходном состоянии ключи 10 закрыты, а ключи 8 открыты, вследствие чего адресные шины 9 подключены к щине нулевого потенциала. К щине 11 через открытый ключ 12 приложено достоянное напряжения - t/сч. По сигналу чтения короткий положительный импульс с соответствующего выхода дешифратора прикладывается к управляющему входу выбранного адресного ключа. При этом ключ 8 закрывается, ключ 10 открывается и во время действия импульса с выхода дешифратора к адресной шине прикладывается напряжение - Uc4- Импульс напрял ения, приложенный к адресной шине, вызывает импульсную деформацию пластины 35 элементов данного адреса и одновременно с этим импульсную деформацию пластины 34, причем направление этой деформации зависит от направления поляризации пластины 35, т. е. от записанной информации. При этом на разрядных шинах 31 и 32 появляются разнополярные сигналы, так как участки пьезокерамики

под электрода.ми 29 и 30 поляризованы встречно, причем полярность выходных сигналов определяется направлением механической деформации пластины 32, т. е. записанной информацией. Эти сигналы поступают на входы разрядных усилителей считывания, и на выходах усилителей появляются импульсы, полярность которых однозначно связана с записанной информации. Данное устройство донускает многократное считывание, причем считывание является неразрущающим, благодаря чему подобное устройство целесообразно использовать в качестве полупостоянного запоминающего устройства.

Предмет и з о -б р е т е н и я

Запоминающее устройство, содержаш,ее регистр адреса, соединенный со входами перестраиваемого дещифратора, вы.чоды которого соединены с управляющими входа.ми адресных ключей, другие входы которых объединены и подключены через общие адресные ключи к источникам напряжения поляризации и считывания, донолнительный общий адресный ключ, подсоединенный к одно.му источнику напряжения частичной поляризации, матрицу

запо.минающих пьезотрансформаторов, адресные шины которых подключены к выходам адресных ключей, экранирующие шины - к выходам разрядных ключей, входы которых объединены и соединены через общие разрядные ключи соответственно с источником напряжения поляризации и другим источником напряжения частичной поляризации, разрядные щины - ко входам дифференциальных усилителей считывания, отличающееся

тем, что, с целью снижения потребляемой мощности, оно содержит вспомогательный общий адресный ключ, вход которого подсоединен ко входам адресных ключей, а выход - к выходу дополнительного общего адресного

ключа и через резисторы - к адресным шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU364962A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

Авторы

Даты

1974-03-15—Публикация

1971-07-12—Подача