Изобретение относится к радиотехнике и может быть использовано для фазовой синхронизации в приемниках дискретной информации.

Цель изобретения - повышение помехоустойчивости при малом времени вхождения в синхронизм.

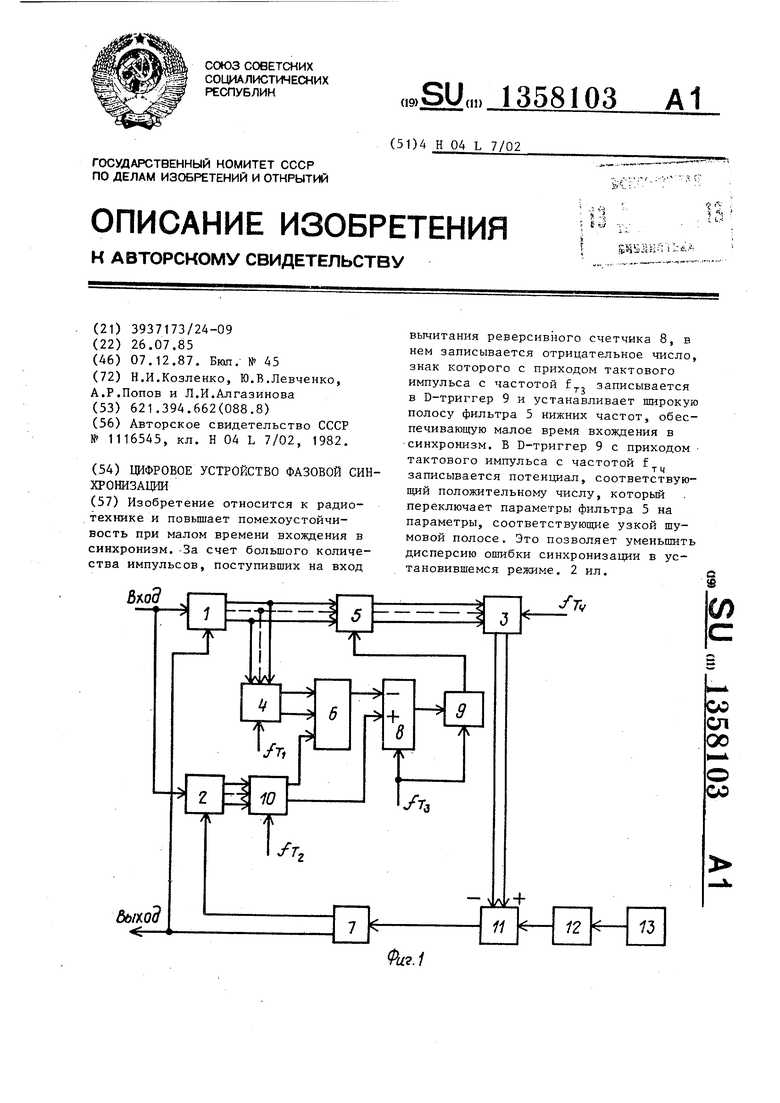

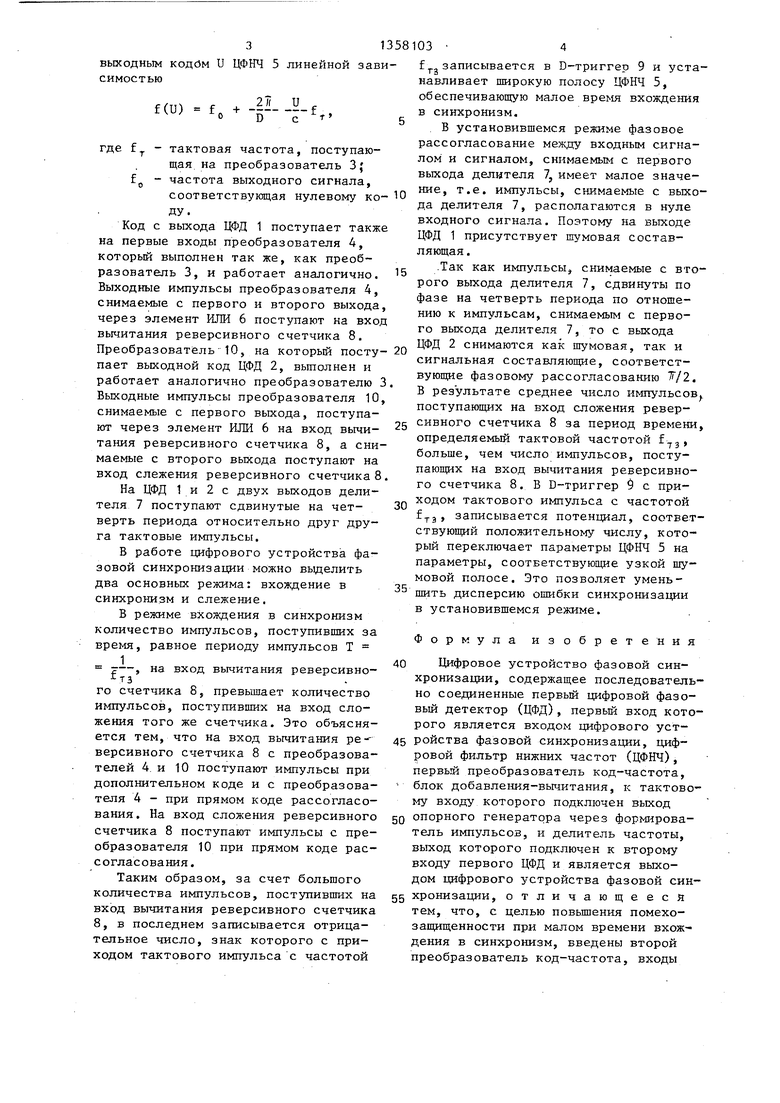

На фиг. 1 представлена структурная электрическая схема цифрового устройства фазовой синхронизации; на фиг, 2 - структурная схема первог второго и третьего преобразователей код-частота.

Цифровое устройство фазовой синхронизации содержит первый 1 и второй 2 (ЦФД), первый 3 и второй 4 преобразователи код-частота, ЦФНЧ 5, элемент ИЛИ 6,делитель 7 частоты, реверсивный счетчик 8, D-триггер 9, третий преобразователь 10 код-частота, блок 11 добавления-вычитания, формирователь 12 импульсов, опорный генератор 13.

Преобразователь код-частота (фиг. 2) содержит сумматор 14, регистр 15, первый 16 и второй 17 элемент И,

Устройство работает следующим образом.

На первый вход цифрового фазового детектора 1 поступает входной сигнал, на второй вход - импульсыс делителя 7 частоты.

В зависимости от фазового сдвига импульсов делителя 7 частоты и входного сигнала на выходе цифрового фазового детектора 1 формируется код, абсолютная величина и знак которого соответствуют значению фазового рассогласования входного и выходного сигналов. При отсутствии фазового рассогласования с выхода ЦФД 1 на вход ЦФНЧ 5 и первого преобразователя 3 код-частота поступает нулевой код. ЦФНЧ 5 предназначен для уменьшения действия помех на точность подстройки фазы, а также для получения требуемых динамических характеристик С выхода ЦФНЧ 5 сигнал поступает на входы первого слагаемого сумматора первого преобразователя 3 код-частота. На вторые входы сумматора 14 поступает код, снимаемый с регистра 15 При поступлении тактовых импульсов регистр 15 в нем записывается результат сложения выходного кода ЦФНЧ 5 с содержимым регистра 15. Появление на выходе сумматора 14 сигна0

5

0

5

ла переноса (займа), если код прямой (дополнительный), разрешает прохождение тактового импульса На первый (второй) выход преобразователя через элементы И 16 и 17.

Частота выходных тактовых импульсов с преобразователя 3 пропорциональна абсолютной величине кода, снимаемого с выхода ЦФНЧ 5, и частоте тактовых импульсов f ,.„ , поступающих на регистр 15. Покажем это на примере. Пусть на вход четьфехразрядного сумматора 14 поступает положительный код, равный единице. С приходом тактовых импульсов регистр 15, к содержимому регистра добавляется единица. Для того, чтобы возник сигнал переноса в сумматоре 14, на регистр 15 должно поступить 16 тактовых импульсов. Если на входы сумматора 14 поступает код, равный двум, то сигнал переноса на выходе сумматора 14 возникает в два раза чаще, т.е. через восемь импульсов и т.д.

Аналогично, при поступлении на преобразователь 3 дополнительного кода, равного единице (соответствукицего отрицательному рассогласованию), и 16 тактовых импульсов t на выходе переноса сумматора 14 возникает сигнал. Если на вход преобразователя 3 поступает дополнительный код,равный двум, то сигнал переноса на выходе сумматора 14 возникает в два раза чаще и т.д.

С выходов преобразователя 3 сигналы поступают на входы управления блока 11 добавления-вычитания импульсов. В зависимости от того, на какой вход блока 11 поступают сигналы с преобразователя 3, блок 11 добавления-вычитания вводит дополнительный или стирает один из импульсов в импульсной последовательности, формируемой формирователем 12 из сигнала опорного генератора 13. Изменение числа импульсов на единицу в импульсной последовательности на входе делителя 7 частоты приводит к дискретному сдвигу фазы выходного сигнала на величину

2 t -5-

0

5

0

0

55

где D - коэффициент деления частоты

выходного делителя. При данном алгоритме работы блоков частота выходного сигнала связана с

и

31358103

ЦФНЧ 5 линейной завиf

на об в

„ +

5

у

с

t

f,

где f - тактовая частота, поступающая на преобразователь 3; частота выходного сигнала, соответствующая нулевому ко ду.

Код с выхода ЦФД 1 поступает такж на первые входы преобразователя 4, который выполнен так же, как преобразователь 3, и работает аналогично. Выходные импульсы преобразователя 4, снимаемые с первого и второго выхода через элемент ИЛИ 6 поступают на вхо вычитания реверсивного счетчика 8, Преобразователь 10, на который посту пает выходной код ЦФД 2, выполнен и работает аналогично преобразователю Выходные импульсы преобразователя 10 снимаемые с первого вькода, поступают через элемент ИЛИ 6 на вход вычитания реверсивного счетчика 8, а снимаемые с второго выхода поступают на вход слежения реверсивного счетчика 8

На ЦФД 1 и 2 с двух выходов делителя 7 поступают сдвинутые на четверть периода относительно друг друга тактовые импульсы.

В работе цифрового устройства фазовой синхронизации можно выделить два основных режима: вхождение в синхронизм и слежение.

В режиме вхождения в синхронизм количество импульсов, поступивших за время, равное периоду импульсов Т

т--, на вход вычитания реверсивноJ T3

го счетчика 8, превьшает количество импульсов, поступивших на вход сложения того же счетчика. Это объясняется тем, что на вход вычитания ре версивного счетчика 8 с преобразователей 4 и 10 поступают импульсы при дополнительном коде и с преобразователя 4 - при прямом коде рассогласования. На вход сложения реверсивного счетчика 8 поступают импульсы с преобразователя 10 при прямом коде рассогласования.

Таким образом, за счет большого количества импульсов, поступивших на вход вычитания реверсивного счетчика 8, в последнем записывается отрицательное число, знак которого с приходом тактового импульса с частотой

0

5

0

0

35

f записывается

в D-триггер 9 и устанавливает широкую полосу ЦФНЧ 5, обеспечивающую малое время вхождения в синхронизм.

В установившемся режиме фазовое рассогласование между входным сигналом и сигналом, снимаемым с первого выхода делителя 7, имеет малое значение, т.е. импульсы, снимаемые с выхода делителя 7, располагаются в нуле входного сигнала. Поэтому на выходе ЦФД 1 присутствует шумовая составляющая .

.Так как импульсы, снимаемые с второго выхода делителя 7, сдвинуты по фазе на четверть периода по отношению к импульсам, снимаемым с первого выхода делителя 7, то с выхода ЦФД 2 снимаются как шумовая, так и сигнальная составляющее, соответствующие фазовому рассогласованию 7Г/2. В результате среднее число импульсов поступающих на вход сложения ревер- 5 сивного счетчика 8 за период времени, определяемый тактовой частотой з больше, чем число импульсов, посту- пaюшJ x на вход вычитания реверсивного счетчика 8. В D-триггер 9 с приходом тактового импульса с частотой

, записывается потенциал, соответ- ствуюш;ий положительному числу, который переключает параметры ЦФНЧ 5 на параметры, соответствуюш 1е узкой шумовой полосе. Это позволяет уменьшить дисперсию ошибки синхронизации в установившемся режиме.

Формула изобретения

40

Цифровое устройство фазовой синхронизации, содержащее последовательно соединенные первый цифровой фазо- вый детектор (ЦФД), первьш вход которого является входом цифрового уст-

45 ройства фазовой синхронизации, цифровой фильтр нижних частот (ЦФНЧ), первьм преобразователь код-частота,

блок добавления-вычитания, к тактовому входу которого подключен выход

50 опорного генератора через формирователь импульсов, и делитель частоты, выход которого подключен к второму входу первого ЦФД и является выходом цифрового устройства фазовой син55 хронизации, отличающееся тем, что, с целью повьшзения помехозащищенности при малом времени вхождения в синхронизм, введены второй преобразователь код-частота, входы

которого подключены к выходам первого ЦФД, элемент ИЛИ, реверсивный счетчик, D-триггер и последовательно соединенные второй иЗД, к первому и второму входам которого подключен соответственно первый вход первого ЦФД и второй выход делителя частоты, и третий преобразователь код-частота, первый и второй выходы которого сое

динены соответственно с первым входом элемента ИЛИ, к второму и третьему входам которого подключены выходы второго преобразователя код-частота, и с входом сложения реверсивного сч.ет- чика, к входу вычитания которого подключен выход элемента ИЛИ, а выход через D-триггер подключен к дополнительному входу ЦФНЧ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Дисретный синхронизатор | 1977 |

|

SU651446A2 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1246395A1 |

| Устройство синхронизации М-последовательности | 1981 |

|

SU1053312A1 |

| Устройство фазовой синхронизации | 1982 |

|

SU1116545A1 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1327307A2 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Устройство фазовой автоподстройки частоты | 1981 |

|

SU1091354A1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

Изобретение относится к радиотехнике и повьшает помехоустойчивость при малом времени вхождения в синхронизм. -За счет большого количества импульсов, поступивших на вход вычитания реверсивного счетчика 8, в нем записывается отрицательное число, знак которого с приходом тактового импульса с частотой f записывается в D-триггер 9 и устанавливает широкую полосу фильтра 5 нижних частот, обеспечивающую малое время вхождения в синхронизм. В D-триггер 9 с приходом тактового импульса с частотой f записывается потенциал, соответствующий положительному числу, который переключает параметры фильтра 5 на параметры, соответствующие узкой шумовой полосе. Это позволяет уменьшить дисперсию ошибки синхронизации в установившемся режиме. 2 ил.

Фиг.г

Составитель И.Грацианская Редактор В.Петраш Техред М.Ходанич Корректор С.Шекмар

Заказ 6009/57 Тираж 636 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная, 4

/7

2

| Устройство фазовой синхронизации | 1982 |

|

SU1116545A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-12-07—Публикация

1985-07-26—Подача