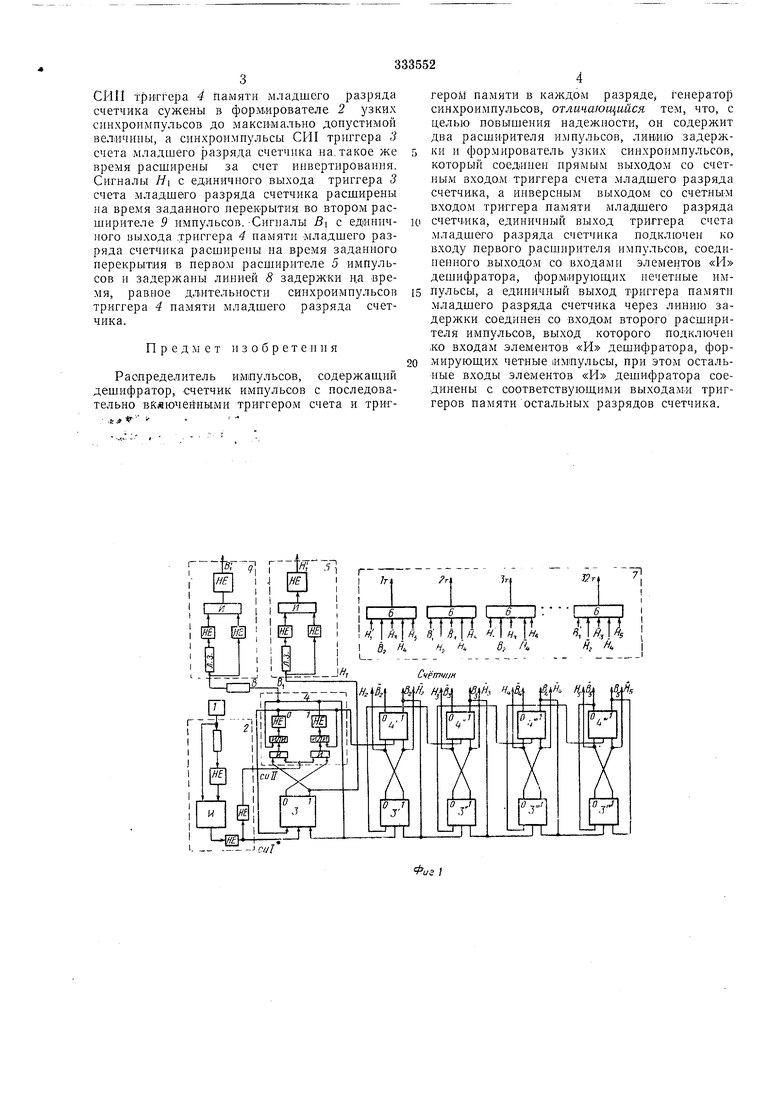

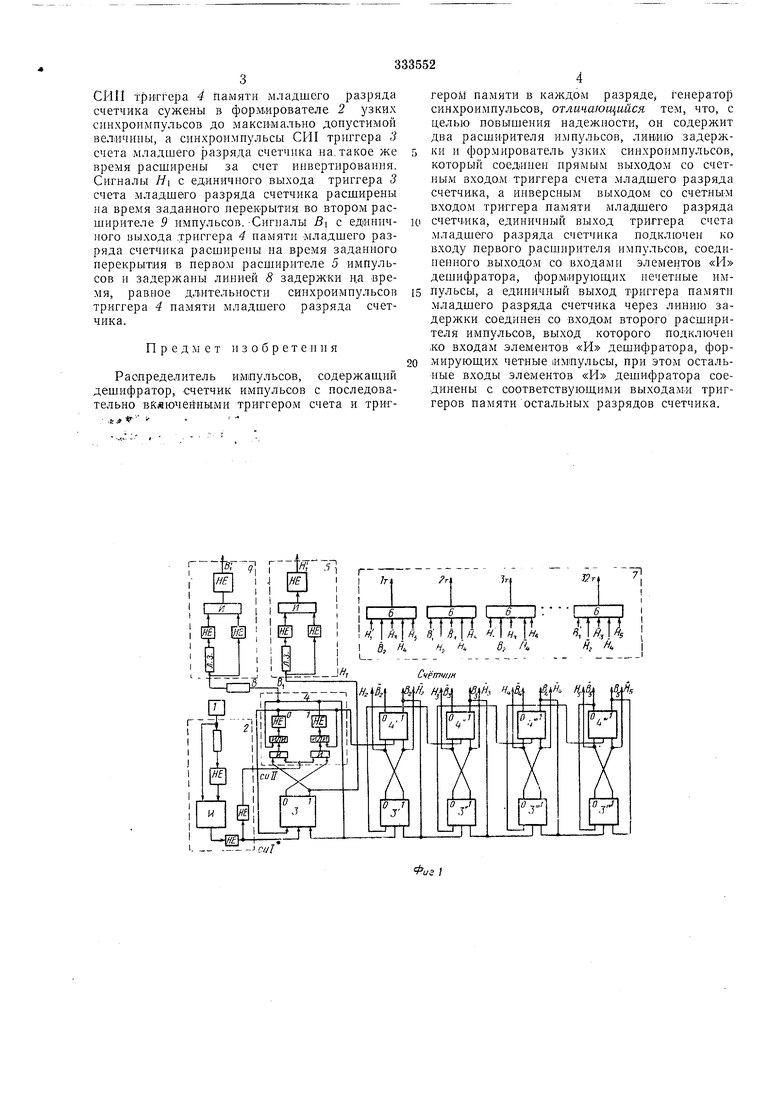

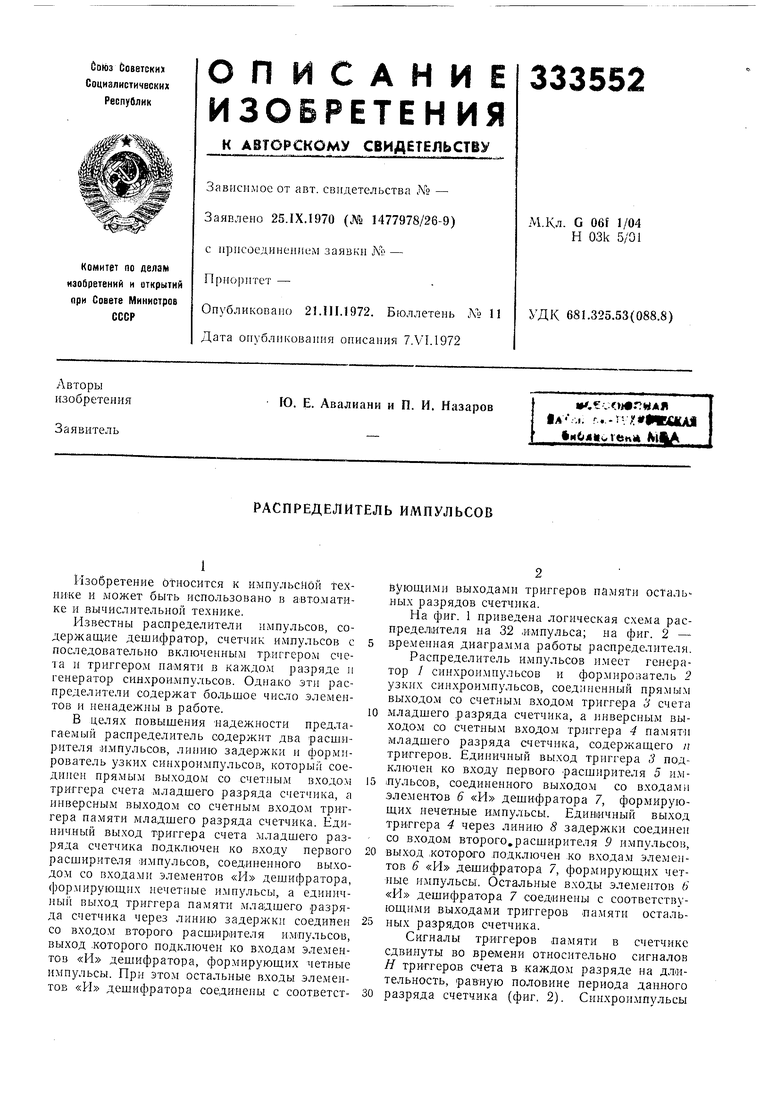

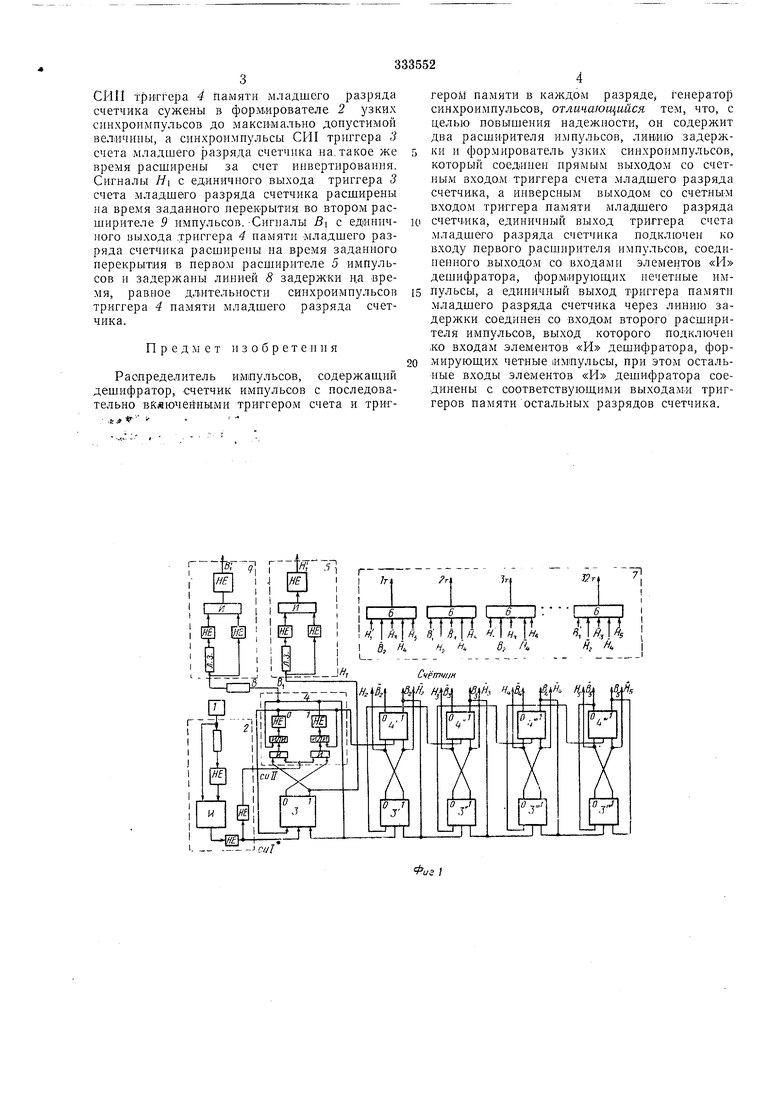

11зобретеиие отиосится к импульсной техинке и может быть использовано в автоматике и вычислительной технике. Известны распределители импульсов, содержащие дешифратор, счетчик импульсов с последовательно включенным rpiHrrepOM счета и триггером намяти в каждол разряде и генератор синхроимпульсов. Одна.ко эти распределители содержат большое число элементов и ненадежны в работе. В целях повышения -надежности предлагаемый распределитель содержит два расширителя импульсов, линию задержки и формирователь узких синхроимпульсов, который соединен прямым выходом со счетным входом триггера счета младшего разряда счетчика, а инверсным выходом со счетным входом триггера памяти младшего разряда счетчика. Единичнь й выход триггера счета младшего разряда счетчика подключен ко входу первого расширителя импульсов, соединенного выходом со входами элементов «И дешифратора, форлгирующих нечетные импульсы, а единичный выход триггера памяти младшего разряда счетчика через линию задержки соединен со входом второго расширителя импульсов, выход .которого подключен ко входам элементов «И дешифратора, формируюших четные импульсы. При этом остальные входы элементов «И дешифратора соединены с соответствующими выходами триггеров памяти остальных разрядов счетчика. На фиг. 1 приведена логическая схема распределителя на 32 импульса; на фиг. 2 - временная диаграмма работы распределителя. Распределитель импульсов имеет генератор / синхрои-мпульсов и формирователь 2 узких синхроимпульсов, соединенный прямым выходом со счетным входом триггера 3 счета младшего разряда счетчика, а инверсным выходам со счетным входом триггера 4 памяти младшего разряда счетчика, содержапдего п триггеров. Единичный выход триггера 3 подключен ко входу первого расширителя 5 нмлульсов, соединеиного выходом со входами элементов 6 «И дешифратора 7, формирующих нечетные импульсы. Единичный выход триггера 4 через линию 8 задержки соединен со входом второго,расширителя 9 импульсов, выход .которого подключен .ко входа.м элементов 6 «И дешифратора 7, фор.мирующих четные импульсы. Остальные входы элементов 6 «И дешифратора 7 соединены с соответствующими выходами триггеров па.мяти остальных разрядов счетчика. Сигналы триггеров памяти в счетчике сдвинуты во времени относительно сигналов Н триггеров счета в каждом разряде на длительность, равяую половине периода данного разряда счетчика (фиг. 2). Синхроимпульсы

СИП триггера 4 памяти младшего разряда счетчика сужены в формирователе 2 узких синхроимпульсов до максимально допустимой величины, а синхроимпульсы GUI триггера 3 счета младшего разряда счетчика на,, такое же время расширены за счет инвертирования. Сигналы HI с единичного выхода триггера 3 счета младшего разряда счетчика расширены на время заданного перекрытия во втором расширителе 9 импульсов. -Сигналы В с единичного выхода .триггера 4 памяти младшего разряда счетчика расширены па время заданного перекрытия в первом расширителе 5 импульсов и задержаны линией 8 задержки да время, равное длительности синхроимпульсов триггера 4 памяти младшего разряда счетчика.

Предмет изобрете и и я

Распределитель имоульсов, содержаш,ий дешифратор, счетчик импульсов с последовательно включенными триггером счета и триг/ -к

героМ памяти в каждом разряде генератор синхроимпульсов, отличающийся тем, что, с целью повышения надежности, он содержит два расширителя импульсов, линию задержки и формирователь узких синхроимпульсов, который соединен прямым выходом со счетным входо,м триггера счета младшего разряда счетчика, а инверсным выходом со счетным входом триггера памяти младшего разряда

счетчика, единичный выход триггера счета младшего разряда счетчика подключен ко входу первого расширителя импульсов, соединенного выходом со входами элементов «И дешифратора, формируюш.их нечетные импульсы, а единичный выход триггера памяти младшего разряда счетчика через линию задержки соединен со входом второго расширителя импульсов, выход которого подключен ко входам элементов «И дешифратора, формирующих четные имиульсы, при этом остальные входы элементов «И дешифратора соединены с соответствуюш,ими выходами триггеров памяти остальных разрядов счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФОРМЫ И ПЛОЩАДИ СВЕТОКОНТРАСТНОГО ОБЪЕКТА | 1992 |

|

RU2100776C1 |

| Устройство для вывода информации | 1990 |

|

SU1727127A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

71

,

б I . L °г J L /.. J

М f t t t f t TTTTtM t t }

, U, Wj e; U, U. . U, IH, в, I //, 14

H, A, I

сии р1|1 1ЩТр1ГГ1ГрЩ®1 7р Н29Н рГр1|

С//

Л , л; и,

J/r-

I I

J rl-I И :2Л Я2 ШИ ±П 1

I-К/Т Т/ХГ Т/х1} Гх

////Л/}/А II

I

ЛУ///:л-у///////// //х/

Даты

1972-01-01—Публикация