Изобретение ОБНОСИТСЯ к области за1П101МИ«ающих устройств.

Известно вычислителыно-логичеокое устройство, содержащее магнитный оперативный «акопитель и-нформации ic разрядными ш-инами, усилители воопроизведения; подключеи«ые через соответствующие диоды .к регистру регенерации, матрицу магнитшых сердечников с прямоугольной тетлей гистерезиса ППГ, прошитых взаимно перпеядикулярными адресными ,и разрядными.(шина.ми, а т.акже первыми и ютюрыми Диагояалънььми шияами, два рбверсивиых дещифратора, регистр сдвигателй. Однако эти устройства имеют сложную конструкцию и малую юкорость работы.

Олисываевдое устройство отлич1ается от известного т€м, ЧТО разрядные шины матрицы подключены одними iKO.HuaiMH к соответствующим шходам усилителей воспроизведения, .адресные шины матрицы подсоединены к выходам регистра сдвигателя, в.ходы которого через соответствующие диоды соединены с выходами усилителей восироизведения, а первые .и вторые диагональные ш-ины матрицы подключены 100ответстве(нно к юыхода м перBOiPO ,и второго реверсивных дешифраторов.

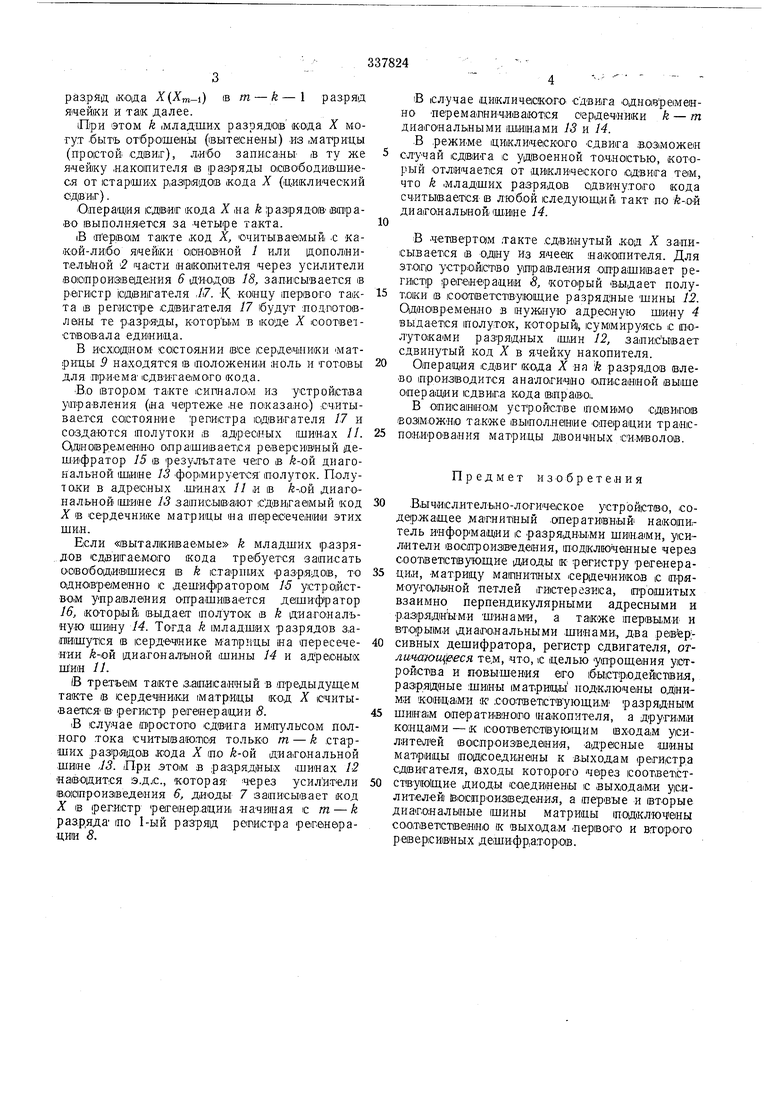

Оно содержит матеитный оперативный накошитель, состоящий из основной 1 и дополсчительной 2 частей с разрядными щинами 3 и адресными :щинами 4, подключенными к дешифратору 5 адреса, усилители воспроизведения 6, иодключенные через диоды 7 к регистру регенерации 8, матрицу 9 магнитных сердеЧ1НИ1Ков 10 с ППГ, прошитых взаимио пер1пенди1куля1рными адресными Ы и разряднымИ 12 1шинами, а также первыми 13 и вторыми 14 диагональными шинами, подключанными к первому 15 и BTopoiMy 16 реверсивным дешифраторам.

Шины 13 подключены одними концами к шинаМ 5 и другими - к усилителям воспроизведения 6, щины 11 (Присоединены к выходам регистра сдвигателя 17, входы которого связаны через диоды 18 с выходами усилителей

воспроизведения 6.

Рассмотрим работу устройства на прИмере сдвига кода X на /С разрядов вправо.

Сдвиг двоигаНОго т- разрядно1по кода Х:Хт... Xi, записанного в одну из ячеек основной /

иши дополнительной i2 части ,на.ко1пителя на k разрядов вправо состоит в том, что код X должен перезаписаться в какую-либо ячейку накопителя так, что1бы самый: старший разряд кода Х(Хт) оказался записанным в/п - k

разряд «ода X{Xm-i) в т - k - I разряд и так далее.

этом k младших разрядов кода X могут бытъ отброшены (|вытесне ны) из .магрицы (простой сдвиг), либо записаны в ту же ячейку ,н.ако1пителя в разряды 01С1ВОбоди1Вши.еС.Я от старших р,азрядо1В «ода X (|Ц,и«лический

СДВИ1Г) .

Операция сдвиг «ода X яа k разрядов агор аво выполняется за -четыре та«та.

iB inepBoiM та«те «од X, очитыва-емый с ка«ой-лябо ячейки оюновН.ой 1 или дошолнител Ыной 2 части накотителя через усилители (востроиеведеяия 6 диодов 18, запи1сывается в регистр сдвигателя ,/i7. К концу |пер(вого такта IB регистре сдвигателл 17 будут лодпотовл&Еы те разряды, котором в «оде X соответствов-ала едиивца.

В исходном состоялии все сердеч1ни«и матрицы 9 наиходятся в положении моль и тотовы для лри-ема сдвитаемого «ода.

Во втором такте сигналОМ из устройства управления («а чертеже ,не по«аза;но) считывается состояние репистра сдвигателя 17 и создаются полутоки ,в адресных шии.ах //. Одновременно опрашивается реверсивный дешифратор 15 в результате чего в й-ой диагональной шине 13 формируетсяоолуток. Полутоки в адресных шинах 11 и в й-ой диагональной шине 13 записыВа;ют 1СДвИ|Гае1мый код X в сердечнике матрицы на пе1ресече;НИ1И этих шин.

Если «выталкиваемые k младших р,азря, дов сдвигаемого кода требуется записать освободившиеся в k старншх разрядов, то одновременно с дешИфратор01М 15 устрой ствогМ управления опрашивается дешифратор 16, который выдает полуток в k дяагояалъную шину М. Тогда k младших разрядов з,аоишутся в сердеч1нике матрицы на пересечении k-ofi диагональной шины 14 и адресных Шин 11.

(В третьем такте записанный в предыдущем такте в сердечнИКИ матрицы код X считывается вчретистр регееерации S.

iB случае простого сдвига импульсом полного тока считываются только т - k старших разрядов кода X то k-ofi диагональной шине ,13. При этом в разрядных шинах 12 наводится ЭД.С., «оторая через усилители во1С1произведения 6, диоды 7 записывает код X IB регистр раганер.ациИ начиная с т - k разр,яда по 1-ый разряд регистра регенерации 8.

iB случае ци«личаско го сДввга одновременно перема1пничива1ются сердечники k - т диагональными шин.ами 13 и 14.

В режиме циклического сдвига возможен случай сдвига с удвоенной точностью, который отличается от циклического сдвига тем, что k младших разрядов сдвинутого кода считыв.ает1ся в любой следующий такт по fe-ой диагональной шине 14.

В четвертом .такте сдвинутый код X записывается в одну из ячеек накопителя. Для этого устройство управления опрашив,ает регистр регенерации S, который выдает полутоки в соответствующие разрядные шины 12. Одновременно в 1нуЖ|Ную адресную шину 4 выдается полуток, который, суммируясь с полутоками разрядных шин 12, записывает сдвинутый код X в ячейку накопителя.

Операция сдвиг кола X ня k разрядов влево производится аналогично описанной выше операции сдвига кода впраВО:.

В описа1Н1НО,м устройстве помвмо сдвигов ВозможНЮ также выполнение операции транспо;н.ирования матрицы двоичных символов.

Предмет изобретения

.Вычислительно-логическое устройство, содержащее 1а пнитный .оперативный накопиг тель информации с раз.рядными ши1Н.ами, усилители воспроизведения, подключанные через соответ1ст1вующие диоды к регистру регенерации, -матрицу ма1лниТ1ных сердечников с прямоугО|Л.ыной петлей гистерезиса, прошитых взаимно перпендикулярными адресными и р.азряд1Ными шинами, а также перв.ы,м-и и вторыми диатональЕЫми .шинами., два рев р;сивных дешифратора, регистр сдвигателя, отличающ&еся те,м, что, с целью упрощения устройств.а и пов.ыш-ения его |быстр1одей|ст1вия, разрядные шин-ы матрицы подключены одними концами ж с-оот1ветст1Вующи.М разрядным

шинам оперативного (накопителя, а другими концами-к соотве-тст1вующим входам усилителей воспроизведения, -адресные ши.ны матрицы подсоединены к выходам регистра сдвигателя, входы которого через сооТ(Вет1Стствую1щи-е диоды соединены с .вьгаодами усилителей воспроизведения, а первые и вторые диагональные шин.ы матрицы 1п-01дключ1е1ны соответ1Ств-ен1Н|0 к выходам первого и вггорог-о р ев ере ивных деши-фр,аторОВ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU280547A1 |

Даты

1972-01-01—Публикация