ПРЕОБРАЗОВАТЕЛЬ ВРЕМЕННОГО ИНТЕРВАЛА В КОД

РЬобретение относится к области вычнслительной техники и может быть попользовано в устройствах автоматики и вычислительных ЗСтройсгвах.

Известные П1реобр.авовател1И временного интервала в код, содерж-ащие устройство управления, устройство рларешения, генератор счетных ИМПульсов, овязанный через ключ со счетчиком, выходы которого через схемы совпадения и блок памяти лодключены ко входу блока вывода результатов преобразования, имеют низкие функциональные возможности и ,не могут преобразовывать одновременно несколько временных интер|В-алов.

Для устранения этих недостатков п едлагаемый П|реобразователь содержит в каждом канале триггер основной памяти, триггер очередности, триггер дополнительной памяти, причем ед-Иничиые и нулевые входы ipoirrepoi; основной памяти соединены с шииами из.меряемых сигналов, управляющий вход - с выходом генератора счетных импульсов. едш1нчный выход которого подключен к единичным входам триггера очередности и триггера дополнительной памяти и ко входу устройства разрешения, другие входы триггеров очередности соединены с -выходами устройства управления, единичный выход триггера очередности подключен к единичному входу триггера дополиительной памятщ, другие в.коды

которого подключены к выходам чтройства управления, а выход триггера данолнмтельной памяти соединен со входом блока .

Для повышения помехоустойчивости преобразователь содержит схему блокировки, BI Iполненную в виде элемента «И-HF,T, одик вход которого подключен к выходу Зстройства разрешения, другой - к выходу устройства управления, а выход соединен со входами триггеров ocHOBHOii памяти.

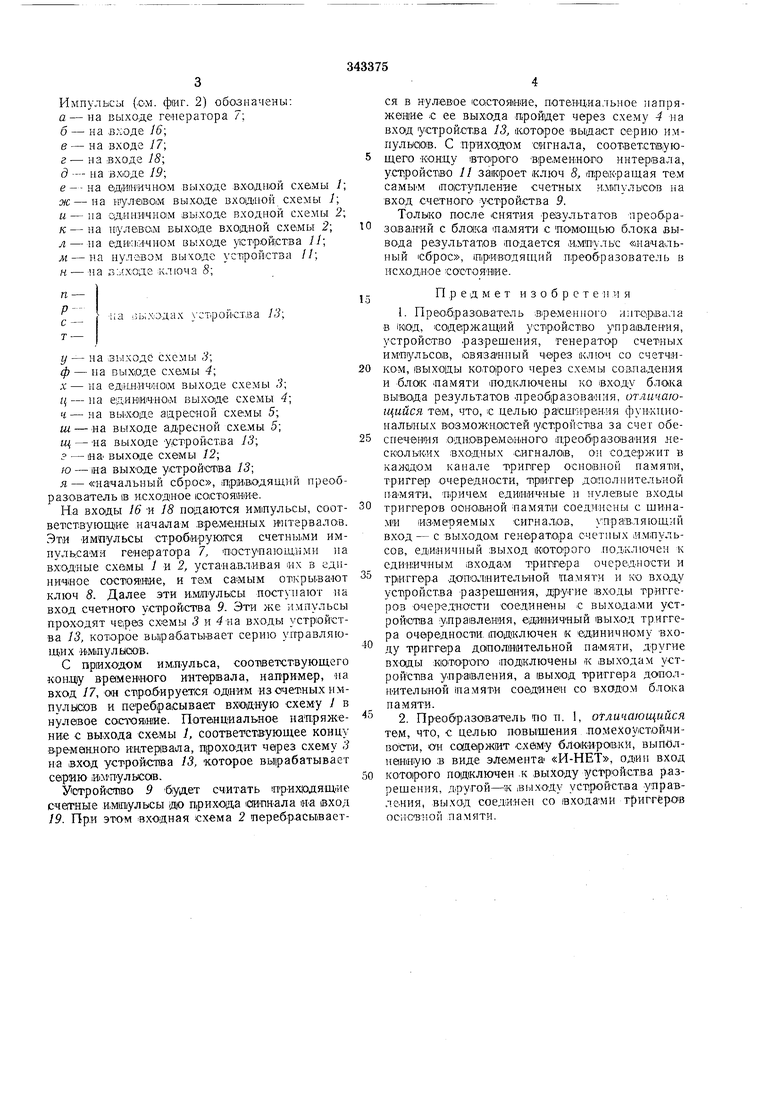

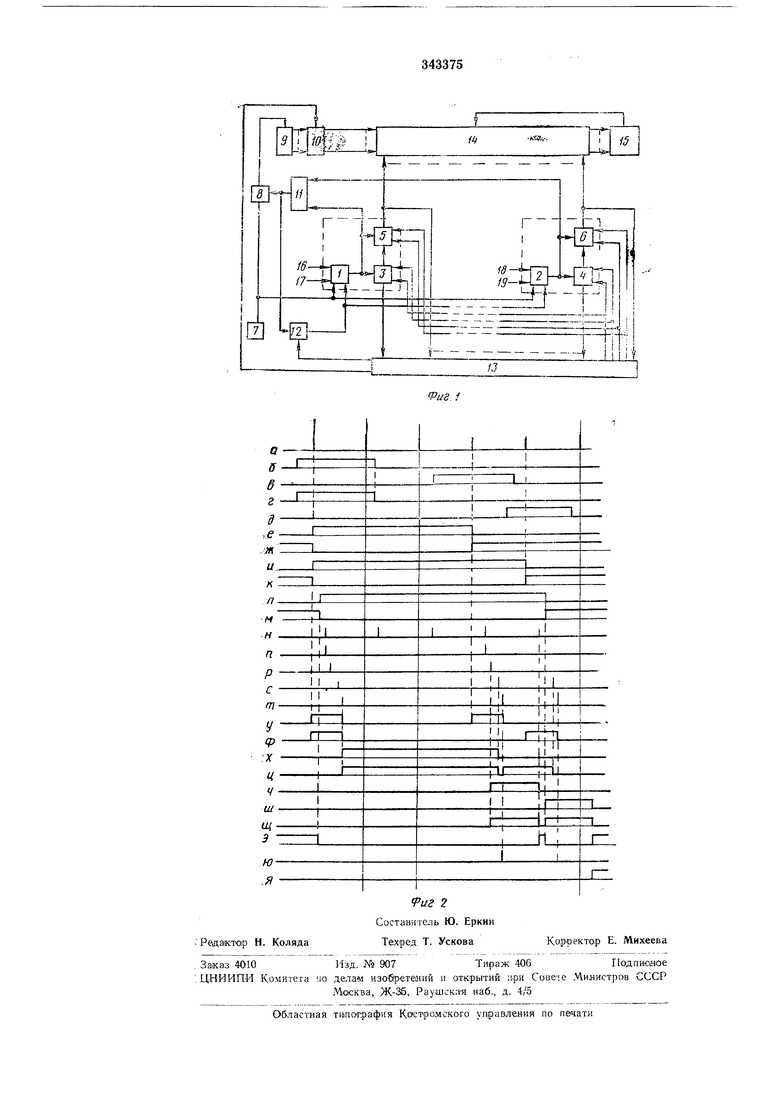

На фиг. 1 дана блок-схема П|редлагаемого преобразователя; на фиг. 2 - времениая диаграмма.

Входная часть преобразователя разбита на каналы, число которых соответствует миинмалыюму количеству одновременно преобразхсмых вре.ме-нных интервалов.

В каждом канале имеются входные схемы 1 и 2, схемы очередности 3 ii 4, адресные схемы 5 и 6, генератор 7 импульсов, ключ 6, счетное устройство 9, схема 10 совпадения, устройство // разрешения, 12 блокировки, устp oiicTBO 1-3 ун1ра;в;1е 1ия. блок 14 памяти, блок 1г вывода резул1)Татов, вход 16 для сигнала, соответствующего иачалу временного интервала I, вход 17 для сигнала, соответствующего концу временного интервала I, вход 18 для сигнала, соответствующего иачалу временного интервала II, вход 19 для сигнала, соотвегствуюи его конду врел енного интервала П.

пульсы {,ом. фиг. 2) обозначены;

на выходе ге нератора 7;

на входе 16;

на входе /7;

на входе 18;

на входе 19;

на единичном выходе входной схемы /;

на нулевом выходе вход|ной схемы 1;

на здлничном выходе входной схемы 2;

на Н1уле.во1М выходе входной схемы 2;

на едишйчном выходе устройства 11;

на нулевом выходе устройства //;

на заходе ключа S;

на выходах ст1ройс.т.ва

у -- на выходе схемы 3;

ф - па выходе схемы 4;

X - на едид.ич1Н01М выходе схемы 3;

ц - па един1И Чно.м выходе схемы 4;

ч-на выходе адресной схемы 5;

ш -на выходе адресной схемы 5;

щ -на выходе устройства 13;

г - на выходе схемы 12;

ю - на вых-аде устройоива 13;

я - «начальный сброс, лри.водящий преобразователь IB исходное состояии-е.

На входы 16 И 18 подаются им1пульсы, соответствующие началам ,в:рем«,н;ных интервалов. Эти ИМпульсы строби-руются счетными импульсами генератора 7, поступа1ош.,кмп на входные схемы 1 и 2, уста-навливая их в еднничйое состюяиде, и тем самым открывают ключ 8. Далее эти импульсы постунают на вход счетного устройства 9. Эти же лмпульсы проходят чйрев схемы 3 и на входы устройства 13, которое вы|раб.аты.вает серию уггравляющих ймяульюоВ.

С приходом имлульса, соответствующего КОП.Ц1У врвмениОГО интервала, например, «а вход 17, он ст(роб«руется одним из счетных нмпульшв и nepedipacbiBaeT входную схему I в нулевое соохзяиие. Потенциальное напряжение с выхода схемы 1, соответствующее концу времеаного интервала, проходит через схему 3 на вход устройСтва 13, которое вырабатывает серию импульсов.

Устройство 9 будет считать стр-ихюдящйе с-чеггные имгаульсы до прихода (СИПнала jia вход 19. Пр.и этОМ входная схема 2 перебрасывается в нулевое состояиие, потенциальное 1апряжеаие с ее выхода пройдет через схему 4и а вход устройства 13, (которое выдаст серию импульсюв. С приходом сигнала, соот.вет.ст1вую5 щего -кояцу второго временно го интервала, устройство 11 закроет ключ 8, (Прекращая тем самыМ 1по|ступление счетных ргмпульсов на вход счетного устройства 9.

Только после снятия результатов преобра зовадаий с бло1к.а памяти с помощью блока вывода результатов подается импульс «ашчааьный сброс, 1П1р«водящнй преобразователь в н с хо дно е :с осто Яни е.

-П р е д м е т и 3 о б р е т е н и я

1. Прео.бразюв-атель В1ремен110ГО HiiTepBana в , содержащий устройство упра1вления, устройство разрешения, генератор счетных импульсов, овязащпый через ислюч со счетчиком, выходы которого через схе.мы совладения и бл:01к памяти .подключены ко iвxoдy блока вывода результатов .преобразования, отличающийся тем, что, с целью расигирвния функциональных всзможН;01Стей устройства за счет обе5 снечения одноврембННого лреобраЗавания нескольких входных сигналО1В, он содержит в каждом канале триггер основной памят1И, триггер очередности, триггер дополнительной паМяти, -причем единичные и нулевые входы

0 триггеров ооНОв.ной памяти соединснь с шипами иЗМеряемых сигналов, управляющий вход - с выходОМ генератора счетных импульсов, единичный выход которого подключен к единичным входаМ триггера очередности и

триггера дополнительной памяти и ко входу успройства разрешения, другие входы триггеров Очередн;асти соединены с выхода;ми устройства управления, еданичный выход триггера очередности. (Подключен к единичному входу триггера даполмительной наМятн, другие входы .кюфоропо подключены к выходам устройст|ва УПрайления, а выход триггера допОлНИТельной памяти соединен со входом блока памяти.

2. Преобразователь но п. 1, отличающийся тем, что, с целью Повышения помехоустойчивости, он со(Д©ржит схему бЛ01КИрО(вкй, выполненную 3 виде эл-емента «И-НЕТ, одип вход

0 KOToiporo подключен .к выхОДу устройства разрешения, другой-к ,в1.1хоДу устройства управления, выход соединен со входаМН триггеров о СИ ев 1 о и п а .м яти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь временных интервалов в код | 1977 |

|

SU683018A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Устройство допускового контроля параметров | 1991 |

|

SU1800380A1 |

| Устройство допускового контроля параметров | 1991 |

|

SU1798719A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство для охранной сигнализации | 1990 |

|

SU1783561A1 |

| Устройство для обработки экспериментальных данных | 1982 |

|

SU1206811A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

Авторы

Даты

1972-01-01—Публикация