Изобретение относится к области вычислительной техники и предназначено для построения устройств управления в цифровых вычислительных машинах.

Известны распределители импульсов, содержащие потенциальные триггеры, соединенные друг с другом через линии задержки и схемы совпадения, причем для построения этих устройств требуется источник тактовых импульсов и как минимум по одной линии задержки и схеме совпадения иа разряд.

Предложенное устройство отличается тем, что единичные выходы всех триггеров соединены соответственно с нулевыми входами предыдущих триггеров, а единичные выходы нечетных триггеров подключены через инверторы к входу линии задержки, выход которой соединен с вторыми входами четных схем совпадения непосредственно, а со входами нечетных- через инвертор.

Это позволяет упростить устройство.

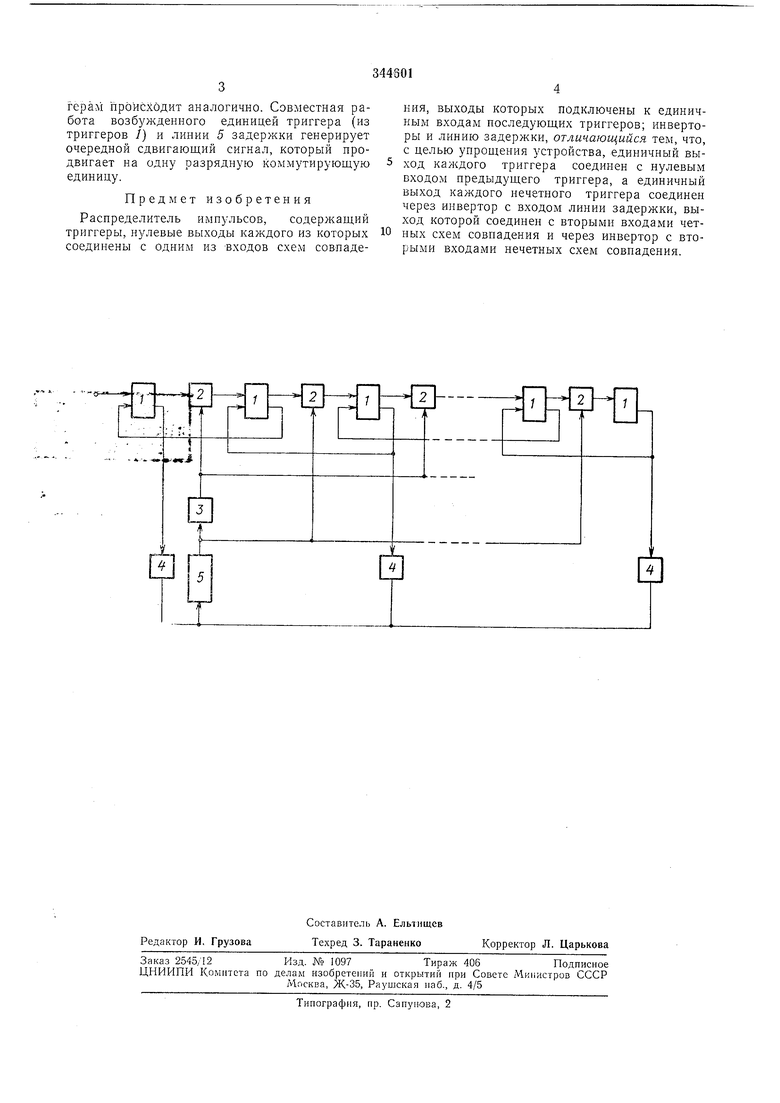

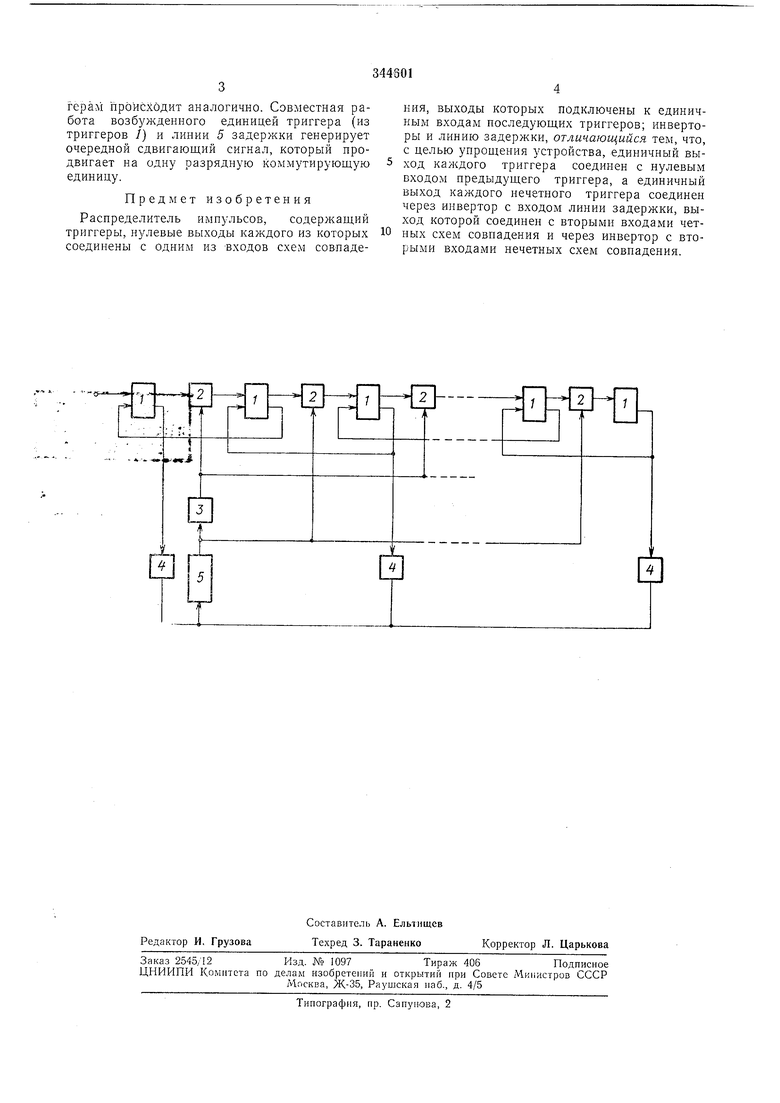

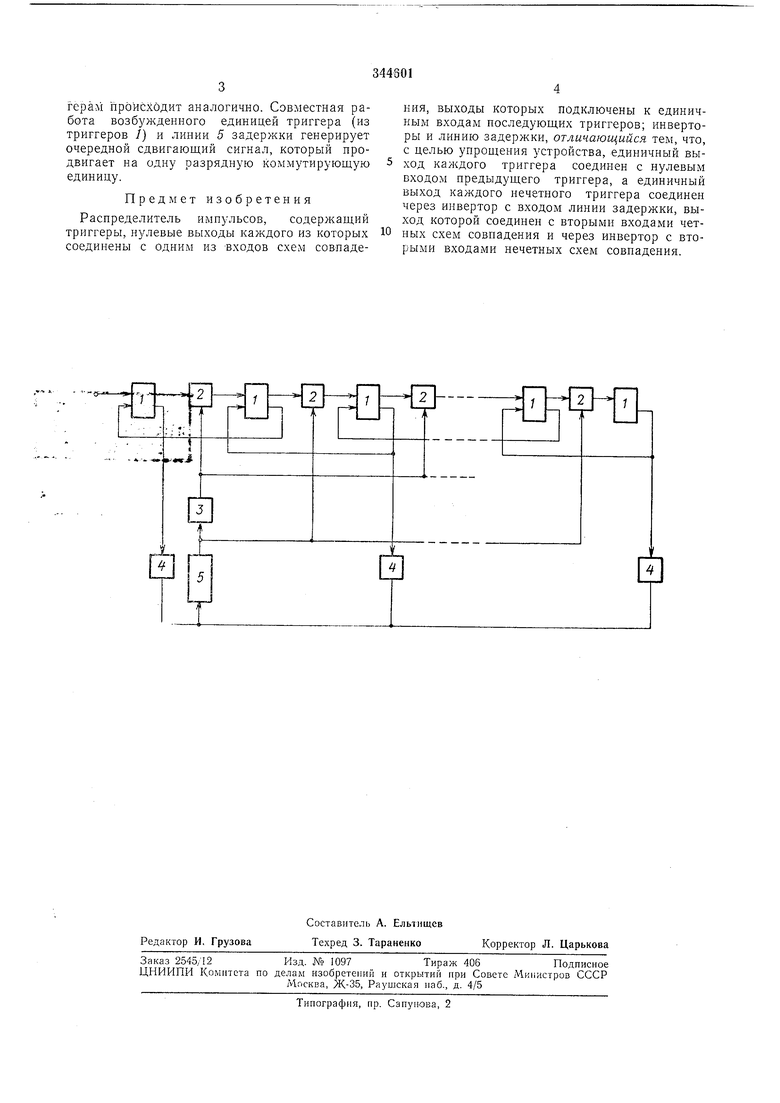

Па чертеже показана схема распределителя импульсов.

Она содержит триггеры 1, схемы 2 совпадения, инвертор 3, развязывающие инверторы 4, линию 5 задержки.

Устройство работает следующим образом.

рающий, но все схемы совпадения заперты по первым входам, подключенным к выходам триггеров 1.

Запускающий импульс, приходя на единичный вход первого триггера из ряда триггеров 1, записывает в нем единицу. На входе первой схемы 2 совпадения, подключенной к нулевому выходу триггера, устанавливается разрешающий сигнал, но она заперта по второму входу. Сигнал единицы с выхода первого триггера подается на вход линии 5 задержки и через время, равное времеии задержки последней, поступает разрешающим сигналом на вторые входы всех нечетных схем совпадений и запирающим на четные схемы совпадений. При этом открывается только первая схема 2 совпадения. Сигиал этой схемы совпадения записывает во второй триггер из ряда триггеров единицу, а он в свою очередь - нуль в первый триггер, запирая тем самым первую схему совпадения. Нулевой сигнал с первого триггера проходит на вход линии 5 задержки и через время, равное времени задержки нг этой линии, поступает разрешающим сигналом на вторые входы четных и запирающим сигналом иа входы нечетных схем совпадеиия. Открывается вторая схема 2 совпадения и записывает единицу в третий триггер, а он в свою очередь - нуль во второй триггер, при этом выдает сигнал единицы на вход линии 5 задержки.

герам происходит аналогично. Совместная работа возбужденного единицей триггера (из триггеров /) и линии 5 задержки генерирует очередной сдвигающий сигнал, который продвигает на одну разрядную коммутирующую единицу.

Предмет изобретения

Распределитель импульсов, содержащий триггеры, нулевые выходы каждого из которых соединены с одним из входов схем совпадения, выходы которых подключены к единичным входам последующих триггеров; инверторы и линию задержки, отличающийся тем, что, с целью упрощения устройства, единичный выход каждого триггера соединен с нулевым входом предыдущего триггера, а единичный выход каждого нечетного триггера соединен через инвертор с входом линии задержки, выход которой соединен с вторыми входами четных схем совпадения и через инвертор с вторыми входами нечетных схем совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1967 |

|

SU216130A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Цифровой фазометр | 1982 |

|

SU1027638A2 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ ИМПУЛЬСОВ | 1972 |

|

SU348993A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Пересчетное устройство | 1976 |

|

SU702526A1 |

Даты

1972-01-01—Публикация