Изобретение относится к области цифровой вычислительной техники и может быть использовано в арифметических устройствах электронных цифровых вычислительных машин.,

В известных двухтактных сумматорах параллельного действия для выполнения операций сложения (вычитания) предусмотрены логические элементы для передачи прямого и обратного кодов на счетный вход накаплиБающего регистра, а также для формирования сигналов поразрядного и сквозного переносов. В каждом двоичном разряде этих сумматоров необходимо иметь три элемента «И и два элемента «ИЛИ. Такой объем оборудования в каждом разряде приводит к усложнению сумматора и снижает надежность его работы.

Цель изобретения - упрощение сумматора и повыщение надежности его работы.

Это достигается тем, что в нем шина сложения каждого разряда подключена к входу логического элемента «И, выход которого соединен с входом логического элемента «ИЛИ старшего разряда.

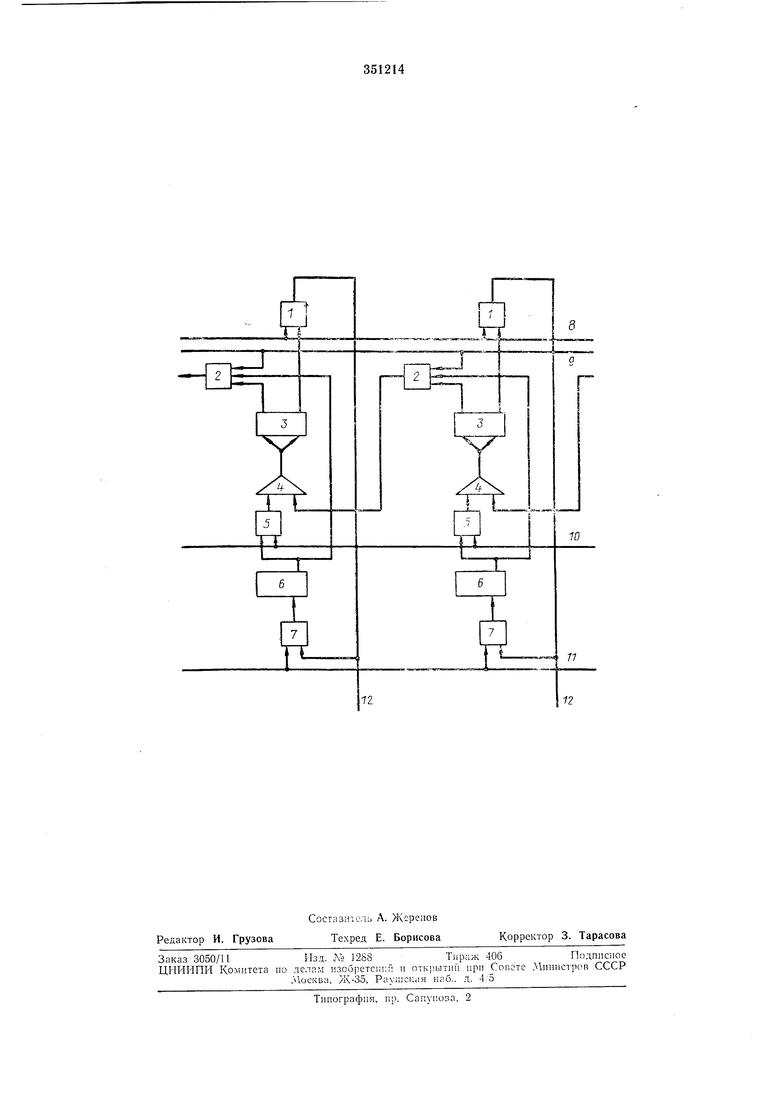

регистра, логический элемент «ИЛИ 4, логический элемент «И 5 триггер 6 приемного регистра, логический элемент «И 7.

В состав сумматора также входят: шина 8 разрешения выдачи кода накапливающего регистра на числовые шины, шина 9 сложения, шина 10 разрешения выдачи кода из приемного регистра, шина/У разрешения приема кода в приемный регистр с числовых шин, числовые шины 12.

Единичный выход триггера 3 подключен к одному входу логического элемента «И. Второй вход этого элемента связан с шиной 8 резрешения выдачи кода. Иулевой выход триггера накапливающего регистра подключен к одному входу логического элемента «И 2, второй и третий входы которого соединены с шиной 9 сложения и единичным выходом триггера 6 приемного регистра. Выход логического элемента «И 2 подсоединен к входу логического элемента «ИЛИ следующего разряда. К другому входу логического элемента «ИЛИ 4 подключен выход логического элемента «И 5 соединенный по входам с шиной 10 разрешения выдачи кода из приемного регистра и единичным выходом триггера приемного регистра. Выход логического элемента «ИЛИ 4 соединен со счетным входом триггера 3 накапливающего регистра.

К «единичному входу триггера 6 приемного регистра подключен выход логического элемента «Pi 7, соединенный но входам с шинами // и 12.

При выполнении операции сложения сумматор работает следующим образом.

Пусть в накапливающем регистре в триггерах 3 хранится код первого слагаемого, а в приемный регистр занесено второе слагаемое. Оба числа положительные.

По первому временному такту осуществляется операция сложения но модулю два. Для этого на щину 10 подается имнульс. Если в триггере 6 любого разряда хранится код единицы, то элемент «И 5 этого разряда открыт и на счетный вход триггера 3 поступает импульс, который производит инвертирование этого триггера.

Далее выполняется операция наложения кодов первого и второго слагаемых. Для этого на щины S и 11 одновременно подаются импульсы. В нриемном регистре получается результат наложения двух кодов (логическое сложение).

На входах триггеров регистров имеются элементы временной задержки импульсов (на схеме они не приведены).

Для формирования окончательного результата сложения на щину 9 подается импульс сложения. Если триггеры какого-либо разряда накапливающего и приемного регистров после первого временного такта находятся в состоянии 01 («О хранится в триггере накапливающего регистра, а «1 - в триггере приемного регистра), то в этом разряде вырабатывается перенос в старщий разряд. Формирование переноса осуществляется с помощью логического элемента «И 2. Имнульс сложения, поступающий на щину Я по цепи логнческих элементов «И 2, «ИЛИ 4 проходит па счетный вход триггера 3 старщего разряда и устанавливает его в нулевое или единичное состояние. Если импульс сложения устанавливает триггер 3 в нулевое состояние, из этого разряда вырабатьгвается сигнал нереноса в

следующий разряд. Когда же триггер 3 сигналом переноса устанавливается в единичное состоянне, то перенос в старщий разряд не вырабатывается.

После распространения сигнала переноса нз младщих разрядов в старщие в накапливающем регистре формируется результат суммирования двух чисел, первоначально расположенных в накапливающем и нриемном

регистрах, а в приемном регистре хранится результат логического сложения первого и второго слагаемых.

Операция вычитания выполняется аналогично операции сложения. Отличие в выполнении

этих операций состоит лищь в том, что до первого временного такта на счетный вход триггеров приемного регистра подается импульс, который инвертирует код приемного регистра. Для упрощения чертежа эта схема

не приводится.

Таким образом, нредложенный сумматор обеспечнвает выполнение операций сложения и вычитания при сокращении оборудования по сравнению с известными устройствами. Для

его построения требуется только два элемента «И и один элемент «ИЛИ. Логические элементы «И / и 7 используются во всех сумматорах, если осуществляется параллельный прием кодов с числовых щин в приемный регистр и выдача кода из накапливающего регистра на числовые щины.

Предмет изобретения

Сумматор параллельного действия, содержащий нриемный триггерный регистр, единичный выход каждого разряда которого соединен через логические элементы «И и «ИЛИ со счетным входом соответствующего разряда накаплнвающего триггерного регистра, отличающийся тем, что, с целью упрощения и новыщения надежности работы сумматора, в нем щина сложения каждого разряда подключена к входу логического элемента «И, выход которого соединен с входом логического элемента «ИЛИ старщего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГОДЕЙСТВИЯ | 1969 |

|

SU240335A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| ДВУХТАКТНЫЙ СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU275527A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| ДВУХТАКТНЫЙ СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1969 |

|

SU238890A1 |

| Накапливающий сумматор | 1976 |

|

SU634276A1 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

Даты

1972-01-01—Публикация