1

Устройство относится к области цифровой вычислительной техники и может быть -использовано в ар«фМетических устройствах электронных Цифровых вычислительных машин.

В известных двухтактных сумматорах параллельно го действия для вьшOv нeния сложеиия и вычита-ния чдасел .предусматриваются логические элементы тила «И для передачи кода «3 приемного регистра на счетньш вход Накапливающего регистра прямым ил,и инверсHbLM кодом. Для формирования сигналов переноса также имеются схемы прямого « инверсного кодов. Наличие в состаВе устройства с.хем формирования .переносов прямого и инверснОГо кодов требует двух логических элементов «И, одной схбМЫ «ИЛИ и формирователя-усилителя на каждый двоичный разряд сумматора.

Известны двухтактные сумматоры, в Которых исключены логические элементы переноса прямого и инверсного йодов, а также ЛОгический Элемент передачи инверсного кода. В этих сумматорах при сложении используются цепи передачи и переноса прямого кода, а код приемного регистра предварительно инвертируется. Для выполнения инвертироваНия требуется дополнительно ко времени суммирОва«ия еще один временной такт, т. в. операции СЛОЖения и вычитания в таких сумматорах выполняются за три временных такта.

Предлагаемый сумматор отличается от известных тем, что шина передач.и инверсного кода соединена со счетными входами триггеров приемного регистра, а сложения

подключена К логическому элементу «И, второй вход которого соединен с шиной переноса из младшего разряда. Это упрощает устройство и повышает его надежность.

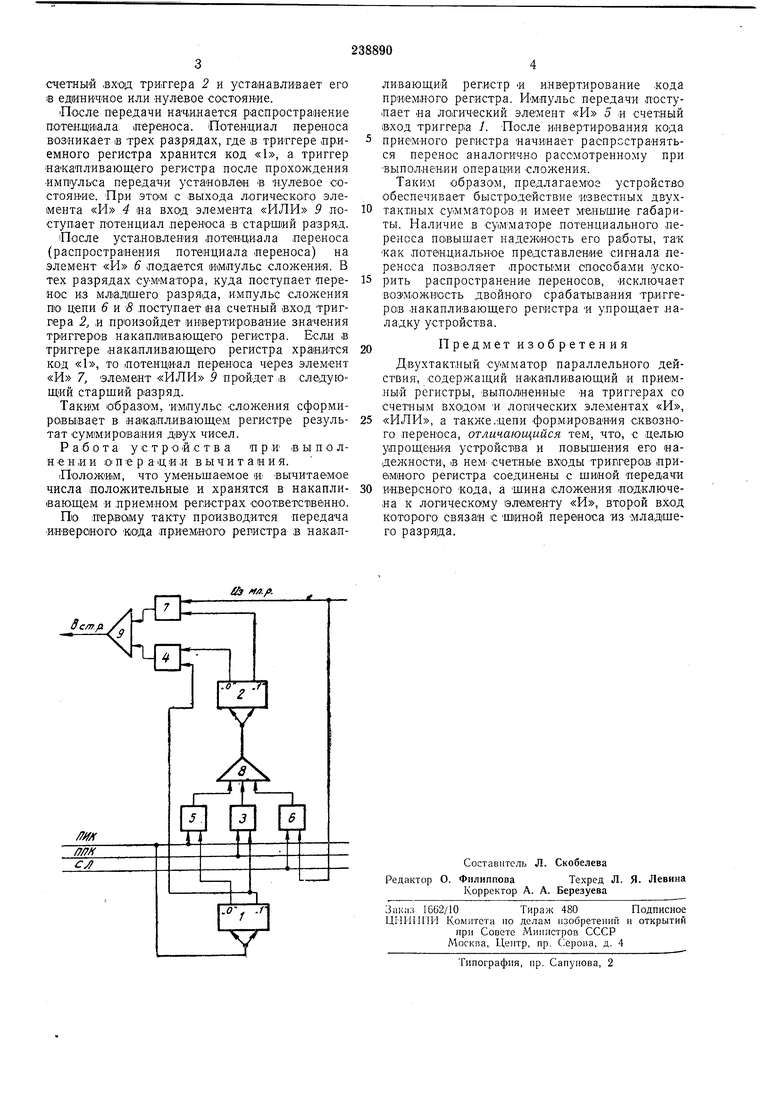

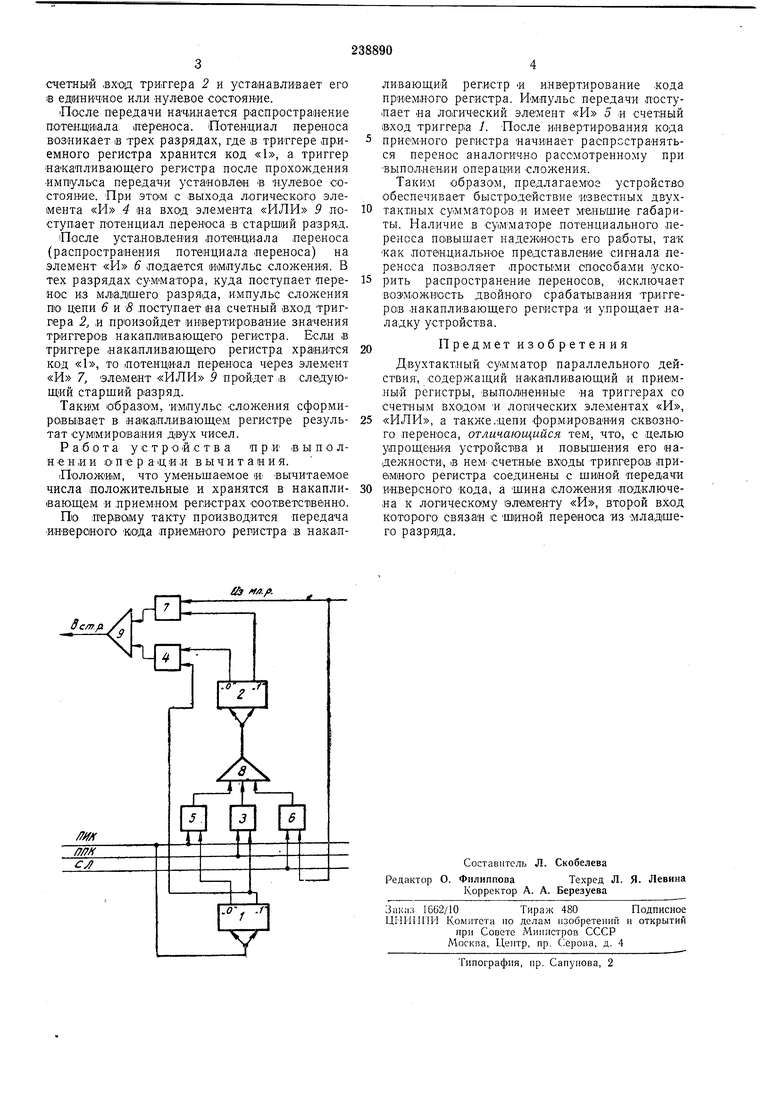

На чертеже приведена функциональная схема одного двоичного разряда двухтактнОГО сумматора. (Линии задержки «а входе триггеров и формирователи-усилители не приводятся.) Схема содержит триггеры /, 2, логические

элсменты «И 5-7 (схемы совпадения), логические элементы «PLII-i 8 и 9 (схемы сборки).

Работа устройства при в ы п о лiH е н ,и и о П е р а ц И: и с л о ж е н и я.

Считаем, что в накапливающем регистре

хранится код первого сла.гаемого, а в приемНОМ регистре записан код второго слагаемого.

Оба числа положительные.

По первому такту производится передача

числа из пр1иемного регистра в наканливаюЩИЙ (сложение по модулю два). Для выполнения этой элементарной операции «а щину передачи прямого кода (ППК) подается импульс. Если в триггере / хранится код «1, то

счетный .вход триггера 2 и устанавливает его 1В единичиое ил.и нулевое состоякие.

После передачи начинается распростраиение потеициала (П-ер-еноса. Потенциал переноса возникает IB трех разрядах, где ,в триггере приемного регистра хранится код «1, а триггер накапливающего регистра после прохождения импульса передачи установлен в нулевое состояние. При этом с выхода логическо.го элемента «И 4 «а вход элемента «ИЛИ 9 .поступает потенциал иереноса в старший разряд.

(После установления ,потен.ци.ала переноса (распространения потенциала переноса) на элемент «И 6 .подается импульс сложения. В тех разрядах сумматора, куда поступает перенос из младшего разряда, импульс сложения пю цепи 6 и -8 поступает еа счетный вход триггера 2, ,и произойдет инвертирование значения триггеров накапливающего регистра. Если .в триггере накапливающего регистра хранится код «1, то потенциал переноса через элемент «И 7, элемент «ИЛИ 9 пройдет е следующий старщий разряд.

Таким о бразоМ, и-мпульс сложения сформировывает в накапливающем регистре результат суммирования двух чисел.

Работа устройства при выполн е н ,и и 01 п е р а щ « и в ы ч и т а н и я.

Лоложим, что уменьшаемое и вычитаемое числа положительные и хранятся в накапливающем и приемном регистрах соответственно.

По первому такту производится передача инверсного Кода приемного регистра в накапливающий регистр и инвертирование .кода приемного регистра. Импульс пере.дачи поступает «а Л0|гический элемент «И 5 .и счетный вход тр.иггер;а 1. После инвертирования кода приемного регистра начинает распространяться перенос аналогично рассмотренному при выполнении операции сложения.

Таким образом, пре.длагаем1ое устройство обеспечивает быстродействие известных двухтактных сумматоров и имеет меньшие габ.ариты. Наличие в сумматоре потенциального переноса повышает надежность его , так как потенциальное представление сигнала переноса позволяет простыми способами ускорить распространение переносов, исключает возможвость .двойного срабатывания триггеров накапливающего регистра и упрощает наладку устройства.

0Предметизобретения

Двухтактный сумматор параллельного действия, содержащий на капливающий и пр.иемный регистры, вы.полненные на триггерах со счетным входом и логических элементах «И,

5 «ИЛИ, а также..цепи формирования сквозного переноса, отличающийся тем, что, с целью упрощения устройства и повышения его надежности, iB нем- счетные входы триггеров приемного регистра соеди.нены с шиной передачи

инверсного «ода, а шина 1сложения подключена к логическому элементу «И, второй вход KOTOpiOro связан с шиной переноса из младшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГОДЕЙСТВИЯ | 1969 |

|

SU240335A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1972 |

|

SU351214A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1972 |

|

SU342186A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| ДВУХТАКТНЫЙ СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU275527A1 |

Даты

1969-01-01—Публикация