Известны арифметические устройства, выполненные 1на логических эледментах и тритге.рах, IB которых для вылолнения операций логическОГО сложения, логического умиожения, .выдачи 1КО|да на числовые ш«,ны вопользуются отдельные логические схемы «И.

Предложенное устройство отличается тем, НТО выход схемы «И, подключенной «о входу устаиоики «О триггера каждого разряда накапливающего регистра, соединен с входом схемы «И, ВЫХОД которой подключен ко входу схемы «ИЛИ, а -выход этой схемы «ИЛИ соединен с числовой шиной.

Это позволяет сократить объем оборудования арифметического устройства и улучшить его характеристики.

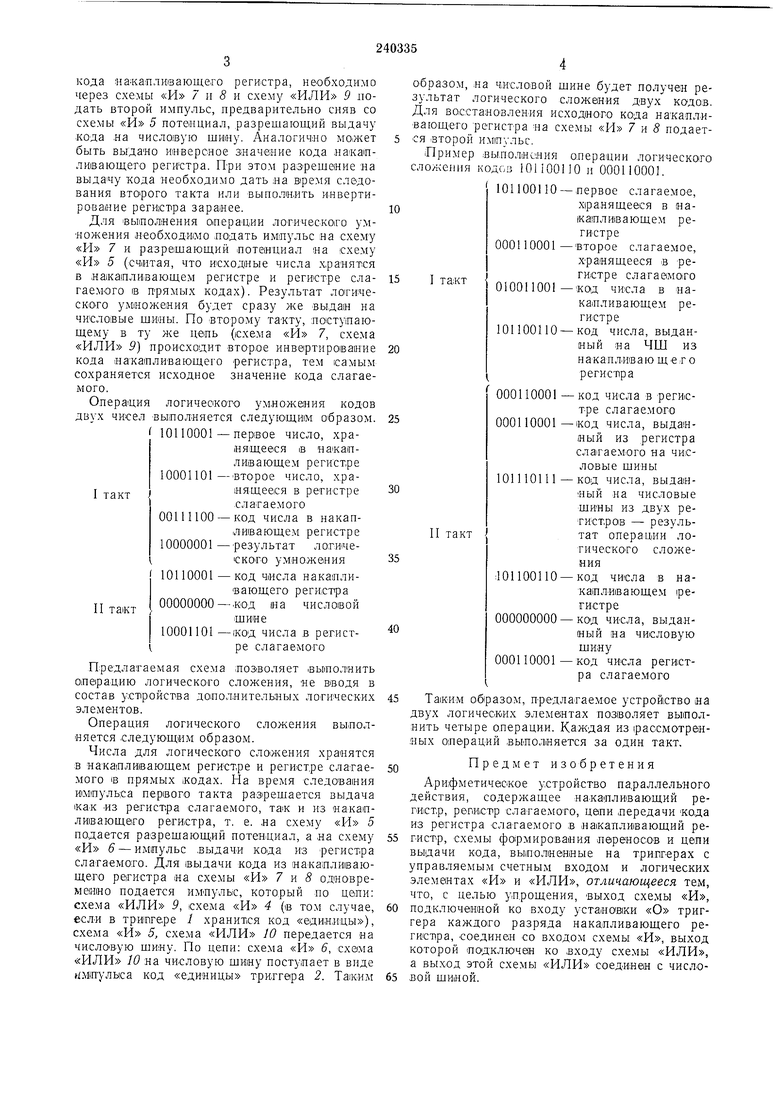

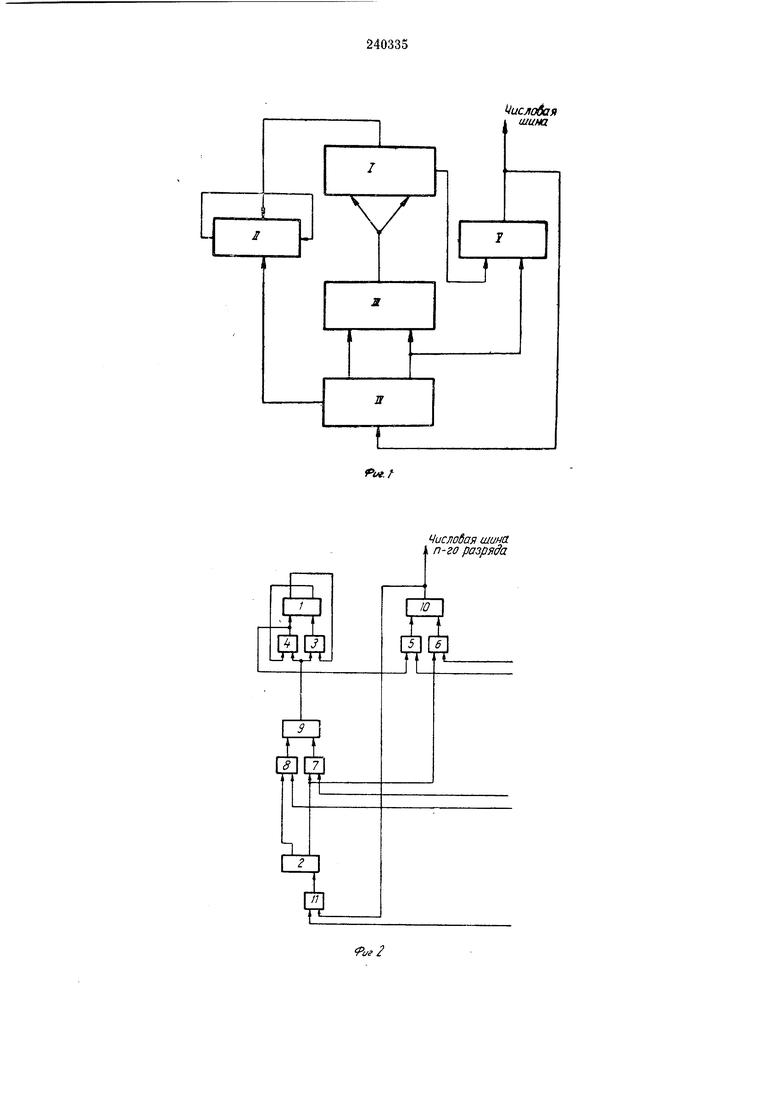

На фит. 1 представлена блок-схема арифметического устройства параллельного действия, где; / - накапливаюш,ий регистр; // - схема переноса; /// - схема передачи кода; IV-регистр слагаемого; V - схема выдачл 1кода на числовые шины; на фиг. 2 - функциональная схема п-го разряда афифметичеокото устройства, где: / - триггер накапливаюш,его .регистра /; 2 - триггер регистра слагаемого IV; 3-S -схемы 9, 10 - схемы «ИЛИ.

Рассмотрим работу п-то разряда арифметинеского устройства пфн выполнении операции выдачи 1кода из накаиливающего -регистра на числовые шины.

Для выполнения этой операции необходимо подать на схему «И 5 потенциал, разрешающий выдачу кода на числовые шины ЧШ, и импульс выдачи кода из регистра слагаемого в сумматор на схему «И 8. Так ка-к в исходном положении триггер 2 приемного регистра слагаемого установлен в пулевое положение, то схема «И 8 будет открыта. В том случае, если приемный регистр не установлен в нулезое положение, то импульсы подаются на схемы «И 7 и S однозременно. Им1пульсы с выходов схем «И 7, 8 через схему «ИЛИ 9 поступают на управляемый счетный вход триггера / (логические схемы «И , 4). Если в

триггере / сохранился код «нуля, то импульс, поступивший со схемы «ИЛИ 9, пройдет через схему «И 3 на единичный вход триггера / и запишет в пего код «единицы. Так как с 1выхода схемы «И 4 на вход схемы «И 5

не иостуиало импульса, то и на числовую шину из рассматриваемого .разряда код не выдавался. В том случае, если до прихода импульса со схе.мы «ИЛИ 9 в триггере / хранился код «единицы, то импульс со схемы

«ИЛИ 9 постулит через схсму «И 4 на нулевой вход этого триггера и на схему «И 5 схемы выдачи кода на числовую шину. Другими словами, ко.д «единицы, хранящийся в триггере 7, будет выдан на числовую ш)ну.

кода .Наскабливающего регистра, необходимо через схемы «И 7 и 8 н схему «ИЛИ 9 подать второй импульс, предварительно сняв со схемы «И 5 поте1ициал, разрешающий выдачу кода на числовую шину. Аналогично может быть выдано инверсное значение кода накапливающего регистра. При этом раз1реше1ние на выдачу кода необходимо дать на В1ремя следования второго такта или выполнить инвертирование реги1СТ1ра заранее.

Для выполнения операции Л0гическо1го умножения необходимо подать импульс :на схему «PI 7 и разрешающий потенциал на схему «И 5 (считая, что исходные числа хранятся в накапливающем регистре и регистре слагаемого IB прямых кодах). Результат ло1ГИ ческОГО умножения будет сразу же выдан на числовые шины. По второму такту, поступающему в ту же цепь (схема «И 7, схема «ИЛИ 9) происходит второе инвертирование кода накапливающего регистра, тем самым сохраняется исходное значение кода слагаемого.

Операция логического умноже,ния кодов двух чисел выполняется следующим образом. ( 10110001 - первое число, хранящееся iB на капливающем регистре 10001101-второе число, хранящееся в регистре

I такт слагаемого

00111100 - код числа в накапливающем регистре 10000001 -результат логического умножения 10110001 - код чнсла накапливающего регистра 00000000-код на числовой

П такт

щине

10001101 -код числа в регистре слагаемого

Предлагаемая схема позволяет выполнить операцию логического сложения, не вводя в состав устройства дополнительных логических элементов.

Операция логического сложения выполняется следующим образом.

Числа для логического сложения хранятся в накапливающем регистре и регистре слагаемого в прямых «одах. Па время следования ишпульса первого такта разрещается выдача как из регистра слагаемого, так и из накапливающего регистра, т. е. на схему «И 5 подается разрещающий потенциал, а на схему «И 6 - импульс выдачи кода из регистра слагаемого. Для выдачи кода из накапливающего регистра на схемы «И 7 и S одновременно подается импульс, который по цепи: схема «ИЛИ 9, схедма «И 4 (в том случае, если в тритгере 1 хранится код «единицы), схема «И 5, схема «ИЛИ W передается на числовую шину. По цепи; схема «И 6, схама «ИЛИ 10 на числовую шину поступает в виде им1пульса код «единицы триггера 2. Таким

бразом, на числовой шине будет получен реультат логического сложения двух кодов. ля восстановления исходного кода накаплиающего регистра на схемы «И 7 и 8 подаетя второй импульс.

Пример выполнения операции логического ожения кодоа 101100110 и 000110001.

101100110 - первое слагаемое, хранящееся в накапливающем регистре

000110001 -второе слагаемое, хранящееся в рет „.,„гистре слагаемого

J такт 010011001-кад числа в накапливающем регистре

101100110 - код числа, выданный на ЧШ из накапливаю щего регистра

000110001 -код числа в регистре слагаемого

000110001-код числа, выданный из регистра слагаемого на числовые шины

101110111 - код числа, выдан ный на числовые шины из двух регистров - резульП такт I тат операции логического сложения

401100110 - код числа в накапливающем регистре

000000000 - код числа, выданный на числовую шину

000110001-код числа регистра слагаемого

Таким образом, предлагаемое устройство на двух логических элементах позволяет выполнить четыре операции. Каждая из paccMOTpeiHных операций выполняется за один такт.

Предмет изобретения

Ари;фметическое устройство параллельного действия, содержащее накапливающий регистр, регистр сла:гаемого, цйпи передачи кода из регистра слагаемого в на1капли1вающий регистр, схемы формирования переносов и цепи выдачи кода, выцо.чневные на триггерах с управляемым счетным входом и логических элементах «И и «ИЛИ, отличающееся тем, что, с целью упрощения, выход схемы «И,

подключенной ко входу установки «О триггера каждого разряда накапливающего регистра, соединен со входом схемы «И, выход которой подключе|н ко входу схемы «ИЛИ, а выход этой схемы «ИЛИ соединен с число ислобаяшина

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU318941A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1972 |

|

SU351214A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

UJ

Числовая шина, п-го разряда

Даты

1969-01-01—Публикация