Изобретение относится к вычислительной технике и .может быть иснользозаио в устройствах Д1;скретиого действия иг логических элементах с едииичныли временными задержками сигнала на выходе относительно момента поступления его на вход.

Известно пересчетное устройство, содержащее логические элементы с временными задержками выход|1Ых сигналов относительно входных, образующие не менее двух последователь 1Ь1х регистров, имеющих разное число разрядов, с выходным логическим элемeнтo ; соедине -: выход старшего разряда каждого регистра. Однако в известиом устройстве каждая кольцевая нересчетная схема использует столько разрядов в регистре, сколько соответствует собственному периоду регистра; в результате устройство получается слишком сложным.

В предлагаемом устройстве, с целью его упрон1ен 1я. каждыГ разряд регистра имеет запрещающую обратную сзязь с входом младшего разряда своего регистоа.

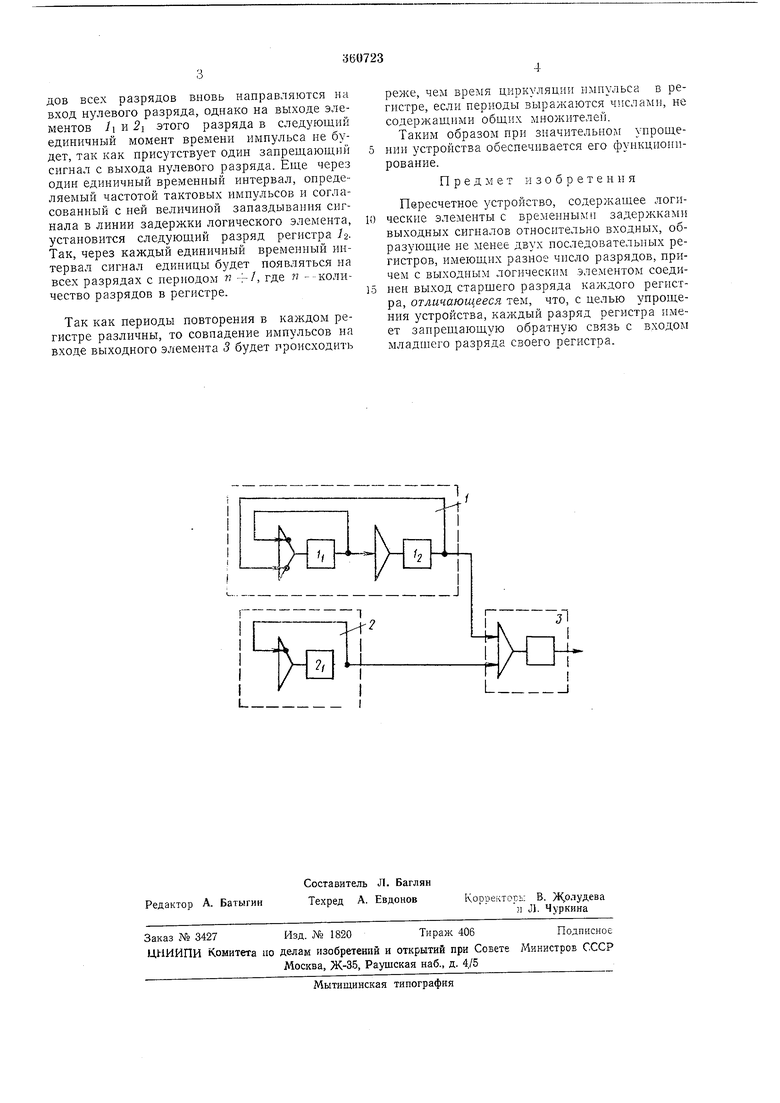

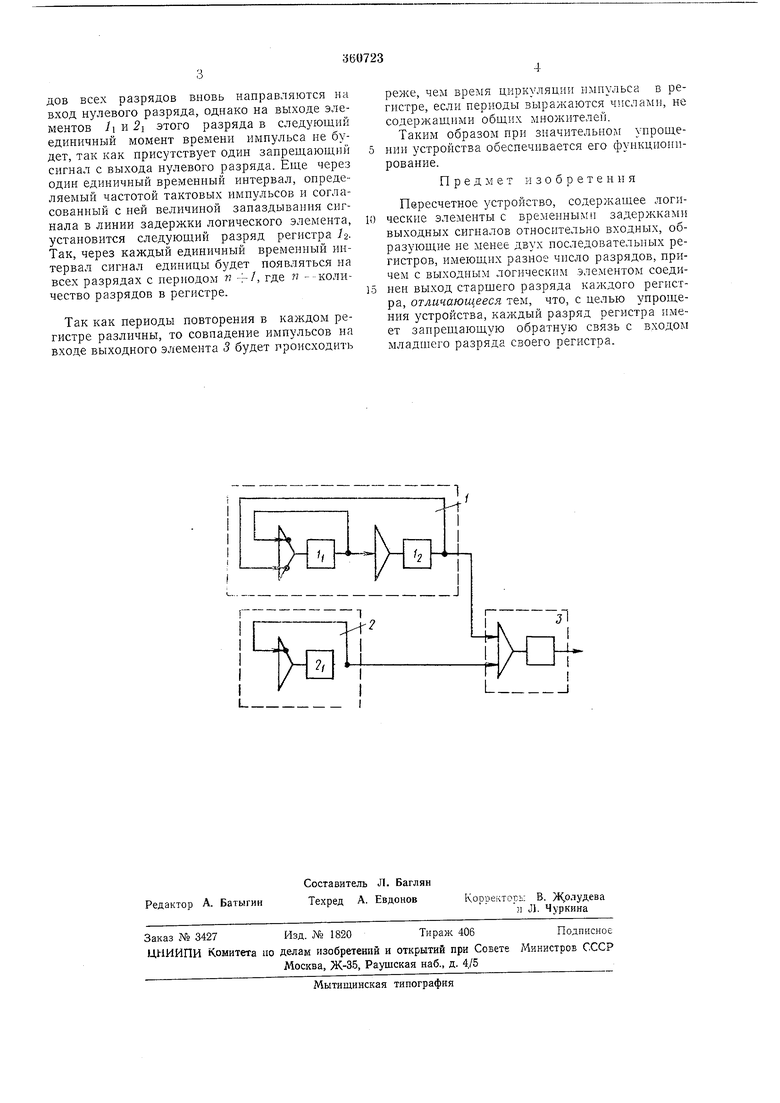

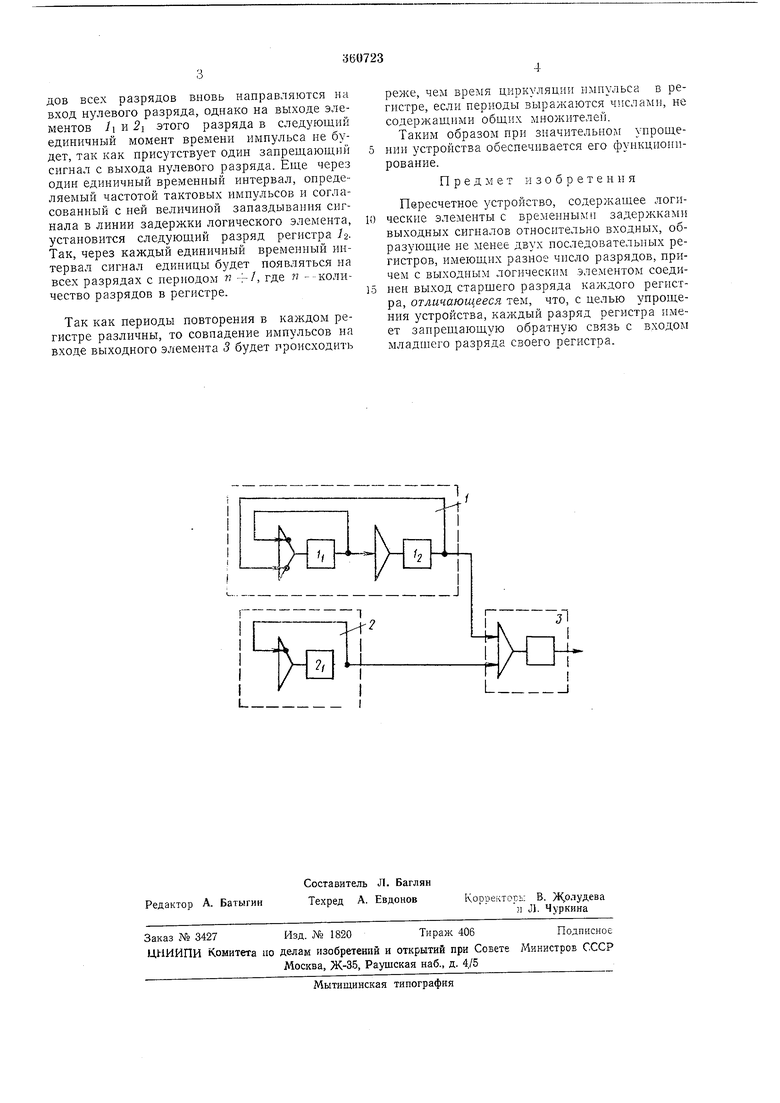

Иа чертеже представлена функциональная

1 и -Л имеющих разное разрядов, представляющих логические элкмер ты /,, /2 и 2i с временными задержками выходных сигналов относнтель1 о входных, и выходной логический 3, подсоедииениый к выходу старшего разряда каждого регнстра по схеме «И. Каждый разряд регпстров имеет запрещающую обратную связь с входом младщего разряда своего регнстра, образуя схему «И - НЕТ. Такое соединение обеспечнвает пере.множснпе простых сомножителей чисел, в которых выражаются периоды повторения импулвсов каждого регистра, если эти сомиожителн не являются обииши для

них.

При включении на все вход), элементов регистров / Н 2 подаются тактовые импульсы or генератора (на чертеже не показан). Прп этом все разряды устапав.чпваются в нулевое

состояние, характеризуемое отсутствием импульсов па выходе.

Для установлення разряда в сост() :.-динииы необходимо присутствие на его входе импульсов. Постуиаюшие такто1 ые импульсы за счет единичиоГ) задержки в каждом разряде и заирещаюи1,ей обратной иадаются с выходом всех разрядов на вход иулевого разряда, соответственно элементов Л Н 2,. На выходе этого разряда через едпнпчнын период появляется сигнал ед1ипи1Ы. так как отсутствуют сигиалы от тех разрядов регистра, которые подключены к его входу запретом.

В момепт появления этого сигиала на выходов всех разрядов вновь направляются на вход нулевого разряда, однако на выходе элементов /1 и 2i этого разряда в следующий единичный момент времени импульса не будет, так как присутствует один запрещающий сигнал с выхода нулевого разряда. Еще через один единичный временный интервал, определяемый частотой тактовых импульсов и согласованный с ней величиной запаздывания сигнала в линии задержки логического элемента, установится следующий разряд регистра , через каждый единичный временный интервал сигнал единицы будет появляться на всех разрядах с периодом г, -г/, где п - количество разрядов в регистре.

Так как периоды повторения в каждом регистре различны, то совпадение импульсов на входе выходного элемента 3 будет происходить

реже, чем время циркуляции импульса в регистре, если периоды выражаются числами, не содержащими общих множителей.

Таким образом ири значительном уирощеНИИ устройства обеспечивается его функционирование.

Предмет изобретения

Пересчетное устройство, содержащее логические элементы с временными задержками выходных сигналов относительно входных, образующие не менее двух последовательных регистров, имеющих разное число разрядов, причем с выходным логическим элементом соедииен выход старщего разряда каждого регистра, отличающееся тем, что, с целью упрощения устройства, каждый разряд регистра имеет запрещающую обратную связь с входом младшего разряда своего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Многоканальный генератор импульсов | 1980 |

|

SU936400A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2004 |

|

RU2260830C1 |

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Устройство для задержки сигналов | 1974 |

|

SU525949A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

J1

1

Даты

1972-01-01—Публикация