Изобретение относится к вычислительной технике и может быть использовано в универсальных и снециализироваи1 ых вычислительных системах, имеющих, например,.магнитное оперативное заноминающее устройство (МОЗУ) с двустуненчатым ден1ифратором адреса (ДА).

Известны различные МОЗУ с нереверсивными и реверсивными дешифраторами.

В этих устройствах одной из возможных неиснравностей является обрыв адресных цепей записи или считывания, нанример, днода дешифрирующей матрицы (прямое сопротивление диода становится недопустимо большим), цричем может выйти из строя как диод, стоящнй в адресной цени записи, так и диод, стоящий в адресной цепн считывания информации.

Такая неисиравность не приводит к полной потере работоспособности МОЗУ, так как возможна замена программным путем неисправного адреса одним из К резерных. Для восстановления работоспособности МОЗУ необходима передача кода, записываемого или хранящегося в неисправном адресе, в резерный, причем в случае выявления неисправности типа «обрыв в адресной цени записи сохранение кода, записываемого в неисправный адрес, осуществляется достаточно просто (например, нутем записи кода в один из резервных адресов). Задача усложняется в случае выявления

выщеуказаннои неисправности в адресной цепи считывания. При этом в неисправном адресе могут храниться как результаты вычислений, для восстановления которых необходимо произвести повторный массив вычислений (в худшем случае начать решение задачи сначала), так и исходная информация, для восстановления которой необходим ее повторный ввод в МОЗУ. И то и другое существенно увеличит время решения задачи, а во многих случаях (работа в реальном масштабе времени) является недопустимым.

Целью описываемого изобретения является восстановление работоспособности МОЗУ в случае возникновения неисправности тина «обрыв в адресной цепи считывания.

Это достигается тем, что выход «нет обрыва блока контроля подключен к одному из управляющих входов ключа считывания, а выход «обрыв блока контроля - к другому управляющему входу ключа считывания, ко входу блока управления и ко входу регистра записи, при этом выход ключа считывания подключен к управляющему входу формирователя записи, а вход опроса - к выходу блока управления.

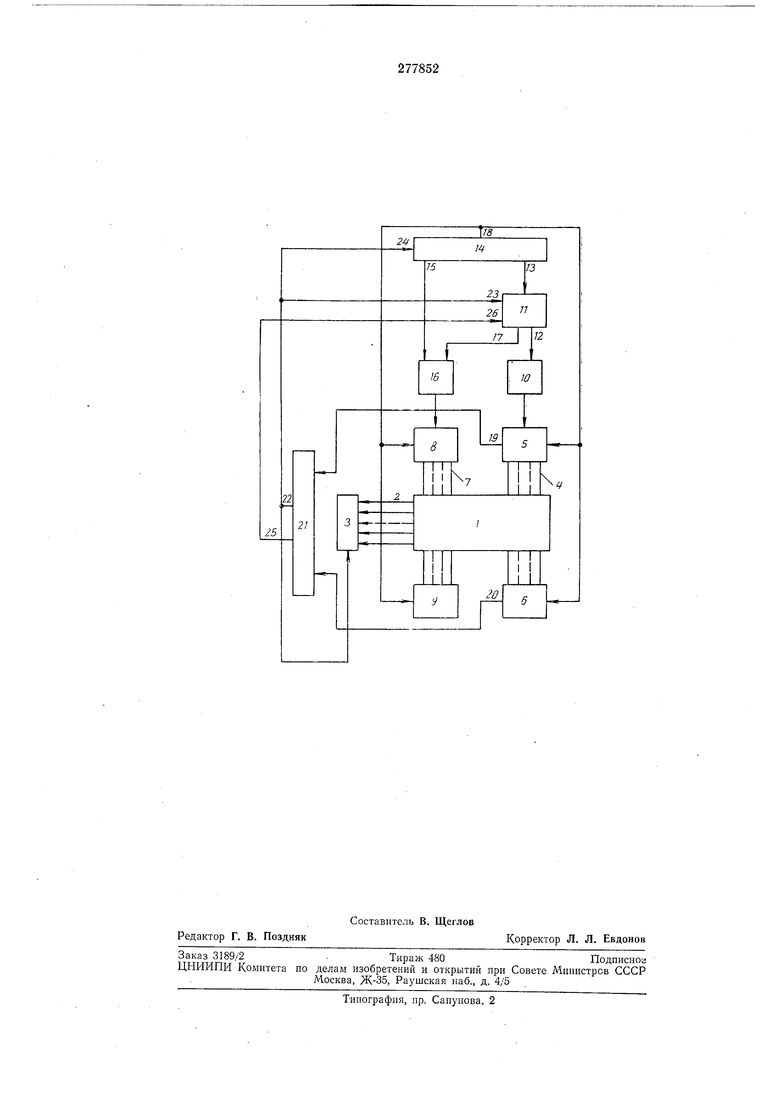

гистру 3 записи, адресные шины 4 считывания подключены к первой ступени 5 ключей дешифратора считывания и ко второй ступени 6, адресные шины 7 записи подключены к первой ступени 8 ключей дешифратора записи и ко второй ступени 9. Первая ступень дешифратора считывания подключена к выходу формирователя 10 считывания, который через ключ // считывания по шине 12 подключен к выходу 13 блока 14 управления. Выход 15 блока управления подключен ко входу формирователя 16 записи, второй вход которого по шине 17 через ключ .11 подключен к блоку 14 управления. Выход 18 блока управления подключен к первой ступени 5 и второй ступени 6 дешифратора считывания, к первой ступени 5 и второй ступени 9 дешифратора записи. Пятая и шестая ступени дешифратора считывания по шинам 19 и 20 подключены к блоку 21 контроля. Выход 22 «обрыв блока контроля подключен ко входу 23 ключа //, ко входу 24 блока 14 управления и к регистру 3 записи, а зыход 25 «нет обрыва подключен ко входу 26 ключа 11.

Работа описываемого устройства происходит следующим образом.

G выходов 13 и 15 блока 14 управления управляюшие сигналы («считывание и «запись соответственно) поступают на формирователи 10 и 16, которые производят опрос детиифраторов считывания и записи. Блок 21 контроля производит контроль наличия «обрыва в адресной цепи считывания накопителя /, и при наличии обрыва в цепи считывания выдает сигнал «обрыв с выхода 22 на ключ 11 блока 14 управления и регистр 3 записи. По этому сигналу блок 14 прекраш.ает нормальную работу и выдает повторный сигнал считывания, который в этом случае через ключ // по шине 17 поступает на формирователь If:. По сигналу через шину 17 формирователь 16 формирует импульс тока, достаточный для считывания информации с адреса накопителя /.

Так как направление тока по адресной цепи записи противоположно адресной цепи считывания, то полный ток от формирователя 16, возбудженного по шине 17, будет намагничивать все сердечники адреса в «1. этом на разрядных шинах чтения будет воспроизведен обратный код храпяш,егося в неисправном адресе слова. Через усилители чтения (предполагается, что они чувствительны к обеим полярностям сигнала) храняшееся в неисправном адресе число окажется записанным в обратном коде на регистр записи.

Сигнал на выходе 22 блока 21, поступая на вход 24 блока 14 управления и на вход регистра 3 записи, обеспечивает последующую запись слова из неисправного адреса, хранящегося теперь уже на регистре 3, в один из резервных адресов. Эта запись должна быть осуществлена с обращением кода. Обращегие кода может быть осуществлено либо обычным путем в логическом устройстве, либо в регистре 3 записи. При отсутствии соответствующих цепей обращения производится обычная запись кода в резервный или любой адрес накопителя, затем этот алЧрес накопителя считывается формирователем 16 по шине 17, и слово из неисправного адреса оказывается записанным на регистр 5 уже в прямом коде, откуда и записывается в нужный резервный адрес.

Предмет изобретения

Запоминающее устройство, содержащее накопитель с разрядной системой чтения и записи, формирователи записи, ключи считывания, регистр записи, блок управления и блок контроля, отличающееся тем, что, с целью восстановления информации при обрыве цепи считывания, выход «нет обрыва блока контроля подключен к одному из управляющих входов ключа считывания, а выход «обрыв блока

контроля - к другому управляющему входу ключа считывания, ко входу блока управления и ко входу регистра записи, при этом иыход ключа считывания подключен к управляющему входу формирователя записи, а вход опроса - к выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| УСТРОЙСТВО РАСПРЕДЕЛЕНИЯ ИНФОРМАЦИИ | 1971 |

|

SU307516A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

Даты

1970-01-01—Публикация