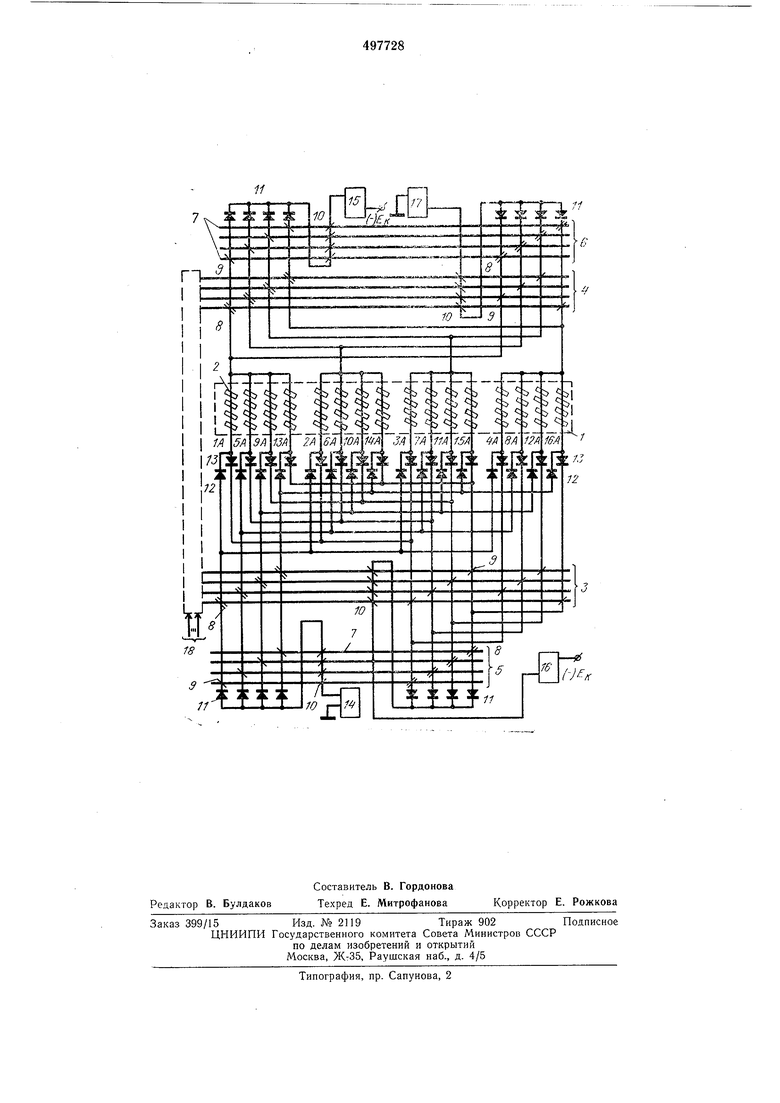

16, 17 тока записи, цепи 18 ввода адреса на ключи считывания. Ключи 3-6 на магнитных сердечниках 7 выполнены по магнитно-диодной схеме распределения тока. На чертеже для удобства чтения показан дешифратор на 16 выходов, по 4 сердечника в каждом ключе дешифратора. Ключи 3-6 образуют разветвленную цепь, каждая ветвь которой содержит многовитковую обмотку 8 магнитного сердечника, обмотку записи 9 и диод 11. Выходы ключа 3 подключены к анодам диодов 12 матрицы считывания, причем к каждому выходу по четыре диода, а к катодам диодов 12 подключены адресные шины. К этим же точкам подключены аноды диодов 13 матрицы записи. Вторые концы адресных щин объединены в четыре группы и подключены к соответствующим выходам ключей 4 и 6. В каждой ветви ключей 3 и 4, образующих цепь считывания дешифратора, включены обмотки 9 записи сердечников ключей 5 и 6, образующих цепь записи дешифратора, причем адрес по цепям считывания на сердечники ключей записи по этим обмоткам подается без изменения. К выходам ключей 5 подключены две группы обмоток 9 записи сердечииков ключа 3. Общие концы этих обмоток попарно соединены и подключены к соответствующим выходам ключа 5. Вторые концы первой группы подключены к катодам диодов 13 матрицы записи, принадлежащих одному выходу ключа 6. При прохождении импульса по одной из этих ветвей на ключ 3 записывается адрес, измененный на единицу. Вторые концы второй группы обмоток 9 на сердечниках ключа 3 подключены к общим точкам катодов остальных диодов 13 матрицы записи. При прохождении импульса по одной из этих ветвей на ключ 3 записывается адрес без изменения. К выходам ключа 6 подключены обмотки 9 записи сердечников ключа 4. При прохождении импульса на одной из ветвей ключа 6 на ключ 4 записывается адрес, измененный на единицу. Для ввода информации в дешифратор непользуются щины 18, содержащие обмотки за-4 ниси сердечников 7 ключей 3 и 4. При обращении к МОЗУ сначала производится подготовка ключей 3 и 4 (ввод адреса в МОЗУ) по шинам 18, при этом в каждом ключе 3 и 4 устанавливается в проводящее5 направление только один сердечник. При опросе ключа импульсом тока, только одна ветвь содержит обмотку сердечника, который будет перемагничиваться по пологому участку петли гистерезиса. В остальных ветвях содер-5 жатся обмотки сердечников, которые будут перематничиваться по крутому участку петли гистерезиса. Эти ветви имеют большой импеданс. Таким образом, подготовка ключа создает в нем одну и только одну проводящую ветвь для6 распредляемо го импульса тока. Предлагаемый дешифратор работает в двухтактном режиме. 1-ый такт - такт считывания, 2-ой такт- такт записи. Для обеспечения соответствующе-6 го режима обмотки 10 устаиовки (установки сердечников в непроводящее состояние) включены последовательно с обмотками 9 записи в цепях считывания и записи, причем число витков обмотки 10 устаиовки вдвое меньше числа витков обмоток 9. В результате прохождения импульса по одной из многовитковых обмоток (ветви) любого ключа, в соседнем (см. схему) ключе, в результате действия импульса тока по обмоткам 9 и 10 остается подготовленным в проводящее состояние только один сердечник; импульс тока устанавливает в непроводящее состояние по обмоткам 10 все сердечники данного ключа, а в проводящее направление по обмотке 9 только один сердечник. В результате ключи 3, 4 и ключи 5, 6 обеспечивают выбор только одной адресной шины. Развязывающие диоды 11, 12 и 13 служат для устранения ложных путей при прохождении отрицательного и положительного импульса (считывание и записи) и для устранения короткозамкнутых контуров при перемагничивании сердечников 7 всех ключей, В режиме считывания запускаются формирователи 14 и 15 считывания. Импульс тока считывания идет от формирователя 14 последовательно по обмоткам 10 установки ключа 5, по одной из ветвей ключа 3 (диоду 11, облмотке 9 записи и многовитковой обмотке 8), через диод 12, выбранную адресную шину, по одной из ветвей ключа 4 (многовитковой обмотке 8, обмотке 9 записи и диоду 11), по обмоткам 10 установки ключа 6 к формирователю 15 и на минусовый выход источника питания. В результате этого на ключи 5 и 6 записи переподается адрес с ключей 3 и 4 считывания без изменения. В режиме записи запускаются формирователи 16 и 17 и импульс проходит последовательно от формирователя 17, через обмотки 10 установки ключа 4 по одной из ветвей ключа 6 (диоду 11 мнотовитковой обмотке 8, обмотке 9 записи, по выбранной адресной шине, через диод 13 одной из двух групп, по одной ветви ключа 5 (обмотке 9 записи, мнотовитковой обмотке 8, диоду 11), через обмотки 10 установки ключа 3 к формирователю 16 и на минусовый выход источников питания. В результате этого на ключи 3 и 4 считывания попадает адрее с ключей 5 и 6 записи, измененный на единицу. Для пояснения рассмотрим случай, когда по шинам 18 в ключах 3 и 4 оказались подготовленными в проводящее направление первые (снизу) сердечники. Импульс тока считывания, проходя по обмоткам 8 первых (снизу) сердечников ключей 3 и 4, проводит подготовку в проводящее направление первых (снизу) сердечников ключей 5 и 6. В данном случае производится выбор первого адреса МОЗУ (1А)- Импульс тока записи, проходя по обмоткам 8 первых (снизу) сердечников ключей 5, 6, обеспечивает также выбор первого адреса МОЗУ (1А) и производит подготовку в проводящее состояние первого (снизу) сердечника

ключа 3 и второго (снизу) сердечника ключа 4. Следующий импульс тока считывания, проходя по обмоткам 8 первого сердечника ключа 3 и второго (снизу) сердечника ключа 4, подготовит в проводящее направление соответствующую цепь записи и произведет выбор 2-го адреса МОЗУ (2А), и т. д. В ключе 3 будет готовится первый (снизу) сердечник,пока импульс записи не пройдет по обмотке 8 четвертого сердечника ключа 6. При этом в ключе 3 будет подготовлен второй (снизу) сердечник, а в ключе 4 - первый (снизу) сердечник. Последующий импульс тока считывания произведет выбор пятого адреса МОЗУ (5А) и т. д.

Таким образом, схема реверсивного дещифратора-счетчика обеспечивает прохождение положительного и отрицательного импульса тока по выбранной адресной шине. Выбор адресной шины происходит в результате соответствующей подготовки сердечников. Первоначально адрес записывается на ключи 3, 4 по обмоткам 18, при дальнейшем обращении к МОЗУ происходит выбор адресов в естественном порядке, т. е. каждый раз выбирается адрее на единицу больший.

Если необходимо обращение к МОЗУ не по счетчику, то по шинам 18 необходимо ввести новый адрес, после чего снова начнется обращение к М.ОЗУ в естественном порядке, начиная с вновь введенного адреса.

Как видно из изложенного, реверсивный дещифратор-счетчик на одних и тех же элементах дешифратора выполняет операции дешифрации и счета адресов за счет введения на сердечники ключей дополнительной системы

обмоток записи и соответствующего подключения этих обмоток к выходам ключей адресного тока считывания и записи.

Предмет изобретения

Дешифратор для запоминающего устройства матричного типа, содержащий ферритовые сердечники, прошитые адресными шинами, источник питания и формирователи тока записи и считывания, подключенные через ключи записи и считывания, выполненные на магнитных сердечниках, к соответствующим адресным щинам, и развязывающие диоды, отличающийся тем, что, с целью повыщения надежности и быстродействия устройства, сердечники ключей прошиты дополнительной обмоткой записи, причем дополнительные обмотки записи каждого сердечника ключей записи включены последовательно с обмотками считывания соответствующих сердечников ключей считывания, дополнительные обмотки записи сердечников первого ключа считывания включены последовательно с соответствующими обмотками считывания сердечников первого ключа записи, а дополнительные обмотки записи сердечников второго ключа считывания разделены на две группы, одни концы обмоток которых соединены попарно и подключены к соответствующим обмоткам считывания сердечников второго ключа записи, вторые концы одной группы подключены к катодам соответствующих развязывающих диодов, аноды которых подключены к первому выходу первого ключа записи, а вторые концы другой группы подключены к общим точкам соединения других развязывающих диодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ДЕШИФРАТОР | 1969 |

|

SU247351A1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРКИ ИНФОРМАЦИИ | 1972 |

|

SU435559A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Реверсивный дешифратор | 1976 |

|

SU604151A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU277852A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЗАПОМИНАЮЩИМ БЛОКОМ | 1973 |

|

SU386441A1 |

| КОММУТАТОР | 1973 |

|

SU385396A1 |

Авторы

Даты

1975-12-30—Публикация

1972-04-17—Подача