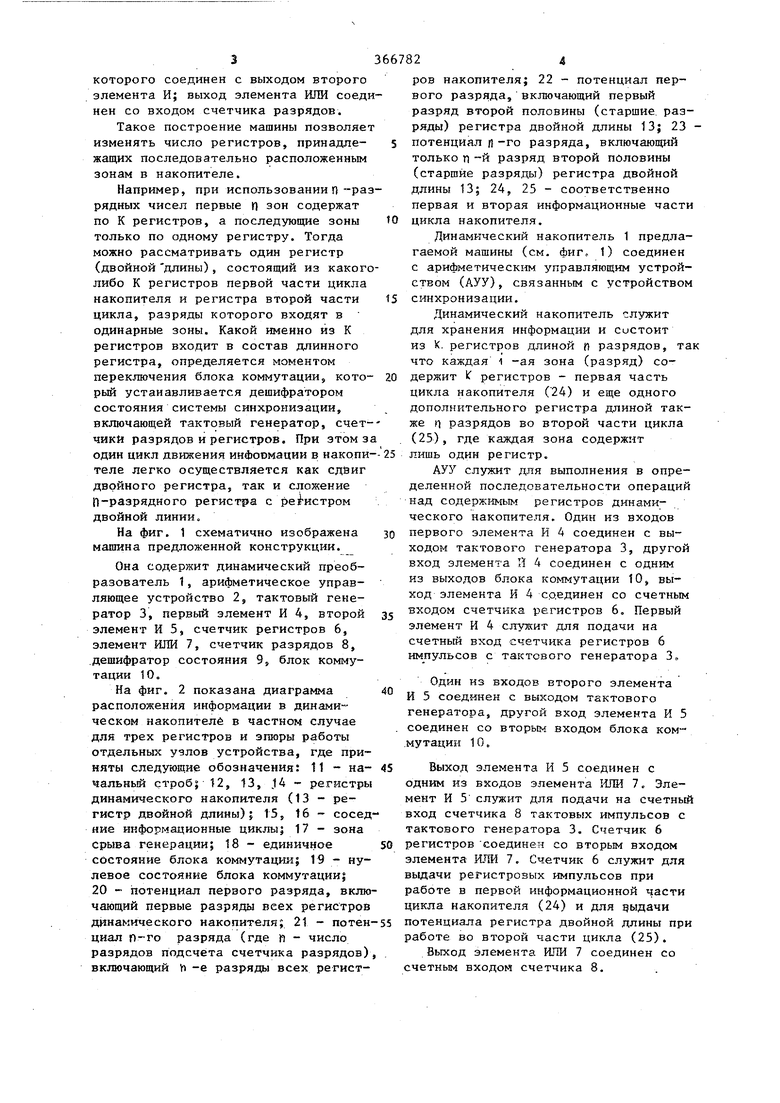

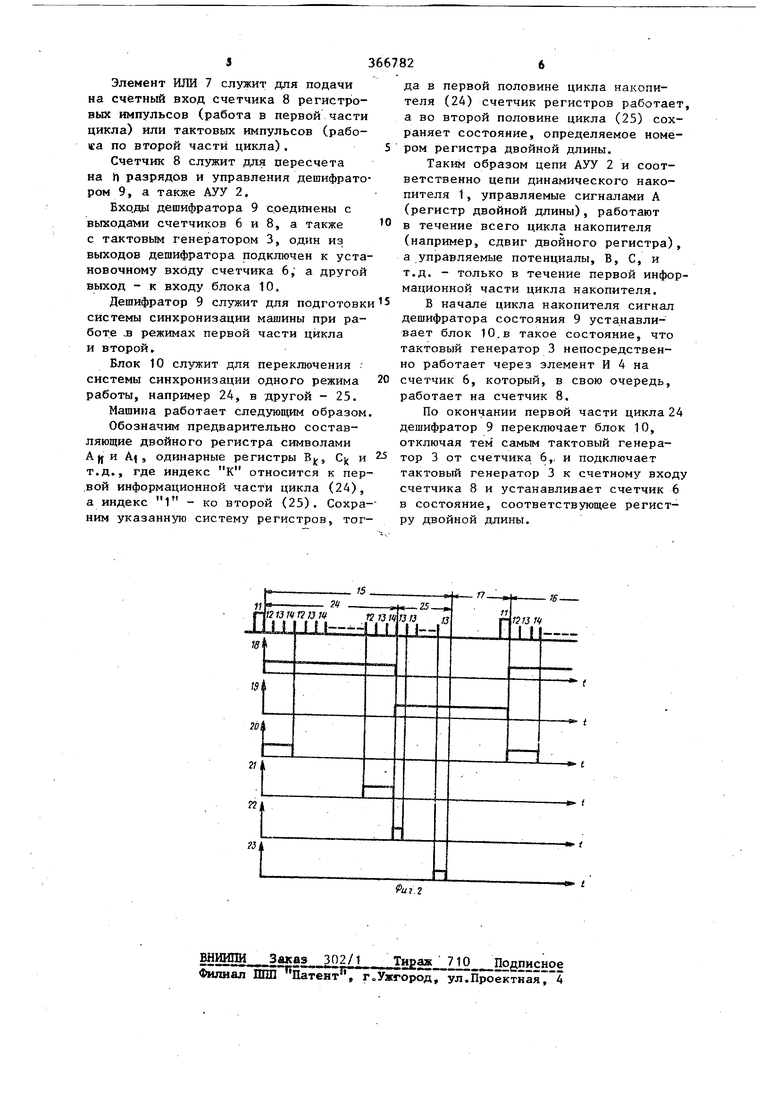

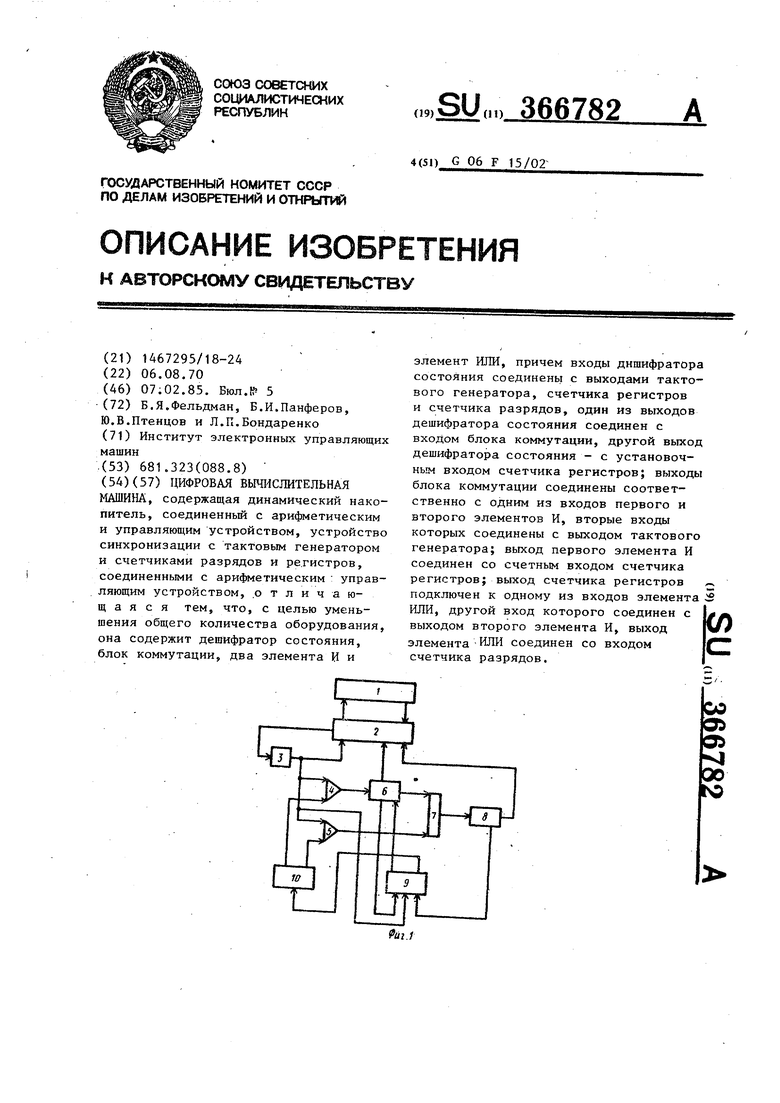

I Изобретение относится к области вычислительной техники и может быть использовано при разработке цифровы машин последовательного типа, в которых регистры выполнены на основ динамического накопителя (магнитострикционные линии задержки, магнит ные барабаны, диски и т„д„). Известны цифровые вычислительные машины, в которых регистры выполнен на основе динамического накопителя, в которых инфррмационяый пакет разделен на зоны так, что в первой зон расположены первые разряды всех регистров, во второй зоне - вторые и т.д. Организация в машине сдвигов информации вправо (т.е. с опережением ранее прошедших через выход накопителя разрядов) связана при наличии в машине нескольких регистров с необходимостью увеличения оборудова ния, идущего на создание сдвиговых цепей, составляющих значительный процент от общего оборудования маши подобного типа. Поэтому в таких машинах алгоритм арифметических операций построены только с испол ьзованием левого сдви га информации. Для выполнения четырех основных арифметических операций (сложения, вычитания, умножения и деления) необходимо иметь один дополнительны регистр (полной или неполной разряд ности в зависимости от алгоритмов операции), При выполнении операций дополнительный регистр вместе с одн из основных регистров образует ре- гистр двойной длины, информация в котором сдвигается одновременно. В известных устройствах дополнительньй регистр расположен аналогич но остальным; каждый 1 -и разряд регистра расположен вместе с -ми разрядами остальных регистров, как описано выше. Организация сдвигов двойного регистра требует в этом сл чае дополнительного оборудования и времени, так как в обычных устройст вах приходится двигать каждую полов ну по очереди. Несмотря на кажущуюся простоту расположения арифметических регистр в накопителе, такая организация АУ име ет следующие недостатки. Во-первых, сдвиг двойного регистра на разряд влево осуществляется за два цикла 2 движения информации в накопителе с промежуточным запоминанием на буферном регистре старшего разряда младшей половины двойного регистра. Другими словами, организация сдвигов такого двойного регистра требует в упомянутых прототипах дополнительного оборудования и времени, так как приходится двигать каждую половину по очереди. Во-вторых, реализация алгоритмов выявления арифметических операций с использованием такого левого сдвига в принципе не требует наличия сплошного регистра .длины 2 (или ц -«- m , где1пл 5 И ) . К примеру, при получении частичных произведений в операции умножения необходимо вести сложение содержимых 2 п разрядного регистра (регистр частичных произведений), и И разрядного (регистра множимого). В известных устройствах зто осуществляется также за два цикла: в первом цикле происходит сложение младшей половины регистра частичных произведений с содержимым регистра множимого,, во втором цикле - прибавление к старшей части регистра частичного произведения единиц и переноса из младшей, если таковой . имеется.f Таким образом, и в этом йлучае требуется дополнительное оборудование и время. С целью уменьшения общего количества оборудования в цифровой машине, регистры которой выполнены на основе динамического накопителя, вычислительная машина предложенной конструкции содержит дешифратор состояния, блок коммутации, два злемента И, элемент ИЛИ, причем входы дешифратора состояния соединены с выходами тактового генератора, счетчика регистров и счетчика разрядов, один из выходов дешифратора состояния соединен с входом блока коммутации, другой выход дешифратора состояния с установочным входом счетчика регистров; выходы блока коммутации соединены соответственно с одним из входов первого и второго элементов И, вторые входы которьк соединены с выходом тактового генератора; выход первого элемента И соединен со счетнь1м входом счетчика регистров; выход счетчика регистров подключен к одному из входов элемента ИЛИ, другой вход которого соединен с выходом второго элемента И; выход элемента ИЛИ соеди нен со входом счетчика разрядов. Такое построение машины позволяет изменять число регистров, принадлежащих последовательно расположенным зонам в накопителе. Например, при использованиип -раз рядных чисел первые п зон содержат по К регистров, а последующие зоны только по одному регистру. Тогда можно рассматривать один регистр (двойной длины), состоящий из какого либо К регистров первой части цикла накопителя и регистра второй части цикла, разряды которого входят в одинарные зоны. Какой именно из К регистров входит в состав длинного регистра, определяется моментом переключения блока коммутации, который устанавливается дешифратором состояния системы синхронизации, включающей тактовый генератор, счетчики разрядов и регистров. При зтом з один цикл движения инфоомации в накопи теле легко осуществляется как сдйиг двойного регистра, так и сложение П-разрядного регистра с регистром двойной линии. На фиг. 1 схематично изображена машина предложенной конструкции. Она содержит динамический преобразователь 1, арифметическое управляющее устройство 2, тактовый генератор 3, первый элемент И 4, второй элемент И 5, счетчик регистров 6, элемент ИЛИ 7, счетчик разрядов 8, .дешифратор состояния 9, блок коммутации 10. На фиг. 2 показана диаграмма расположения информации в динамическом накопителе в частном случае для трех регистров и эпюры работы отдельных узлов устройства, где приняты следующие обозначения: 11 - начальный строб; 12, 13, .14 - регистры динамического накопителя (13 - регистр двойной длины); 15, 16 - сосед ние информационные циклы; 17 - зона срыва генерации; 18 - единичное состояние блока кoммyтaц ш; 19 - нулевое состояние блока коммутации| 20 - потенциал первого разряда, вклю чающий первые разряды всех регистров динамического накопителя; 21 - потен циал п-го разряда (где п - число разрядов подсчёта счетчика разрядов) еключающий И -е разряды всех регист24ров накопителя; 22 - потенциал первого разряда, включающий первый разряд второй половины (старшие, разряды) регистра двойной длины 13j 23 потенциал разряда, включающий только п-и разряд второй половины (старшие разряды) регистра двойной длины 13; 24, 25 - соответственно первая и вторая информационные части цикла накопителя. Динамический накопитель 1 предлагаемой машины (см. фиг. 1) соединен с арифметическим управляющим устройством (АУУ), связанным с устройством синхронизации. Динамический накопитель служит для хранения информации и систоит из К. регистров длиной п разрядов, так что каждая i -ая зона (разряд) содержит регистров - первая часть цикла накопителя (24) и еще одного дополнительного регистра длиной также г разрядов во второй части цикла (25), где каждая зона содержит лишь один регистр. АУУ служит для выполнения в определенной последовательности операций над содержимым регистров динамического накопителя. Один из входов первого элемента И 4 соединен с выходом тактового генератора 3, другой вход элемента И 4 соединен с одним из выходов блока коммутации 10, выход элемента И 4 с.о.единен со счетным входом счетчика регистров 6. Первый элемент И 4 служит для подачи на счетный вход счетчика регистров 6 импульсов с тактового генератора 3 Один из входов второго элемента И 5 соединен с выходом тактового генератора, другой вход элемента И 5 соединен со вторым входом блока коммутации 10. Выход элемента И 5 соединен с дним из входов элемента ИЛИ 7. Элеент И 5 служит для подачи на счетный вход счетчика 8 тактовых импульсов с тактового генератора 3. Счетчик 6 егистров соединен со вторым входом элемента ШШ 7. Счетчик 6 служит для ыдачи регистровых импульсов при аботе в первой информационной части икла накопителя (24) и для выдачи отенциала регистра двойной длины при аботе во второй части цикла (25). Выход элемента ИЛИ 7 соединен со четным входом счетчика 8. Элемент ИЛИ 7 служит для подачи на счетный вход счетчика 8 регистровых импульсов (работа в первой части цикла) или тактовых импульсов (рабо(са по второй части цикла) . Счетчик 8 служит для пересчета на h разрядов и управления дешифрато ром 9, а также АУУ 2. БХО.ДЫ дешифратора 9 соединены с вьжодами счетчиков 6 и 8, а также с тактовым генератором 3, один из выходов дешифратора подключен к уста новочному входу счетчика 6, а другой выход - к входу блока 10, Дешифратор 9 служит для подготовк системы синхронизации машины при работе л режимах первой части цикла и второй. Блок 10 служит для переключения системы синхронизации одного режима работы, например 24, в другой - 25. Машина работает следующим образом Обозначим предварительно составляющие двойного регистра символами A)f и А 9 одинарные регистры В,, С и т.д., где индекс К относится к пер вой информационной части цикла (24) а индекс 1 - ко второй (25). Сохр ним указанную систему регистров, то да в первой половине цикла накопителя (24) счетчик регистров работает, а во второй половине цикла (25) сохраняет состояние, определяемое номером регистра двойной длины. Таким образом цепи АУУ 2 и соответственно цепи динамического накопителя 15 управляемые сигналами А (регистр двойной длины), работают в течение всего цикла накопителя (например, сдвиг двойного регистра), а управляемые потенциалы. В, С, и т.д. - только в течение первой информационной части цикла накопителя. В начале цикла накопителя сигнал дешифратора состояния 9 устанавливает блок 10.в такое состояние, что тактовый генератор 3 непосредственно работает через элемент И 4 на счетчик 6, который, в свою очередь, работает на счетчик 8. По окончании первой части цикла 24 дешифратор 9 переключает блок 10, отключая тем самым тактовый генератор 3 от счетчика 6,, и подключает тактовый генератор 3 к счетному входу счетчика 8 и устанавливает счетчик 6 в состояние, соответствующее регистру двойной длины.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора и предварительной обработки информации | 1981 |

|

SU1012230A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА ДЛЯ ТЕХНОЛОГИЧЕСКИХ РАСЧЕТОВ | 1968 |

|

SU231888A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для моделирования узлов коммутации сообщений | 1985 |

|

SU1278879A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА, содержащая динамический накопитель, соединенный с арифметическим и управляющим устройством, устройство синхронизации с тактовым генератором и счетчиками разрядов и регистров, соединенными с арифметическим : управляющим устройством, .отличающаяся тем, что, с целью уменьшения общего количества оборудования, она содержит дешифратор состояния, блок коммутации, два элемента И иэлемент ИЛИ, причем входы дншифратора состояния соединены с выходами тактового генератора, счетчика регистров и счетчика разрядов, один из выходов дешифратора состояния соединен с входом блока коммутации, другой выход дешифратора состояния - с установоч- нь!м входом счетчика регистров; выходы блока коммутации соединены соответственно с одним из входов первого и второго элементов И, вторые входы которых соединены с выходом тактового генератора; выход первого элемента И соединен со счетным входом счетчика регистров; выход счетчика регистров ,-. подключен к одному из входов элемента ИЛИ, другой вход которого соединен с выходом второго элемента И, выход элемента ' ИЛИ соединен со входом счетчика разрядов.(Л,s

Авторы

Даты

1985-02-07—Публикация

1970-08-06—Подача