1

Изобретение относится к области автоматики и вычислительной техники .и может быть использовано как автономное операционное звено, так и в составе частотно-импульсных вычислительных устройств.

Известно множительно-делительноё устройство Ш, содержащее два триггера и два элемента И, причем выход I первого триггера соединен с перкзн входом первого элемента И, выход которого соединен со счетным входом второго триггера, выход 1 которого соединен с первым входом второго элемента И и установкой нуля первого триггера..

К недостаткам такого, устройства относятся пульсации выходной частоты fi , что затрудняет ее дальнейшую обработку.

Наиболее близким к изобретению является частотно-импульсное множительно-делительноё устройство 2}, содержащее реверсивный счетчик, дифференцирунуций блок, два триггера, два элемента И, вычитающий блок, причем выход переноса реверсивного счет чика соединен с выходом дифференцирующего блока, выход которюго соединен с входом установки единицы первого триггера, единичный выход которого соединен с первым входом первого элемента И, второй вход и выход которого соединены соответственно с шиной первого сомножителя устройства и счетным входом второго триггера, нулевой выход которого соединен с входом установки нуля первого триг10гера и первым входом второго элемента И, второй вход второго элемента И соединен с шиной делителя устройства, а 5ЫХОД дифференциружвдего блока является выходом устройства, первый вход вычитающего блока соединен

15 с выходом второго элемента И, второй вход - с шиной второго сомножителя устройства, а выхода соединены с сум шру1ацим и вычитаявдим входами ре20версивного счетчнка.

К недостаткам этого устройства следует отнести сущестйунхцее ограни V

(1)

чение

25

частота делителя, где

F, - частота первого сомножителя.

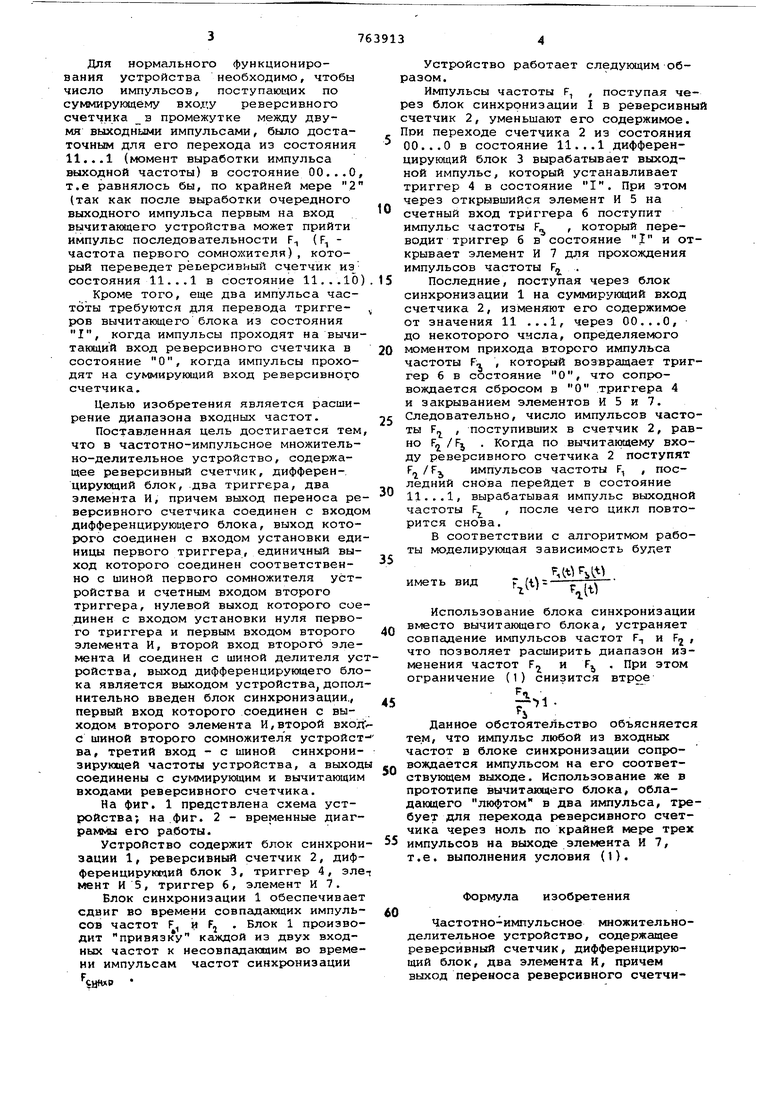

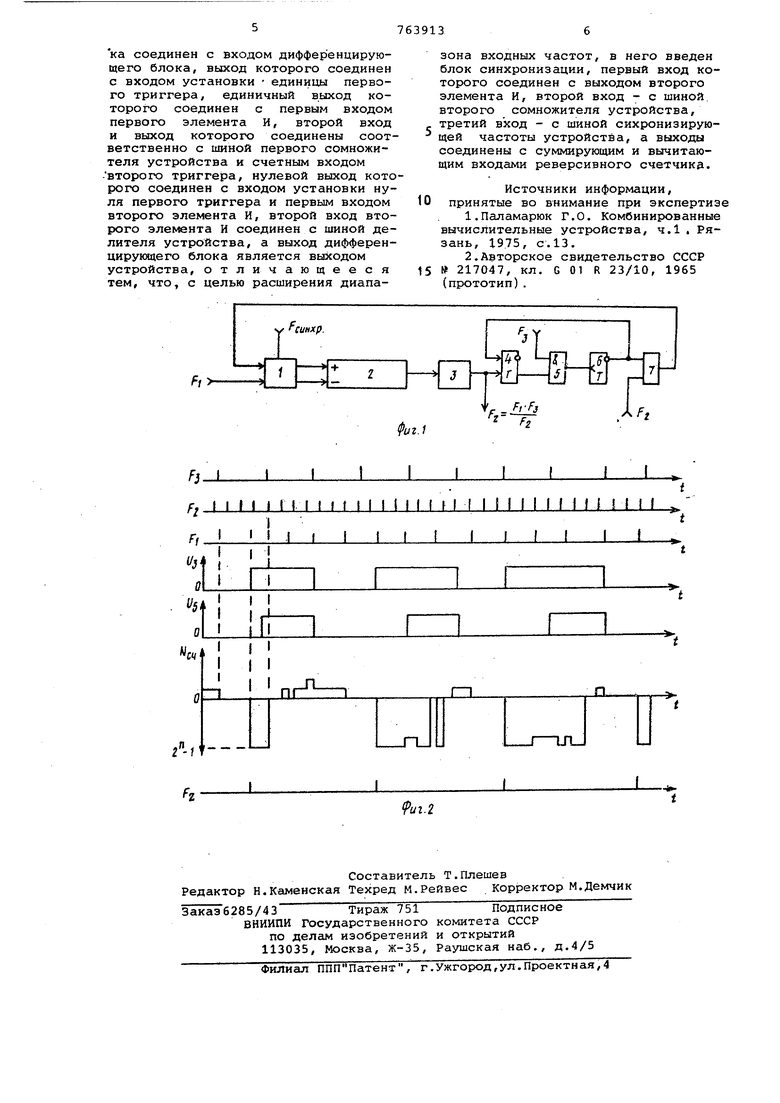

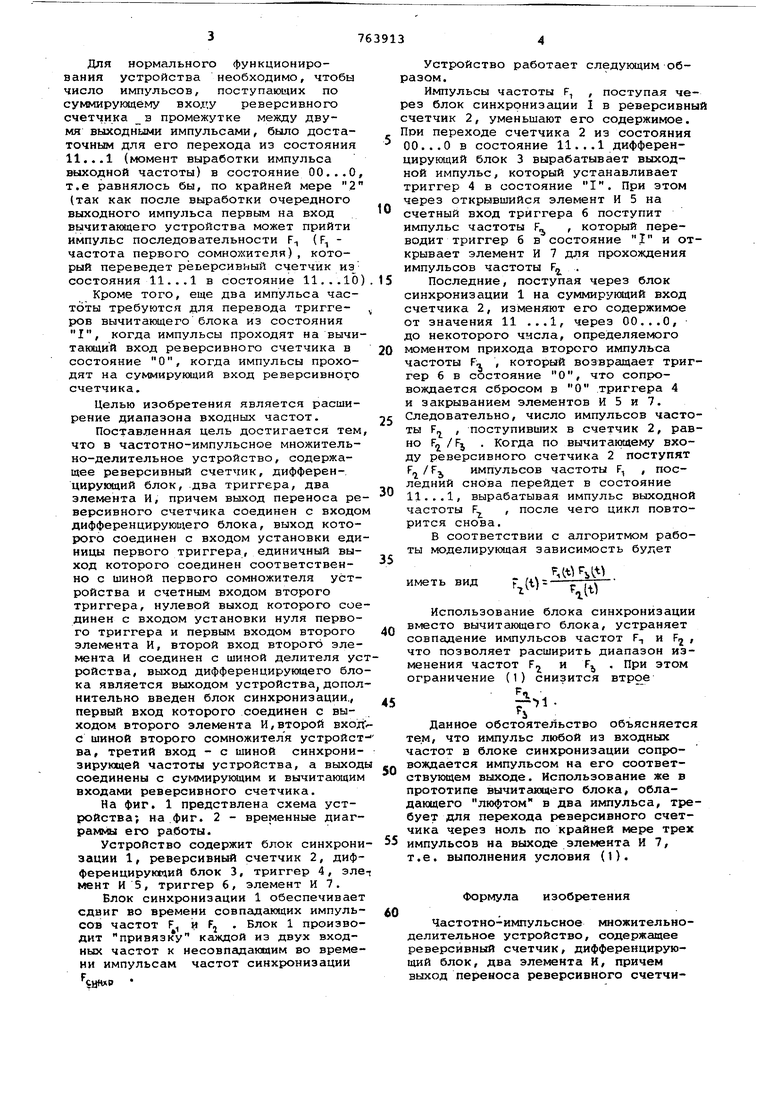

Это ограничение обусхювлено следующими причинами. Для нормального функционирования устройства необходимо, чтобы число импульсов, поступающих по суммирующему входу реверсивного счетчика в промежутке между двумя выходными импульсами, было достаточным для его перехода из состояния 11...1 (момент выработки импульса выходной частоты) в состояние 00...О, т.е равнялось бы, по крайней мере 2 (так как после выработки очередного выходного импульса первым на вход вычитаквдего устройства может прийти импульс последовательности F ( FI частота первого сомножителя), который переведет реверсивный счетчик из состояния 11... 1 в состояние 11,..10 Кроме того, еще два импульса частоты требуются для перевода триггеров вычитающего блока из состояния I, когда импульсы проходят на вычитакядий вход реверсивного счетчика в состояние О, когда импульсы проходят на суммирукадий вход реверсивного счетчика. Целью изобретения является расширение диапазона входных частот. Поставленная цель достигается тем что в частотно-импульсное множительно-делительное устройство, содержащее реверсивный счетчик, дифферен-. цирующий блок, два триггера, два элемента И, причем выход переноса ре версивного счетчика соединен с входо дифференцирующего блока, выход которого соединен с входом установки еди ницы первого триггера, единичный выход которого соединен соответственно с шиной первого сомножителя устройства и счетным входом второго триггера, нулевой выход которого сое динен с входом установки нуля первого триггера и первым входом второго элемента И, второй вход второго элемента И соединен с шиной делителя ус ройства, выход дифференцирукядего бло ка является выходом устройства, допол нительно введен блок синхронизации., первый вход которого соединен с выходом второго элемента И,второй Bxojf с шиной второго сомножителя устройст ва, третий вход - с шиной синхронизирующей частоты устройства, а выход соединены с суммирующим и вычитающим входами реверсивного счетчика. На фиг, 1 предствлена схема устройства; на фиг. 2 - временные диаграммы его работы. Устройство содержит блок синхрони зации 1, реверсивный счетчик 2, дифференциругадий блок 3, триггер 4, зле мент И 5, триггер 6, элемент И 7. Блок синхронизации 1 обеспечивает сдвиг во времени совпадающих импульсов частот F t FJ . Блок 1 производит привязку каждой из двух входных частот к несовпадакяцим во времени импульсам частот синхронизации ЧН«ХР Устройство работает следующим обазом. Импульсы частоты F, , поступая чеез блок синхронизации I в реверсивный четчик 2, уменьшают его содержимое. ри переходе счетчика 2 из состояния 00 ... О в состояние 11...1 дифференцирующий блок 3 вырабатывает выходной импульс, который устанавливает триггер 4 в состояние I. При этом через открывшийся элемент И 5 на счетный вход триггера 6 поступит импульс частоты „ , который переводит триггер б в состояние I и открывает элемент И 7 для прохождения импульсов частоты F . Последние, поступая через блок синхронизации 1 на суммирукадий вход счетчика 2, изменяют его содержимое от значения 11 ...1, через 00...О, до некоторого числа, определяемого моментом прихода второго импульса частоты F- , который возвращает триггер б в состояние О, что сопровождается сбросом в О триггера 4 и закрыванием элементов И 5 и 7. Следовательно, число импульсов частоты F,j , поступивших в счетчик 2, равно F. / FJ . Когда по вычитающему входу реверсивного счетчика 2 поступят F / F импульсов частоты F, , последний снова перейдет в состояние 11... 1, вырабатывая импульс выходной частоты F, после чего цикл повторится снова. В соответствии с алгоритмом работы моделирующая зависимость будет - .,,ты iti иметь вид Использование блока синхронизации вместо вычитающего блока, устраняет совпадение импульсов частот F-, и Fj , что позволяет расширить диапазон изменения частот Fr При этом ограничение (1) снизится втрое РТ. Данное обстоятельство объясняется тем, что импульс любой из входных частот в блоке синхронизации сопровождается импульсом на его соответствующем выходе. Использование же в прототипе вычитс1ющего блока, обладающего люфтом в два импульса, требует для перехода реверсивного счетчика через ноль по крайней мере трех импульсов на выходе элемента И 7, т.е. выполнения условия (1). Формула изобретения Частотно-импульсное множительноделительное устройство, содержащее реверсивный счетчик, дифференцирующий блок, два элемента И, причем выход переноса реверсивного счетчика соединен с входом дифференцирующего блока, выход которого соединен с входом установки единицы первого триггера, единичный выход которого соединен с первым входом первого элемента И, второй вход и выход которого соединены соответственно с шиной первого сомножителя устройства и счетным входом второго триггера, нулевой выход которого соединен с входом установки нуля первого триггера и первым входом второго элемента И, второй вход второго элемента И соединен с шиной делителя устройства, а выход дифференцирующего блока является выходом устройства, отличающееся тем, что, с целью расширения диапазона входных частот, в него введен блок синхронизации, первый вход которого соединен с выходом второго элемента И, второй вход - с шиной, второго сомножителя устройства, третий вход - с шиной сихронизирующей частоты устройства, а выходы соединены с суммирующим и вычитающим входами реверсивного счетчика.

Источники информации, принятые во внимание при экспертизе

1.Паламарюк Г.О. Комбинированные вычислительные устройства, ч.1 . Рязань, 1975, с.13.

2.Авторское свидетельство СССР № 217047, кл. G 01 R 23/10, 1965 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Частотно-импульсное множительно-дЕлиТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU813426A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| Расширитель импульсов | 1979 |

|

SU790188A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| Множительное устройство | 1980 |

|

SU951304A1 |

| Множительно-делительное устройство | 1985 |

|

SU1305677A1 |

| Устройство для позиционного программного управления с самоконтролем | 1982 |

|

SU1072002A1 |

I I I

Авторы

Даты

1980-09-15—Публикация

1978-08-21—Подача