1

Изобретение относится к области вычислительной техники.

Известен четырехфазный динамический //(-триггер на МОП-транзисторах, содержащий два инвертора, сборку К. с выходной сборкой, сборку / с нервой схемой совпадения на выходе, два инвертора, вторую схему совпадения.

Целью изобретения является повышение надежности и быстродействия устройства.

Для этого в предложенном устройстве вход выходной сборки и вход первой схемы совпадения соединены с нервой выходной шиной триггера, выход первой схемы совпадения подключен к первому входу второй схемы совпадения, второй вход которой соединен через первый инвертор с выходом выходной сборки, выход второй схемы совпадения соединен со второй выходной шиной триггера и через второй инвертор - с первой выходной шиной триггера.

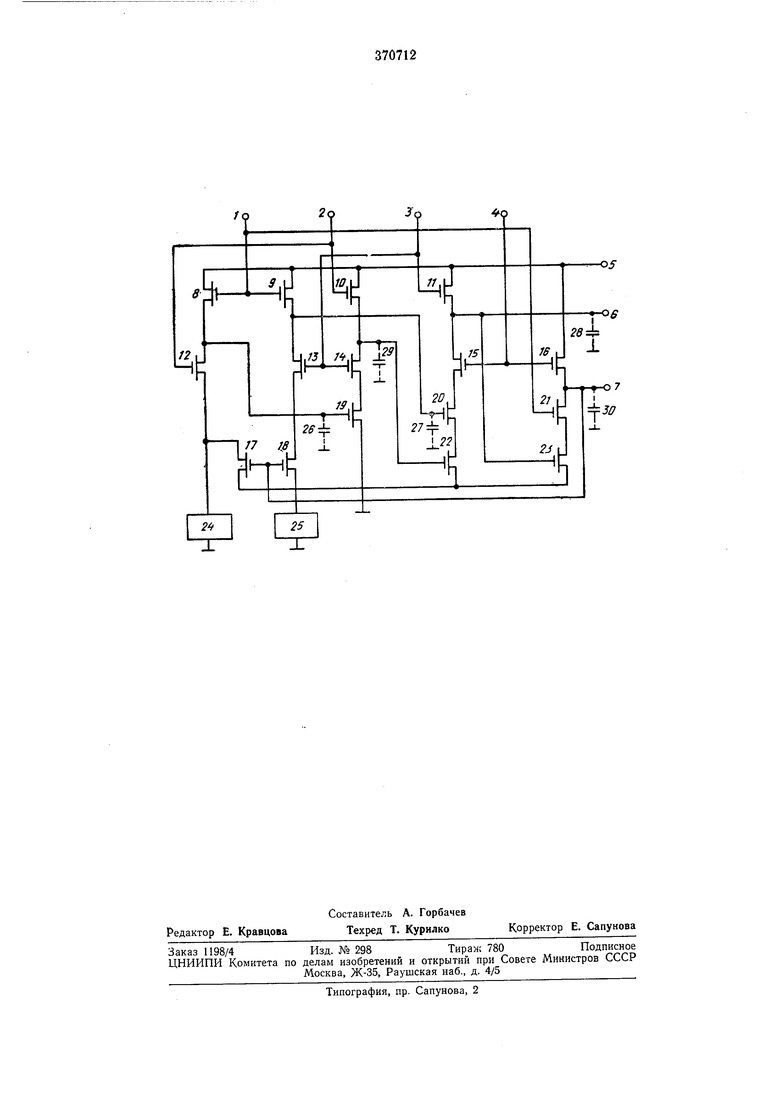

Устройство содержит входы 1, 2, 3, 4, входную шину 5 источника питания, выходы 6, 7 триггера, МОП-транзисторы 8-23, логические схемы 24, 25 (сборки К и I соответственно).

Пусть в исходном состоянии выход 6 имеет потенциал, близкий к потенциалу «земля, выход 7 - нотеЕциал, близкий к потенциалу источника питания, а логические схемы 24 и 25, работающие в ключевом режиме, разомкнуты, что соответствует логическому «нулю (следовательно, истоки транзисторов 12 и 18 не заземлены).

npiH поступлении на вход / фазы ф1 транзисторы 8 и 9 будут открыты. Входные емкости 26 и 27 транзисторов 19 и 20 заряжаются приблизительно до потенциала источника питания. При поступлении фазы фа на вход 2 транзистор 2 будет открыт через последовательно соединенный с ним транзистор 17. Транзистор 17 открыт в связи с наличием на его затворе отрицательного потенциала, поданного посредством обратной связи с выходом 7.

Таким образом, входная емкость 26 разряжается приблизительно до потенциала «земля. По фазе ф2 открывается транзистор 10, и емкость 2S транзистора 22 заряжается приблизительно до потенциала источника питания.

При ноступлении на вход 3 фазового импульса фз транзистор 13 будет закрыт, так как закрыт последовательно соединенный с ним транзистор 18, поскольку исток транзистора 18 не соединен с шиной «земля. На входной емкостн 27 транзистора 20 сохраняется отрицательный потенциал, соответствующий логической «единице. Транзистор 11 при поступлении фз открывается, и входная емкость 28 транзистора 23 заряжается приблизительно до

потенциала источника питания. Транзистор

14 при поступлении на его затвор фз будет закрыт, так как закрыт последовательно соединенный с ним транзистор 19 (на затворе потенциал, соответствующий логическому «нулю).

Следовательно, на входной емкости 29 транзистора 22 сохраняется потенциал, соответствующий логической «единице.

При поступлении фазового импульса ф4 на вход 4 транзистор 15 открывается, так как будут открыты последовательно соединенные с ним транзисторы 20 и 22 (на затворах которых потенциал приблизительно равен потенциалу источника питания).

Следовательно, входная емкость 28 транзистора 23 заряжается до потенциала приблизительно равного иотенциалу «земля. Траезистор 16 при поступлении ф4 открывается, и входная емкость 30 транзисторов 17 и 18 заряжается приблизительно до потенциала источника питания.

На вход / поступает фаза ф1 следующей тетрады фазирующих импульсов ф1-ф4. При этом транзистор 21 будет закрыт, так как закрыт последовательно соединенный с ним транзистор 23 (на затворе потенциал приблизительно равен потенциалу «земля). Входная eiMKOiCTb 30 TpaH3iHCTqpoe 17 и 18 сохраняет потенциал, приблизительно равный потенциалу источника питания.

Следовательно, при подаче на оба входа логических нулей триггер сохраняет свое состояние.

Допустим, что к моменту прихода ф1 логическая схема 24, работающая в ключевом режиме, разомкнута, что соответствует логическому «нулю, а схема 25 - замкнута, что соответствует логической «единице.

По фазе ф1 емкости 26 и 27 транзисторов 19 и 20 заряжаются приблизительно до потенциала источника питания. При поступлении фазы ф2 на вход 2 емкость 26 транзистора 19 заряжается шриблизительно до тотенцнала «земля через последовательно соединенные транзисторы 12 и 17. Транзистор 17 открыт, так как на затворе имеется отрицательный потенциал поданный посредством обратной связи с выхода 7. По фазе ф2 емкость 28 транзистора 22 заряжается приблизительно до потенциала источника питания. При поступлении фазы фз на вход 5 емкость 27 транзистора 20

разряжается приблизительно до потенциала «земля через последовательно соединенные транзисторы 13 и 18. Транзистор 18 открыт, так как на затворе имеется отрицательный потенциал, поданный посредством обратной свяди с выхода 7, а исток соединен с землей через замкнутый ключ 25. По фазе фз емкость 28 транзистора 23 заряжается приблизительно до потенциала источника питания через транзистор //. До окончания этого фазового импульса емкость 29 сохраняет потенциал, приблизительно равный потенциалу источника питания, так как транзистор 19 закрыт, в связи с наличием на его затворе потенциала, приблизительно равного потенциалу «земля. При поступлении фазы фд на вход 4 транзистор 15 будет закрыт, так как закрыт последовательно соединенный с ним транзистор 20 (на затворе потенциал, приблизительно равный потенциалу источника питания). На фазе ф4 открывается транзистор 16, и емкость 30 транзисторов 17 и 18 закрывается приблизительно до потенциала источника питания. При поступлении фазы ф1 на вход / транзистор 21 и после5 довательно соединенный с ним транзистор 23

открываются, и емкость 30 транзисторов 17 и

18 заряжается приблизительно до потенциала

«земля.

Таким образом триггер изменяет свое со0 стояние.

Работа триггера при других входных комбинациях / и /С аналогична.

Предмет изобретения

Четырехфазный динамический //(-триггер на МОП-транзисторах, содержащей два инвертора, сборку /С с выходной сборкой, сборку / с первой схемой совпадения на выходе, два

инвертора, вторую схему совпадения, отличающийся тем, что, с целью повышения надежности и быстродействия, в нем вход выходной сборки и вход первой схемы совпадения соединены с первой выходной шиной триггера, выход первой схемы совпадения подключен к первому входу второй схемы совпадения, второй вход которой соединен через первый инвертор с выходом выходной сборки, выход второй схемы совпадения соединен со второй

выходной щиной (ра и через -второй инвертор- € перБой выходной щиной триггера.

JT

IT

| название | год | авторы | номер документа |

|---|---|---|---|

| Д-триггер | 1971 |

|

SU677073A1 |

| ЯЧЕЙКА ПАМЯТИ АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2008 |

|

RU2390860C1 |

| В П ТБ h т^^1Щ1 ,-, -j-.• :,••..i,i j I | 1973 |

|

SU406298A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Выходное устройство на мдп транзисторах | 1975 |

|

SU547970A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| ИЗОбрСТС}|МЯ | 1973 |

|

SU407356A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

Авторы

Даты

1973-01-01—Публикация