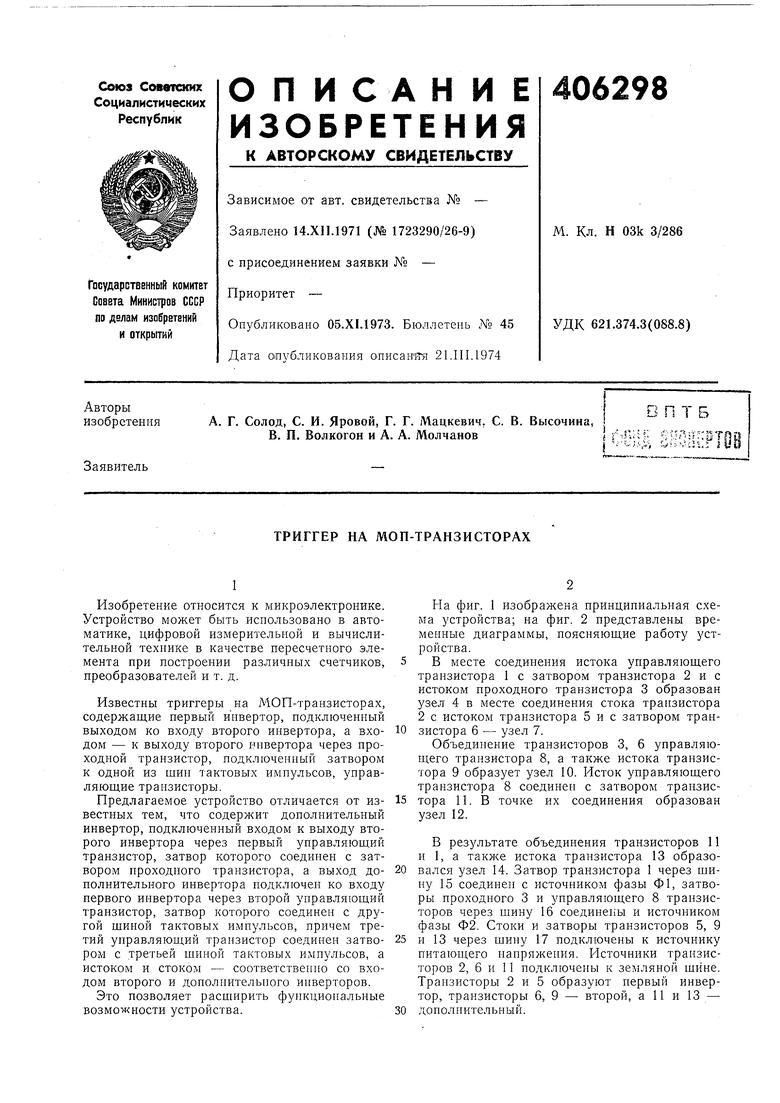

Изобретение относится к микроэлектронике. Устройство может быть использовано в автоматике, цифровой измерительной и вычислительной технике в качестве нересчетного элемента при построении различных счетчиков, преобразователей и т. д. Известны триггеры на МОП-транзисторах, содержащие первый инвертор, подключенный выходом ко входу второго инвертора, а входом - к выходу второго инвертора через проходной транзистор, подключенный затвором к одной из шин тактовых импульсов, управляющие транзисторы. Предлагаемое устройство отличается от известных тем, что содержит дополнительный инвертор, подключенный входом к выходу второго инвертора через первый управляющий транзистор, затвор которого соединен с затвором проходного транзистора, а выход дополнительного инвертора подключен ко входу первого инвертора через второй управляющий транзистор, затвор которого соединен с другой шиной тактовых импульсов, причем третий управляющий транзистор соединен затвором с третьей шнной тактовых импульсов, а истоком и стоком - соответственно со входом второго и дополнительного инверторов. Это позволяет расншрить функциональные возможности устройства. На фнг. 1 изображена принциниальная схема устройства; на фиг. 2 нредставлены временные диаграммы, поясняющие работу устройства. В месте соединения истока управляющего транзистора 1 с затвором транзистора 2 и с истоком проходного транзистора 3 образован узел 4 в месте соединения стока транзистора 2 с истоком транзистора 5 и с затвором транзистора 6 - узел 7. Объединение транзисторов 3, 6 управляющего транзистора 8, а также истока транзистора 9 образует узел 10. Исток управляющего транзистора 8 соединен с затвором транзистора 11. В точке их соединения образован узел 12. В результате объединения транзисторов 11 и 1, а также истока транзистора 13 образовался узел 14. Затвор транзистора 1 через шину 15 соединен с источником фазы Ф1, затворы нроходного 3 и управляющего 8 транзисторов через шину 16 соединены и источником фазы Ф2. Стоки и затворы транзисторов 5, 9 и 13 через шину 17 подключены к источнику питаюндего напряжения. Источники транзисторов 2, 6 и 11 нодключены к земляной шине. Транзисторы 2 и 5 образуют первый инвертор, транзисторы 6, 9 - второй, а 11 и 13- дополнительный.

Сток управляющего транзистора 18 соединен с узлом 7, исток - с узлом 12, затвор подключен к шине фазы ФЗ.

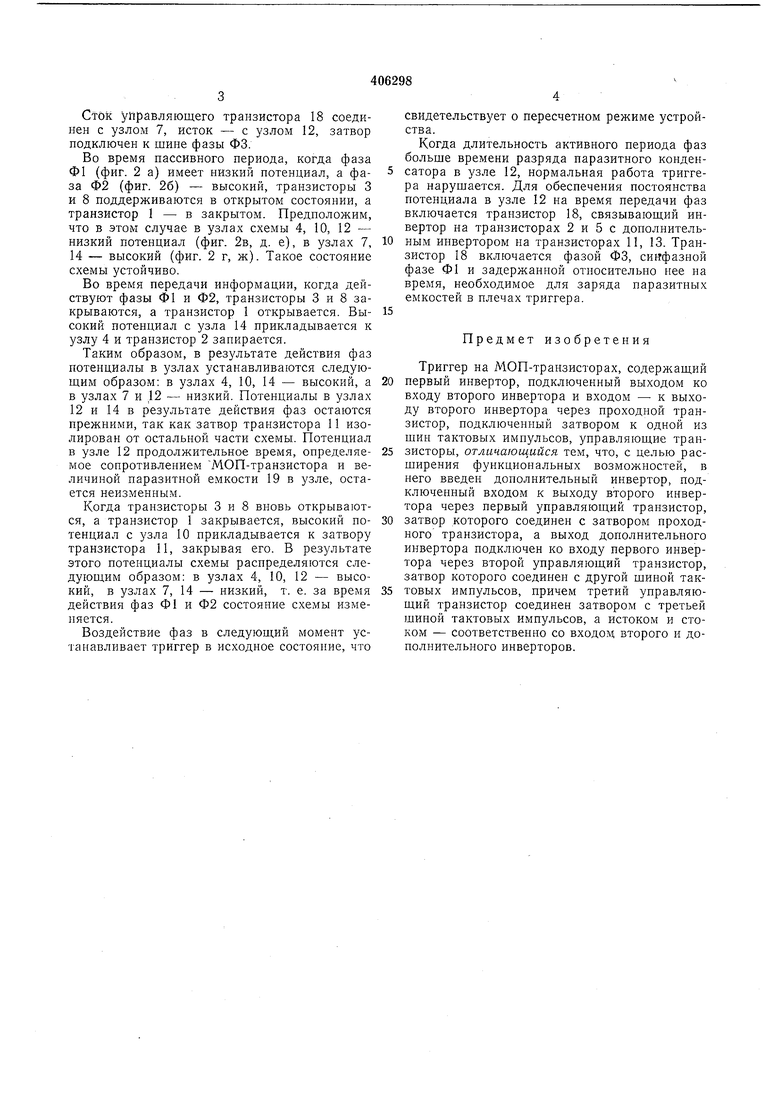

Во время пассивного периода, когда фаза Ф1 (фиг. 2 а) имеет низкий потенциал, а фаза Ф2 (фиг. 26) - высокий, транзисторы 3 и 8 поддерживаются в открытом состоянии, а транзистор 1 - в закрытом. Предположим, что в этом случае в узлах схемы 4, 10, 12 - низкий потенциал (фиг. 2в, д. е), в узлах 7, 14 - высокий (фиг. 2 г, ж). Такое состояние схемы устойчиво.

Во время передачи информации, когда действуют фазы Ф1 и Ф2, транзисторы 3 и 8 закрываются, а транзистор 1 открывается. Высокий потенциал с узла 14 прикладывается к узлу 4 и транзистор 2 запирается.

Таким образом, в результате действия фаз потенциалы в узлах устанавливаются следующим образом: в узлах 4, 10, 14 - высокий, а в узлах 7 Е 12 - низкий. Потенциалы в узлах 12 и 14 в результате действия фаз остаются прежними, так как затвор транзистора 11 изолирован от остальной части схемы. Потенциал в узле 12 продолжительное время, определяемое сопротивлением МОП-транзистора и величиной паразитной емкости 19 в узле, остается неизменным.

Когда транзисторы 3 и 8 вновь открываются, а транзистор 1 закрывается, высокий потенциал с узла 10 прикладывается к затвору транзистора 11, закрывая его. В результате этого потенциалы схемы распределяются следующим образом: в узлах 4, 10, 12 - высокий, в узлах 7, 14 - низкий, т. е. за время действия фаз Ф1 и Ф2 состояние схемы изменяется.

Воздействие фаз в следующий момент устанавливает триггер в исходное состояние, что

свидетельствует о пересчетном режиме устройства.

Когда длительность активного периода фаз больще времени разряда паразитного конденсатора в узле 12, нормальная работа триггера нарушается. Для обеспечения постоянства потенциала в узле 12 на время передачи фаз включается транзистор 18, связывающий инвертор на транзисторах 2 и 5 с дополнительным инвертором на транзисторах 11, 13. Транзистор 18 включается фазой ФЗ, сиифазной фазе Ф1 и задержанной относительно нее на время, необходимое для заряда паразитных емкостей в плечах триггера.

Предмет изобретения

Триггер на МОП-транзисторах, содержащий

первый инвертор, подключенный выходом ко входу второго инвертора и входом - к выходу второго инвертора через проходной транзистор, подключенный затвором к одной из щин тактовых импульсов, управляющие транзисторы, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен дополнительный инвертор, подключенный входом к выходу второго инвертора через первый управляющий транзистор,

затвор которого соединен с затвором проходного транзистора, а выход дополнительного инвертора подключен ко входу первого инвертора через второй управляющий транзистор, затвор которого соединен с другой шиной тактовых импульсов, причем третий управляющий транзистор соединен затвором с третьей щиной тактовых импульсов, а истоком и стоком - соответственно со входом второго и дополнительного инверторов.

ск

k 4

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ ИНВЕРТОР НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1969 |

|

SU235100A1 |

| ВСЕСОЮЗНАЯ ""}iATZh'TuD-- РТНГгч^Ргуде'^'^^КАЯ_ б::блио-|-е.на МБ АВ. А. Косинский, Ю. К. Судьин и А. П. Евдокимов | 1973 |

|

SU370712A1 |

| КОМБИНАЦИОННАЯ ЛОГИЧЕСКАЯ СХЕМА | 1971 |

|

SU320053A1 |

| ЧЕТЫРЕХФАЗНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU342299A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Полупроводниковое запоминающее устройство | 1979 |

|

SU879651A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

7

I i 1

t

t

Авторы

Даты

1973-01-01—Публикация