110 Изобретение относится к вычислительной TexiiUKB, а более конкретно к устройству записи информации в МД Тдинамический матричный накопитель, которое может быть использовано в интегральном полупроводниковом динаш ческом запоминающем устройстве с произвольной выбора и данных. Известно устрой,тво для записи информации, содержаще, выходной буфер и ключи записи, выполненные на.транзисторах дополняющего типа проводимости Г J . Недостатком известного устройства является сложность технологического процесса его изготовления из-за использования транзисторов дополняющего типа проводимости. Кроме того, недостатком является малая амплитуда сигнала на его выходах (не превышающая напряжение источнргка питания), вследствие чего в элементы памяти записывается заряд малой величины, что требует элемент памяти большой площади, Наиболее близким техническим решением к.предлагаемому является устройство для записи информации в ЩПдинакический матричный накопитель, вьЙюлненное на транзисторах одного типа проводимости и содержащее первые и зторые ключевые транзисторы записи и четыре буферных транзистора записи у которых исток первого буферного транзистора записи соединен со стоком второго и с первой шиной записи, исток третьего буферного транзистора Згзписи соединен со стоком четвертого и с второй шиной записи. Затворы пер вого и четвертого буферных транзисторов записи образуют прямой информа онный вход устройства, затворы второго и третьего буферных транзисторов записи образуют его инверсный информационный вход. Истоки- второго и четаертого .буферных транзисторов записи соединены с общей шиной, стоки пер. вого и третьего буферных транзисторов записи соединены с шиной питания Шины записи соединены со стоками со.ответственно первых и вторых ключевых транзисторов записИд затворы которых попарно объединены и образуют входы разрешения записи устройства ф . . , . , , фр ... . а истоки каждой пары ключевых транзисторов записи об разуют первую, втор утл, ,,. j-io,,.,/п-ю пары выходов устройства записи. Причем в каждой паре выходов исток пер2вого ключевого транзистора записи образует прямой, а исток второго ключевого транзистора записи - инверсный выход устройства C2J, При работе устройства на одном из его информационных входов устанавливается высокий уровень напряжения и подается В :1сокий уровень одного из сигналов разрешения записи фз.) . В результате через открывшиеся буферные транзисторы записи, на затворы которых подан высокий уровень напряжения, и через открыт то пару ключевых транзисторов записи, на затворы которых подан высокий уровень сигнала разрешения записи , на выходах i-к пары ключевых транзисторов записи устанавливается народном высокий уровемь напряженияравнын напряжению питания ЕЙ, на -,, 11CL другом - низкий уровень напряжения У 0. При этом в случае записи 1 (высокий уровень напряжения подан на прямой информационный вход устройства) на прямом выходе ,,будет установлен высокий уровень V,, , на инверсном - низкий уровень V , а при записи О - наоборот. Выходы устройства разрядными шинами соединены с входами элементов памяти на копителя. Информйциоппы.й сигнал V или V записывается в один из элементов памяти и хранится в нем Б виде информационного заряда &q, величина которого равна где Cfi - емкость элемента памяти; ди - амплитуда записываемого в элемент памяти сигнала ; выхода блока записи. В случае прототипа -V Е, Увеличение амплитуды записывагзм го в элемент памя-ти сигнала в соотз(;тствии с (1) обеспечивает при неизменной величине емкое 1и Cj большую величину хранимого в элементе памятя за1эя.ца, чтоувеличивает надежность хранения информации, либо при неизменной ь-еличине хранимого заряда позволяет увеичить степень интеграции устройства путем уменьшения размерог емкости элемента памяти. Недостатком данного устройства ля записи является малая ам шитуца сигнала ыа его выходах 6ie превьштаю- ая напрял-сение источника питания) , следствие чего в элемент памяти запиывается заряд малой величины..что треует элемент памяти большой Ш1О1иади„ 31 Цель изобретения - повышение надежности устройства за счет увеличения амплитуды выходного сигнала. Поставленная цель достигается тем что в устройство для записи информации в ЩП-динамический матричный накопитель, содержащее первый i второй ключевые транзисторы записи, четыре буферных транзистора записи, затворы шрвого и четвертого буферных транзисторов записи являются прямым информационным входом устройства, а затворы второго и третьего буферных транзисторов записи являются инверсным информационным входом устройства стоки второго и четвертого буферных транзисторов записи соединены с обще шиной, исток второго и сток первого буферных транзисторов записи соедине ны с первой шиной записи, а исток четвертого и сток третьего буферных транзисторов записи соединены с второй шиной записи, затворы первых и вторых ключевых транзисторов записи попарно объединены и являются входом разрешения записи устройства, первая и вторая шины записи подключены к стокам соответстЕснно первого и второго ключевых транзисторов записи, истоки которых являются первым п вто рым выходами устройства соответствен но, введены конденсатор и транзисторы установки напряжения включения заряда конденсатора, удержания заряда конденсатора, сброса напряжения включения, причеьг стоки транзисторов установки напряжения включения и заряда кондет сатора соед1н-1ены с шиной питания, 15СТОКИ транзисторов удержания заряда конденсатора и сброса напряжения включения соединены с общей шиной, исток транзистора установки напряжения включения соединен с первой, обкладкой конденсатора, стоком транзистора сброса напряжения включения и стоками первого и третьего буферных транзисторов записи, исток транзистора заряда конденсатора соединен с второй обкладкойконденсатора и стоком транзистора удержания заряда конденсатора, затворы транзис

торов установки напряжения включения заряда конденсатора, сброса напряжения включения и удержания заряда конденсатора являются первым, вторым, третьим и четвертым управляющими входами устройства соответственно.

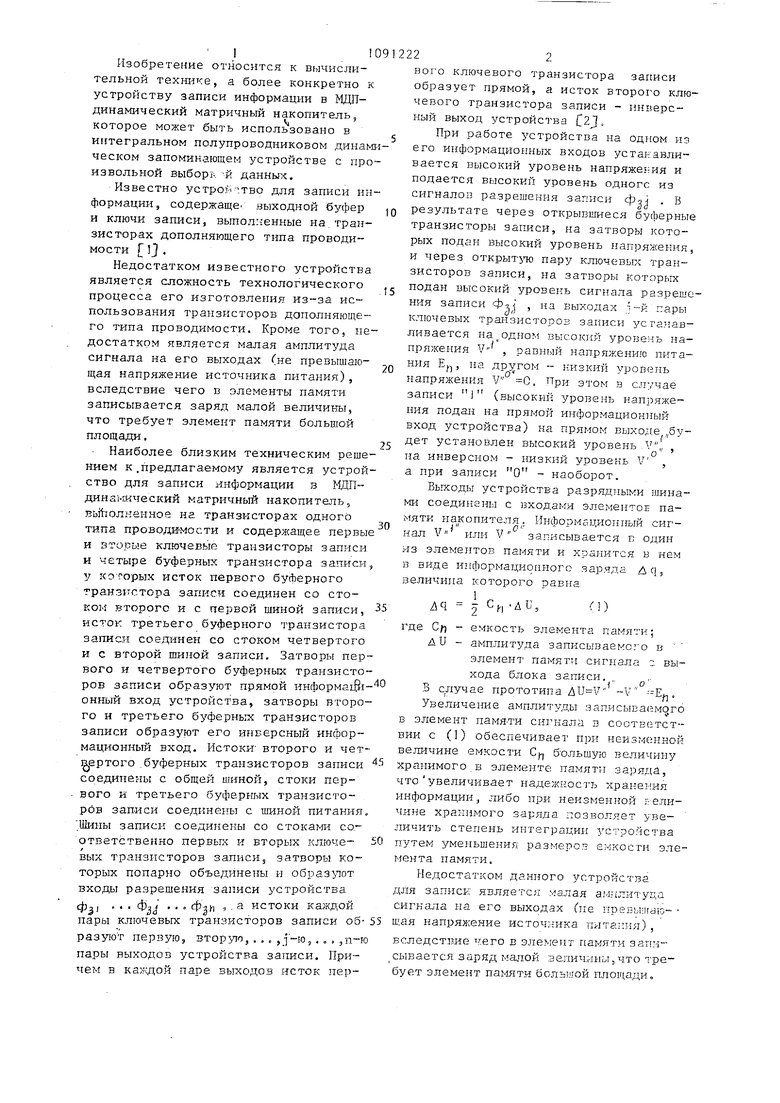

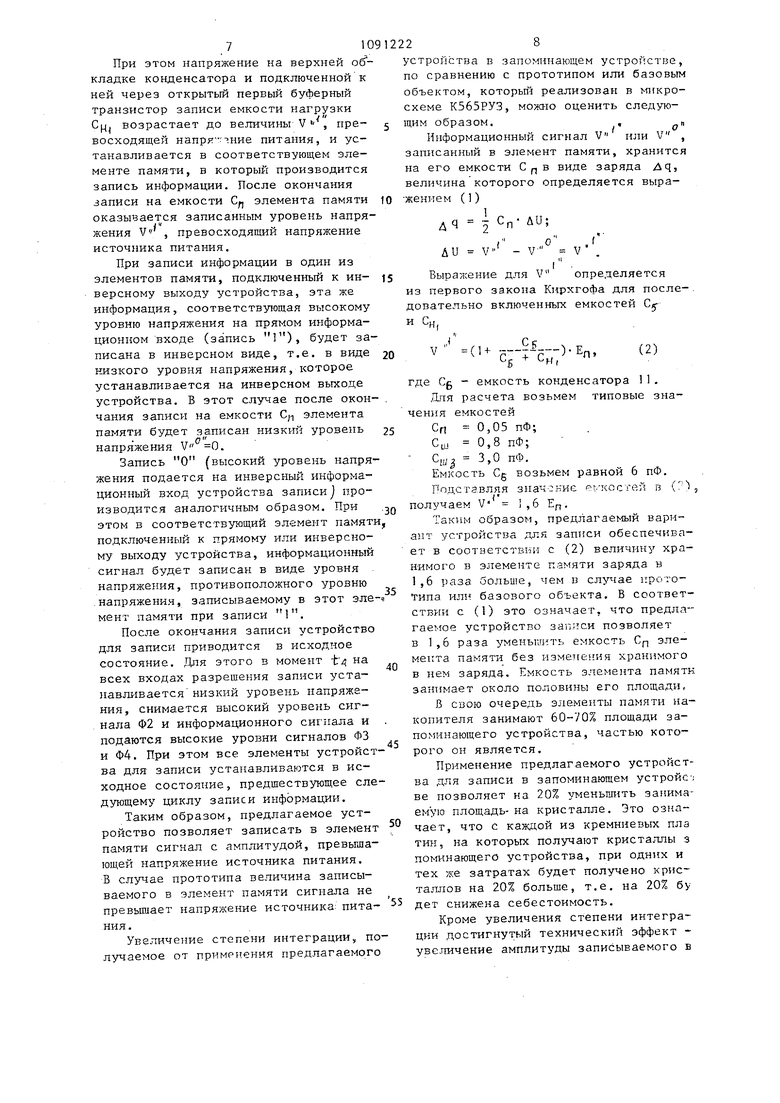

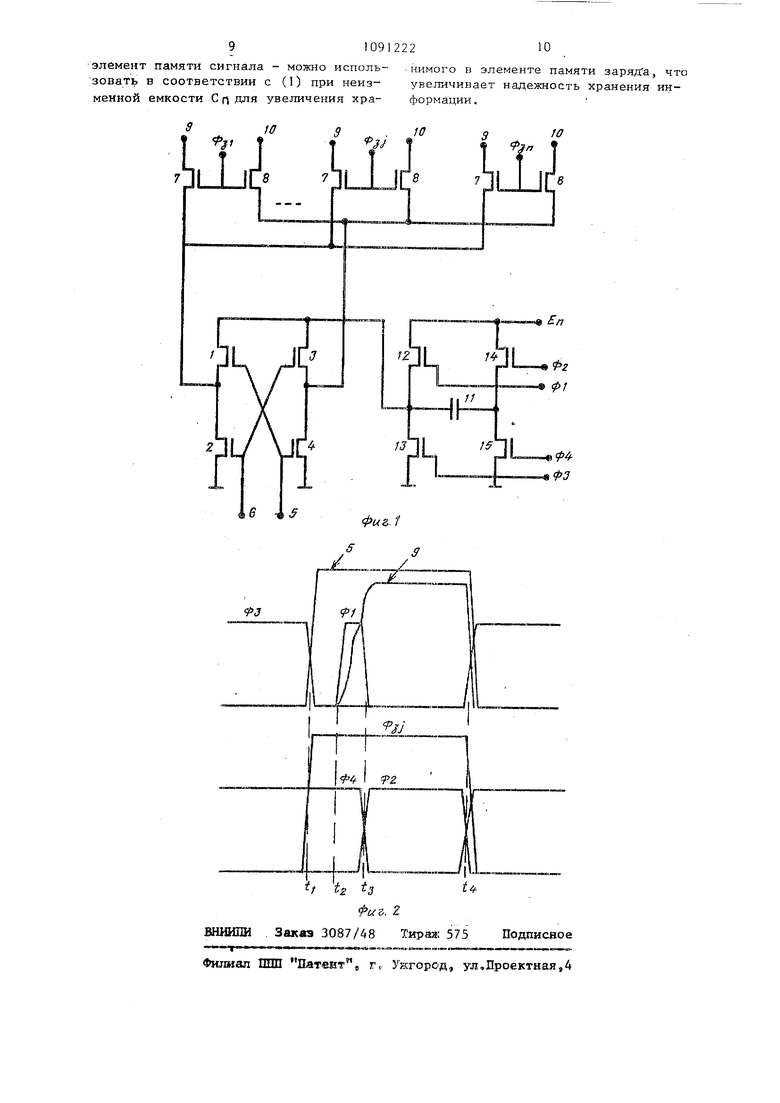

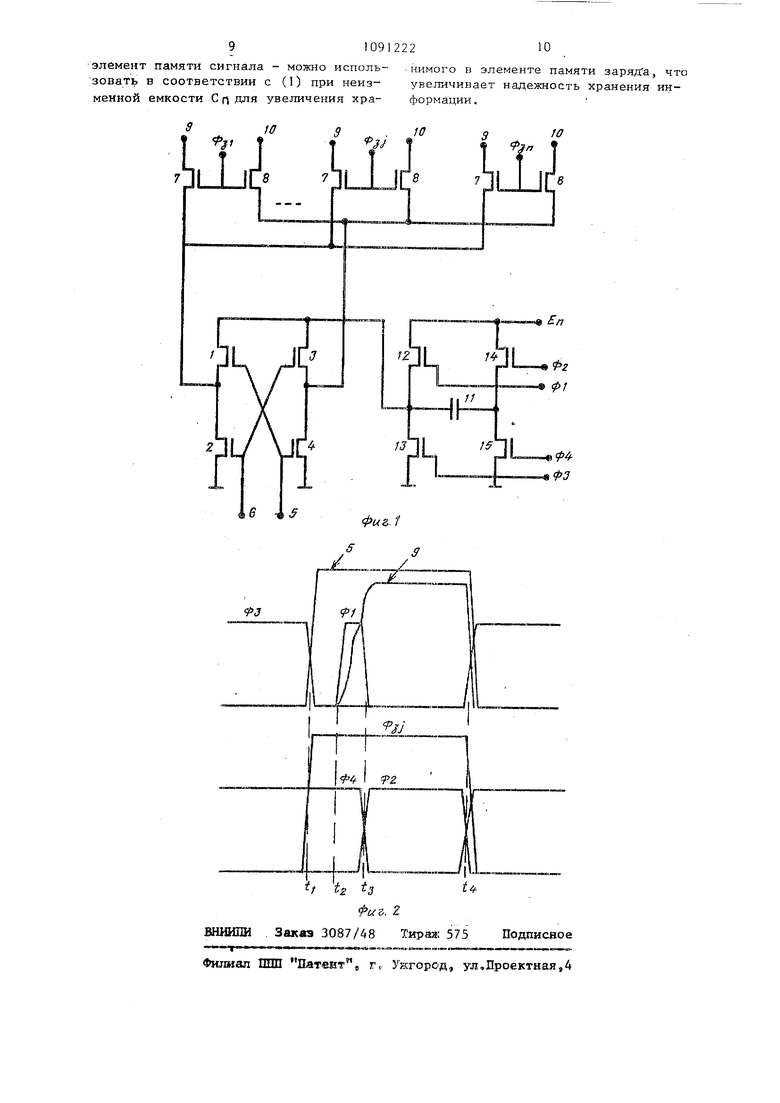

Па фиг. 1 приведена схема предлагаемого устройства; на фиг.. 2 - вреПредлагаемое «устройство для записи нреднагначено для МДП-динамического матричного накопителя, поэтому его ра- боту рассмотрим во взаимодействии с элементами памяти накопителя. Временные диаграммы, поясняющие работу устройства для записи, приведены на .фиг. 2. 2 ме-гные диаграм;:ы, поясняющие его рпботу. Устройство для за1П1си информации в М Ш-динамический матричный накопите:п (фнг.1 ), содержит четыре буферных транзистора записи, у которых исток первого буферного транзистора 1 сое тинен со стоком второго буферного транзистора 2 и с первой шиной записи, исток третьего буферного транзистора 3 соединен со стоком четвертого буферного транзистора 4 и с второй шиной записи. Затворы первого и четвертого буферных транзисторов образуют прямой информационный вход устройства 5, затворы второго и третьего буферных транзисторов образуют его инверсный информационный вход 6. Истоки второго и четвертого буферных транзисторов соединены с общей шиной. Первая и вторая шины записи соединены со стоками соответственно первых 7 и вторых 8 клют-ювых транзисторов записи, затворы которых попарно обьединены и образуют входы разрешения записи устройства Фл Фзп 3 истоки каждой пары ключевых транзисторои записи образуют первую, , . . ., -ю, . . . ,т1-ю пары выходов устройства записи. Причем в :-.;аж;;ой г.пре выходов исток первого 1;:;ючевого транзистора записи образует прямой 9, а истек второго ключевого транлтстора записи - ипиерсный 1 О Bi-.rc од ус троЯ с ТВ а . CiOKH первого и третьего буферных транзисторов записи соединены с первой обклалткой кон;1енсатора I , истоком транзистора 12 установки напряжения включения и стосом транзистора 13 сброса папря; ен;:я гключкнпя, Нижняя обклгздка конде:и:атора соод 1иеиа с истоком транзистора 14 заряда конденсатора и стоком транзистора 15 удержания заряда конденсатора. Стоки транзисторов 12 и 14 соединены с источником пита)П1я, истоки транзисторов 13 и 15 соединены с пшной. Затворы 7фацзисторов 12-15 образуют соответственно первьш Ф1, второй Ф2, третий ФЗ и четвертый Ф4 управляющие входы устройства. S10 В накопителе выходы элементов памяти соединены по столбцам разрядными шинами, которые поочередно соединены с прямыми и инверсными выходами устройства для записи, таким образом что каждая пара выкодов устройства для записи соединена с соответствующей нарой разрядных шин, В исходном состоянии на всех входах разрешения записи установлены низ-10 кие уровни напряжения сигналов ф1|1 ФЗ Ф J поэтому все пары ключевых транзисторов записи на ходятся в выключенном состоянии. Иа управляющих входах устройства Ф1 и Ф2 установлены низкие уровни напряжения, на входах ФЗ и Ф4 -- высокие уровни напряжения. На прямом и инвер ном информационных входах устройства установлець низкие уровни напряжения поэтому все транзисторы записи находятся в закрытом состоянии. Транзист ры установки напряжения включения и заряда конденсаторов также находятся в закрытом состоянии, транзисторы удержания заряда конденсатора и сбро са напряжения включения находятся в открытом состоянии, поэтому на обоих о С клад к ах конрьнсятора установлены низкие уровни напряжения., В начале ра5о его интервала в мо ке;;т Бреь;е;--1 i. кг атнсрь; j-и napt; ключ. транзисторов записи подает-сп Бысоггий уровень напряжения сигнала записи ф-м -. Нч. всех остальных ВХОДЯ разуешеция записи поддержршается низкий ypoiieHb напряжения. В результате через открывшиеся ключевы транзисторы записи к первой и второй гаинам записи оказываатся подключенно соответствующая пара разрядных шин матричного накопн1йля. При этом запись информации кожет быть проведена в любой из элементов памяти, соединенных с одной из этих разрядны шин. Для записи информации в опре.деленный элемент памяти этот элемент памяти находится во включенном состо янии и его емкост1 Cj по.дключена к соответствующей разоядной шине. Для определенности предполоядам, что во включенной сост 5янии находится элемент цамятн, соедриенный с разрядной шиной, соедргненной с прямым иыкодом устройства записи, В этот же (т времени снимггется высокиз уровень сигнала ФЗ, в результате чего транзистор сброса напряжения включения 1ереходит в закры 2 тое состояние и на один из информационных входов устройства подается высокий уровень напряжения. Допустим, высокий уровень напряжения подается на прямой информационный вход, что соответствует записи 1. При этом первый и четвертый, буферные транзисторы .записи переходят в открытое состояние, а второй и третий буферные. транзисторы записи остаются закрытыми. В результате емкость первой шины записи С емкость соответствую1цей числовой 1иины С||| и емкость Си элгмента памяти, в которой будет произзодиться запись информации, образуют суммарную емкость нагрузки CH на прямом вы-ходе устройства (С ,|. C,,|j + -I-GUJ + С(). которая -через первьй oydiepиый транзистор записи оказывается подключенной к верхней обкладке конденсатора. Емкость второй шипы записи С и емкость другой числовой шины Сщ образуют суммарную емкость нагрузки Сно на инверс1юм выходе устройства Я i.uj которая через четвертый бзферный транзистор записи оказывается подключенной к общей шине и на ней устанавливается нулевой уэои/ о. напряжения следующий момент зремени tg подается высокий уровень сигнала Ф1. FfpK этом транзистор установки напряжения включения открывается и верхняя обкладка конденсатора начинает заряжасься до высокого уровня напряжения. Поскольз у первый буферный транзистор записи находится в открытом состоянии, суммарная емкость нагрузки Cj на прямом выходе устройства записи также начинает заряжаться до высокого уровня напряжения. Нижняя обкладка конденсатора через открытый транзистор удержания конденсатора подключена к об:дей тине к на ней удерживается низкий напряжения. В времег и t , когда напряжение на верхней обкладке конденсатора и на емкость: нагрузки CIH достигает величины, близкой к напряжению питания, снимаются высокие уровни сигналов Ф1 и Ф4 и подается - ысокий уровень сигнала Ф2. Транзисторы установки напряжения включения и поддержания заряда конденсатора переходят в закрытое состояние, а транзистор заряда конд-е-1сатора открывается, в результате нижняя обкладка конденсатора заряжается до высокого уровня напряжения . При этом напряжение на верхней об кладке конденсатора и подключенной к ней через открытый первый буферный транзистор записи емкости нагрузки Сц возрастает до ве.1тнчины V «, превосходящей напря ние питания, и устанавливается в соответствующем элементе памяти, в который производится запись информации. После окончания записи на емкости С элемента памяти оказывается записанным уровень напря жения , превосходящий напряжение источника питания. При записи информации в один из элементов памяти, подключенный к инверсному выходу устройства, эта же информация, соответствующая высокому уровню напряжения на прямом информационном входе (запись 1), будет за писана в инверсном виде, т.е. в виде низкого уровня напряжения, которое устанавливается на инверсном выходе устройства. Б этот случае после окон чания записи на емкости Cj-, элемента памяти будет з аписан низкиз уровень напряжения . Запись О (высокий уровень напря жения подается на инверсный информационный вход устройства записи j производится аналогичным образом. При этом в соответствующий элемент памят подключенный к прямому или инверсному выходу устройства, информационный сигнал будет записан в виде уровня напряжения, противоположного уровню .напряжения, записываемому в этот эле мент памяти при записи 1. После окончания записи устройство для записи приводится в исходное состояние. Для этого в момент на всех входах разрешения записи устанавливается низкий уровень напряжения, снимается высокий уровень сигнала Ф2 и информационного сигнала и подаются высокие уровни сигналов ФЗ и Ф4. При этом все элементы устройст ва для записи устанавливаются в исходное состояние, предшествующее сле дующему циклу записи информации. Таким образом, предлагаемое устройство позволяет записать в элемент памяти сигнал с амплитудой, превышающей напряжение источника питания. В случае прототипа величина записываемого в элемент памяти сигнала не превышает напряжение источника: питания . Увеличение степени интеграции, по лучаемое от прнмрнения предлагаемого устройства в запоминающем устройстве, по сравнению с прототипом или базовым объектом, которьм реализован в микросхеме К565РУЗ, можно оценить следующим образом., „ Информационный сигнал V или V , записанный в элемент памяти, хранится на его емкости С р, в виде заряда Aq, величина которого определяется выражением (1) д q 2 Сл- ли; ( о .( AU - V V . Выражение для V определяется из первого закона Кирхгофа для после-. довательно включенных емкостей Су (, (2) -S и, где Cg - емкость конденсатора 11. Для расчета возьмем типовые значения емкостей Сп 0,05 пФ; 0,8 пФ; - Су 3,0 пФ, Емкость Cg возьмем равной 6 пФ. Подставляя значение et.-хостей п I получаем V 1,6 Ер. Таким образом, предлагаемый вариант устройства для записи обеспечивает в соответствим с (2) величину хранимого в элементе памяти заряда в 1,6 раза больше, чем в случае прототипа или базового объекта, Б соответствр и с (I) это означает, что предлагаемое устройство записи позволяет в 1,6 раза уменьшить емкость Ср элемепта памяти без измет1е.ния хранимого в нем заряда. Емкость эле 1ента памяти занимает около половины его площади, В свою очередь элементы памяти накопителя занимают 60-70% площади запоминающего устройства, частью которого он является. Применение предлагаемого устройства для записи в запоминающем устройс-; ве позволяет на 20% уменьшить занимаемую площадь-на кристалле. Это означает, что с каждой из кремниевых пла тин, на которых получают кристаллы з поминающего устройства, при одних и тех же затратах будет получено кристаллов на 20% больще, т.е. на 20% бу дет снижена себестоимость. Кроме увеличения степени интеграции достигнутый технический эффект увелтичение амплитуды записываемого в

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Устройство для записи информации в блоки памяти с произвольной выборкой | 1984 |

|

SU1156136A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Формирователь импульсов | 1985 |

|

SU1374416A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В МДП-ДИНА1-1ИЧЕСКИЙ МАТРИЧНЫЙ НАКОПИТЕЛЬ, содержащее первый и второй ключевые транзисторы записи, четьфе буферных транзистора записи, затворы первого и четвертого буферных транзисторов записи являются ин|1Ормационным входом устройства, а затворы второго.и третьего буферных транзисторов записи являются инверсным информационным входом устройства, стеки второго и четвертого буферных транзисторов записи соединены с общей Ешной, исток второго и сток первого буферных транзисторов записи, исток четвертого и сток третьего буферных транзисторов записи соединены с первой и второй шинами записи соответственно, затворы ключевых транзисторов записи являются входом разрешения записи устройства, первая и вторая шины записи подключены к- стокам первого и второго ключевых транзисторов записи соответственно, истоки которых являются первым и вторым вькодаъж устройства соответственно, о т л и ч а - ю щ е е с я тем, что, с целью повышения его надежности за счет увеличе.ния амплитуды выходного сигнала, оно содержит конденсатор и транзис-, торы установки напряжения включения заряда конденсатора, удержания заряда конденсатора, сброса напряжения включения, стоки транзисторов установ :и напряжения включения и заряда конденсатора соединены с шиной питания, истоки транзисторов удержания з.йряда конденсатора и сброса иапрлгления включения соединены с общей шиной, исток транзистора установки напряжения включения соединен с первой обклапкой конденсатора, стоком транзистора, сброса напря-женкя включения стоками первого и третьего буферных транзисторов записи, |изв1 исток транзистора заряда конденсатора соединен с второй обкладкой конденсаО тора и стохоь транз1-1стора удержания заряда конденсатора, затворы транзисN3 Ю Ss5 торов установки напряжения включения заряда конденсатора, сброса напряжения включения и удержания заряда конденсатора являются первым, вторым, третьим и четвертым управляющими входами устройства соответственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прибор для периодического прерывания электрической цепи в случае ее перегрузки | 1921 |

|

SU260A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4202045, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1984-05-07—Публикация

1982-03-09—Подача