Изобретение относится к радиоэлектронике и может быть использовано в аппаратуре автоматики. Известные устройства съема кода с регистра делителя-счетчика без останова счетчика используются, например, в устройствах отсчета временного положения импульсов в радиолокации. В таких устройствах импульс, временное положение которого относительно начала цикла работы делителя измеряется, поступает на узел синхронизации сигналом опорного генератора, после чего подается на узел съема кода с разрядов делителя-счетчика, представляющий собой набор логических схем «И, одни входы которых присоединены к выходам разрядов делителя, а на вторые подается импульс с выхода узла синхронизации. При поступлении этого импульса формируется кодированный сигнал. Синхронизация должна быть выполнена так, чтобы съем кода производился по окончании всех, переходных процессов (установления данной кодовой комбинации) в разрядах делителя. Это возможно в любом случае, если максимальная задержка переноса единицы в счетчике меньше периода входного сигнала делителя. Такие условия в последавательиом счетчи-ке выполняются -дри малом числе разрядов или низкой частоте входного си1пнала делителя (сигнала задающего генератора) и повышенном быстродействии всех (младших и старших) разрядов делителя. При большом числе разрядов делителя (20-30) и высокой частоте входного сигнала (5-10 мгц) указанные условия не могут быть реализованы в делителе с последовательным запуском разрядов. В этом случае используются схемы параллельного переноса единицы, в частности схема параллельного запуска всех разрядов делителя счетчика. При этом резко растет число связей между разрядами, так как на входной вентиль старшего разряда должны быть поданы входные управляющие сигналы от всех предшествующих ему младших разрядов, увеличивается «агрузка на младшие разряды, растет число входов вентилей (в старших разрядах до 20-30), что приводит к увеличе1нию объема оборудования. Это усложняет устройство и снижает его надежность. Таким образом, в известных устройствах при большом числе разрядов и высокой частоте входного сигнала съем кода с делителя с последовательным запуском не может быть осуществлен, если время переноса единицы превышает период сигнала опорного генератора. Использование в этом случае делителя с параллельным запуском увеличивает объем оборудования, усложняет схему, резко повышает требования к быстродействию старших

разрял-ов делителя и снижает надежность устройства.

Цель изобретения - обеспечение съема любой кодовой комбинации с регистра делителяочетчика (1без его останова), в котором максимальное время переноса единицы превышает период сигнала задающего генератора, при сохранении надел4ности и высокой точности.

Для этого в устройстве съема кода с многоразрядным делителем-счетчиком съем кода с групп младших и старших разрядов осуществляется раздельно; разряды на группы делят из условия, что макаи.мальное время переноСа единицы (переполнения в группе, не превышает, например, половины периода входного сигнала данной группы. При поступлении импульса съема кода он синхронизируется со вторым полупериодом задающего генератора и подается на узел съема кода группы младших разрядов непосредственно, а на узел съема кода группы старших разрядов - через дополнительный логический формирователь, на выходе которого формируется импульс только в течение второго полупериода выходного сигнала группы младших разрядов, являющегося входньш сигналом группы старших разрядов.

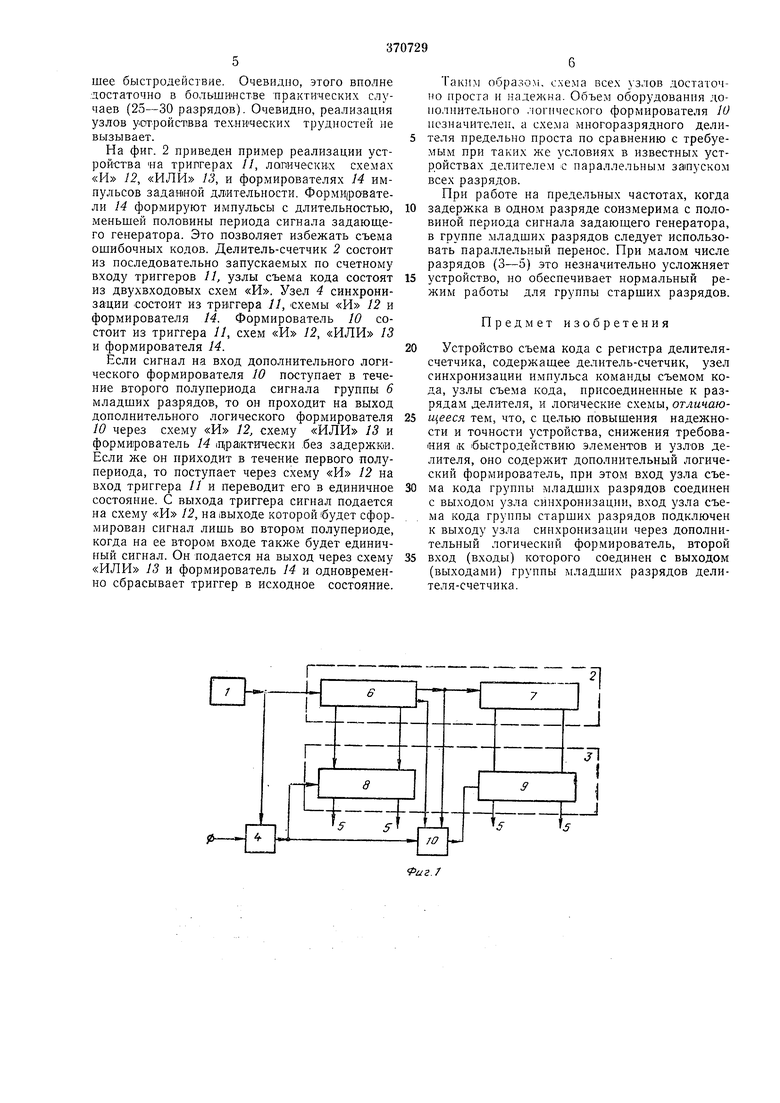

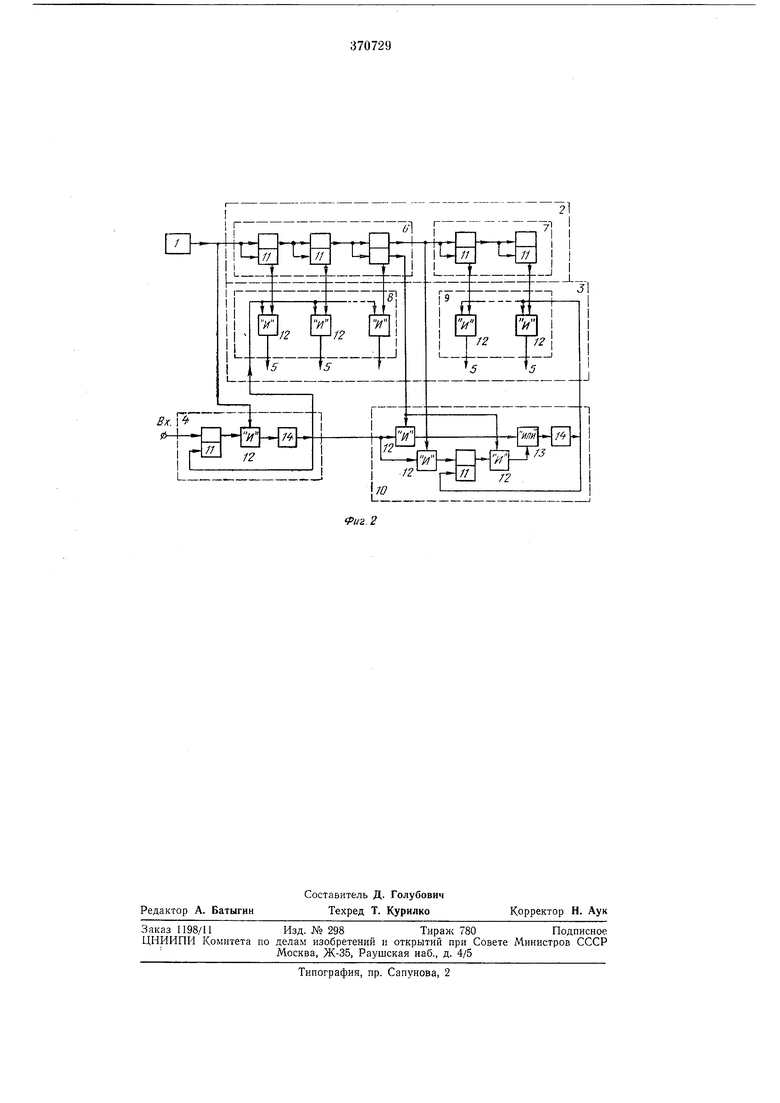

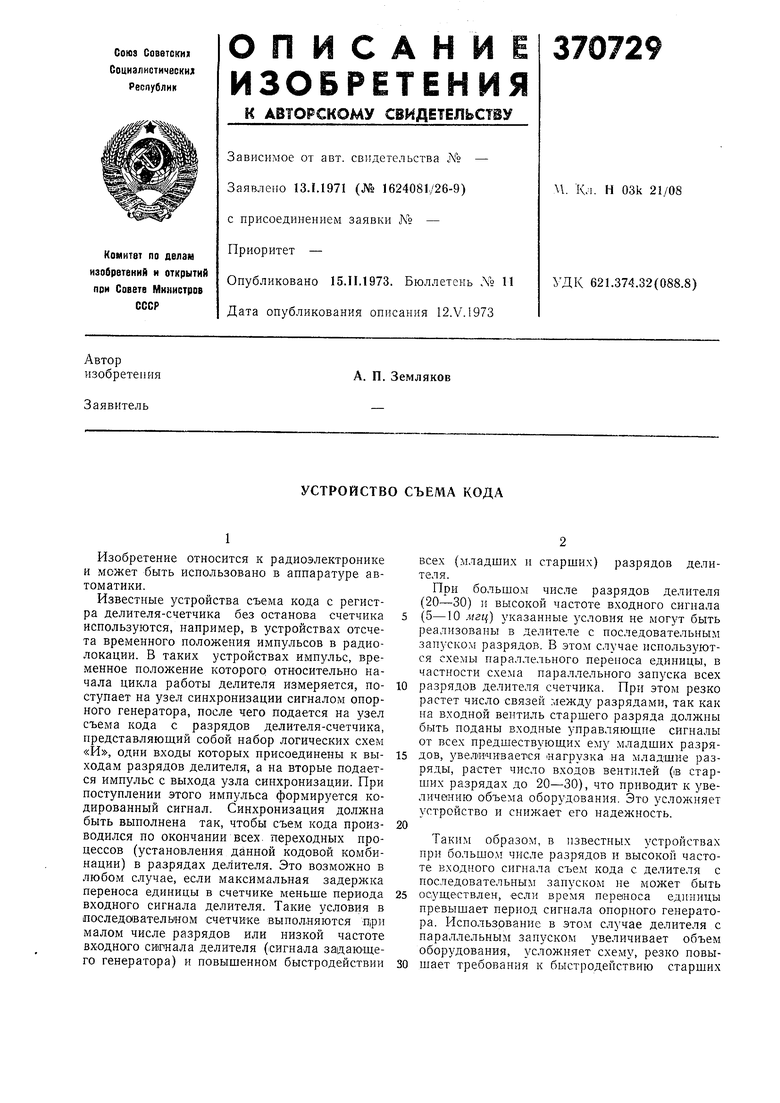

На фиг. 1 представлена блок-схема предлагаемого устройства. На фиг. 2 - пример реализации устройства.

Приняты следующие обозначения: задающий генератор /; делитель-счетчик 2; узел 3 съема кода; узел 4 синхронизации входного импульсного сигнала задающего генератора; щины 5 выдачи кода; группы младших 6 и старщих 7 разрядов делителя-счетчика 2; узлы 8, 9 съема кода младших и старших разрядов; дополнительный логический формирователь 10 сигнала управления; триггеры 11 (см. фиг. 2); лагичеокне схемы «И 12; логичеокие схемы «ИЛИ 13; формирователь 14 импульсов заданной длительности.

В уст1ройСТ1ве задающий генератор / соединен с делителем-счетчиком 2, к разрядам которого присоединен узел 3 съема кода, управляющий вход которого соединен с выходом узла 4 синхронизации входного импульса съема кода, при поступлении которого шины 5 оказываются присоединенными к разрядам делителя-счетчика 2. Разряды делителя-счетчика 2 условно разделены на группы 6, 7 младших и старших разрядов, к которым присоединены соответствующие узлы 8, 9 съема кода, входящие в узел 3 съема кода; вход узла 8 съема кода соединен с выходом узла 4 синхронизации непосредственно, а вход узла 9 съема кода группы старших разрядов - через дополнительный логический формирователь 10 другие входы которого присоединены к выходам группы 6 младших разрядов делителя 2.

Устройство работает следующим образом.

При подаче импульса съема кода на вход узла 4 синхронизации, на его выходе формируется импульс, совпадающий во времени с вторым полупериодом сигнала задающего генератора / (считают, что импульсы запуска

де.чителя совпадают с первых) нолупериодом). Разряд) делителя на делят из условия, что максимальное время переноса единицы в группе меньше половины полупериода

входного сигнала группы. Поэтому в течение первого полупериода все переходные процессы в группе 6 младших разрядов уже заканчиваются, и импульс съема кода с выхода узла 4, «привязанный ко второму полупериоду, подается непосредственно на вход узла 8 съема кода группы младших разрядов. При этом на выходных шинах 5 группы младших разрядов возникают импульсы, соответствующие коду числа, содержащемуся в данный момент в

группе младших разрядов 6.

На вход узла 9 съема кода группы старших разрядов 7 синхронизированный импульс с узла 4 подается через дополнительный логический формирователь 10.

Если синхронизирующий импульс происходит в течение второго полупериода выходного сигнала грушпы 6 младших разрядов (являющегося входным для группы 7 старщих разрядов) , то оп передается на вход узла 9 без

задержки; если же импульс приходит в течение первого полупериода, выходного сигнала группы младших разрядов, то он передается на вход узла 9 с задержкой до второго полупериода выходного сигнала группы младших

разрядов. Таким образом, съем кода числа с группы 7 старших разрядов происходит во втором полупериоде входного сигнала данной группы, когда по услови 0 все переходные про-. цессы в группе уже закончились и код может

быть снят без ошибки. При поступлении импульса на вход узла 9, на его выходных шинах 5 формируется код числа, содержащегося в старших разрядах. Задержка съема кода старших разрядов до второго полупериода

входного сигнала группы не вносит ошибки, так как счетные импульсы приходят на вход группы один раз в период входного сигнала, а в интервале между ними других счетных импульсов не поступает.

Раздельный счет кода с групп младших и старших разрядов обеспечивает высокую точность съема и в тех случаях; когда максимальное время установления комбинации во всех разрядах делителя превышает период

сигнала задающего генератора. Поэтому можно строить делитель-счетчик по самой экономичной и надежной схеме с последовательным переносом единицы из младших разрядов в старшие; при этом частота входного сигнала

при переходе к старшим разрядам снижается, а требования к их быстродействию уменьшаются. В большинстве случаев достаточно разделить разряды на две группы, так как уже пять двоичных разрядов в младшей группе

снижают частоту входного сигнала старшей группы в раза. Но это значит, что в старщей группе необходимые условия будут выполняться для двоичных разрядов того же быстродействия, что и младшие,

или для 32 разрядов, в 5 раз меньшее быстродействие. Очевидно, этого вполне достаточно в большинстве практических случаев (25-30 разрядов). Очевидно, реализация узлов уотройст1вва технических трудностей не вызывает.

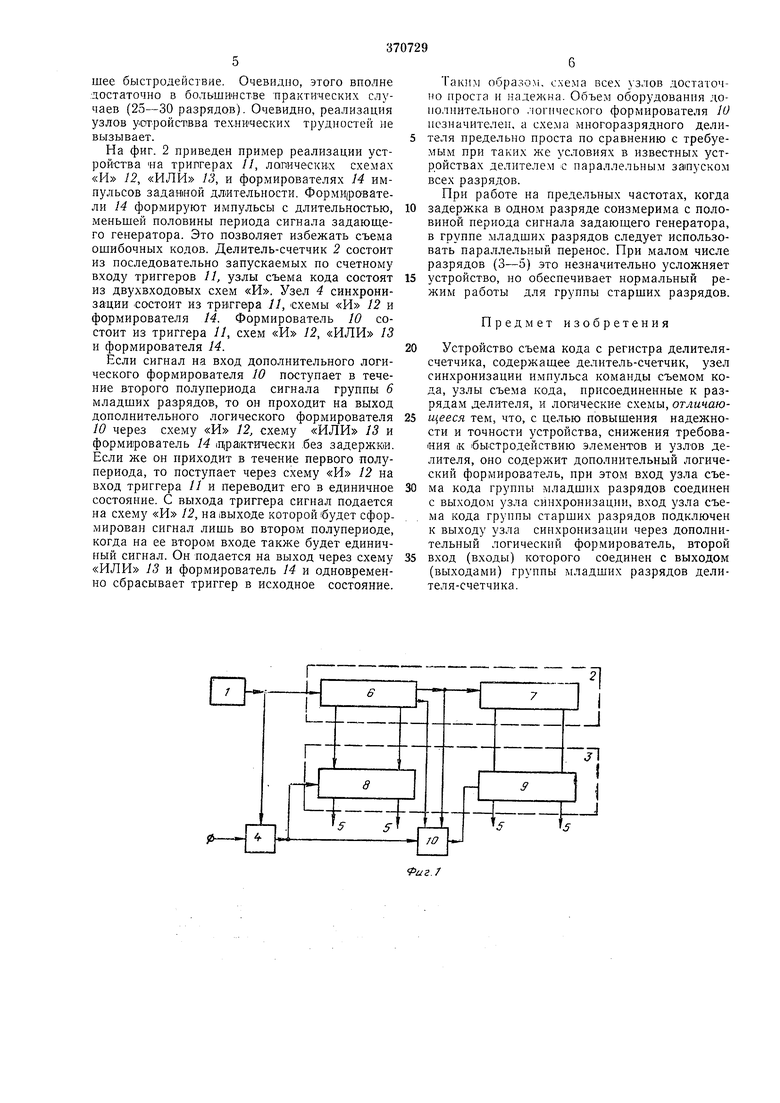

На фиг. 2 приведен пример реализации устройства «а триггерах //, лопичеСки.х схемах «И 12, «ИЛИ 13, и формирователях М импульсов задаиной длительности. Формиро-ватели 14 формируют импульсы с длительностью, меньшей половины периода сигнала задаюш.его генератора. Это позволяет избежать съема ошибочных кодов. Делитель-счетчик 2 состоит из последовательно запускаемых по счетному входу триггеров 11, узлы съема кода состоят из двухвходовых схем «И. Узел 4 синхронизации -состоит из триггера 11, схемы «И 12 и формирователя 14. Формирователь 10 состоит из триггера 11, схем «И 12, «ИЛИ 13 и формирователя 14.

Если сигнал на вход дополнительного логического формирователя 10 поступает в течение второго полупериода сигнала группы 6 младших разрядов, то он проходит на выход дополнительного логического формирователя 10 через схему «И 12, схему «ИЛИ 13 и формирователь 14 1црактически .без задержки. Если же он приходит в течение первого полупериода, то поступает через схему «И 12 на вход триггера // и переводит его в единичное состояние. С выхода триггера сигнал подается на схему «И 12, на выходе которой будет сформирован сигнал лишь во втором полупериоде, когда на ее втором входе также будет единичный сигнал. Он подается на выход через схему «ИЛИ 13 и формирователь 14 и одновременно сбрасывает триггер в исходное состояние.

Таким образом, с.хе.ма всех узлов достаточно проста и надежна. Объем оборудования дополнительного .чогического формирователя 10 незначителен, а схе.ма многоразрядного делителя предельно проста по сравнению с требуемым при таких же условиях в известных устройствах делителем с параллельным запуском всех разрядов.

При работе на предельных частотах, когда

задержка в одном разряде соизмерима с половиной периода сигнала задающего генератора, Б группе младших разрядов следует использовать параллельный перенос. При малом числе разрядов (3-5) это незначительно усложняет

устройство, но обеспечивает нормальный режим работы для группы старших разрядов.

Предмет изобретения

Устройство съема кода с регистра делителясчетчика, содержашее делитель-счетчик, узел синхронизации импульса команды съемом кода, узлы съема кода, присоединенные к разрядам делителя, и логические схемы, отличающееся тем, что, с целью повышения надежности и точности устройства, снижения требования iK быстродействию элементов и узлов делителя, оно содерл ит дополнительный логический формирователь, при этом вход узла съема кода группы младших разрядов соединен с выходом узла синхронизации, вход узла съема кода группы старших разрядов подключен к выходу узла синхронизации через дополнительный логический формирователь, второй вход (входы) которого соединен с выходом (выходами) группы младших разрядов делителя-счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДИСКРЕТНОГО ИЗМЕНЕНИЯ ФАЗЫСИГНАЛА | 1971 |

|

SU306559A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Одноканальное цифровое устройство для управления @ -фазным @ -пульсным вентильным преобразователем | 1990 |

|

SU1757057A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

Авторы

Даты

1973-01-01—Публикация