1

Изобретение относится к области вычислительной техники и может найти применение в цифровых вычислительных системах.

Известны делители частоты с нечетным коэффициентом деления, содержащие двоичный счетчик.

Однако эти устройства не позволяют использовать максимально достижимое быстродействие счетного триггера принятой элементной базы, так как для обеспечения заданного коэффициента пересчета используют петли обратной связи, в которые входит и триггер младшего разряда.

С целью повышения быстродействия в предлагаемом делителе прямой и инверсный выходы триггера первого разряда двоичного счетчика подключены к счетному входу триггера второго разряда через переключатель, управляюш,и.й вход которого соединен с выходом двоичного счетчика.

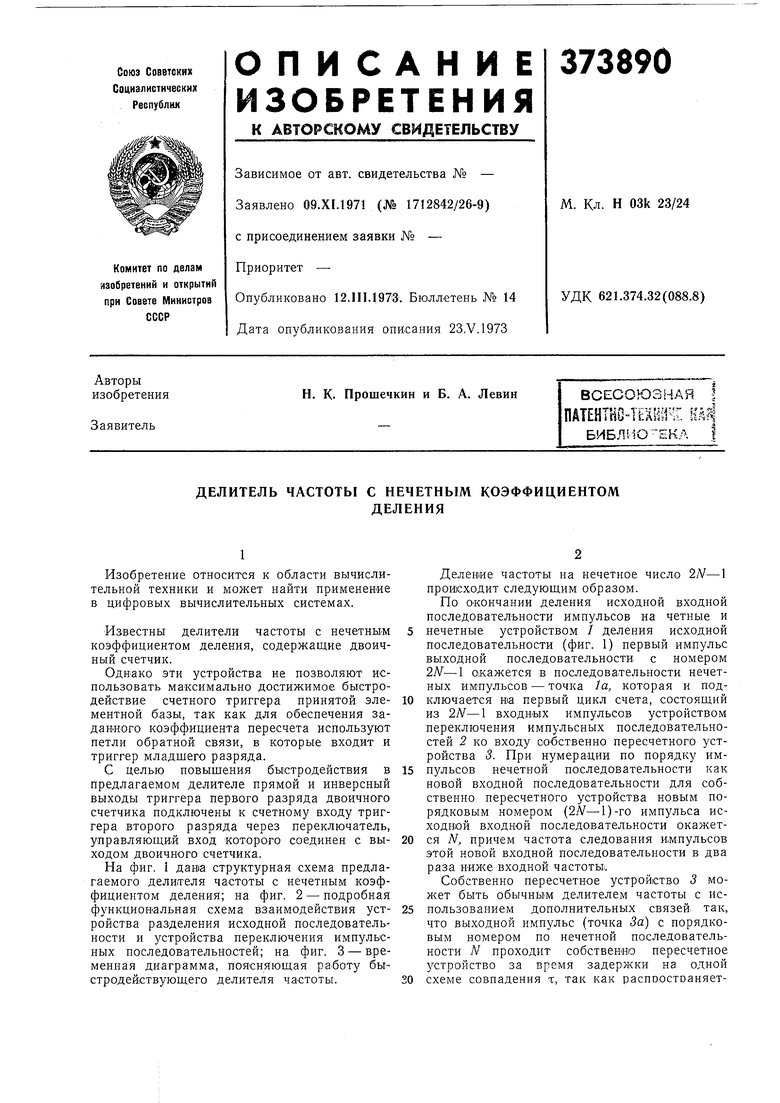

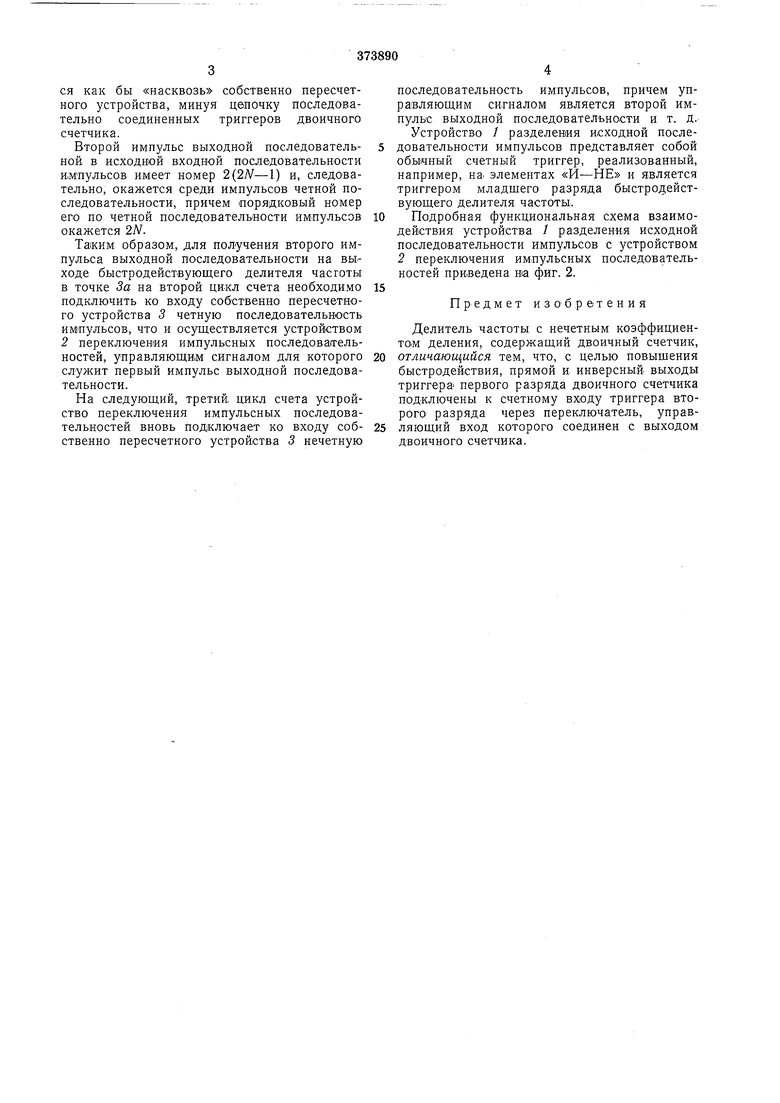

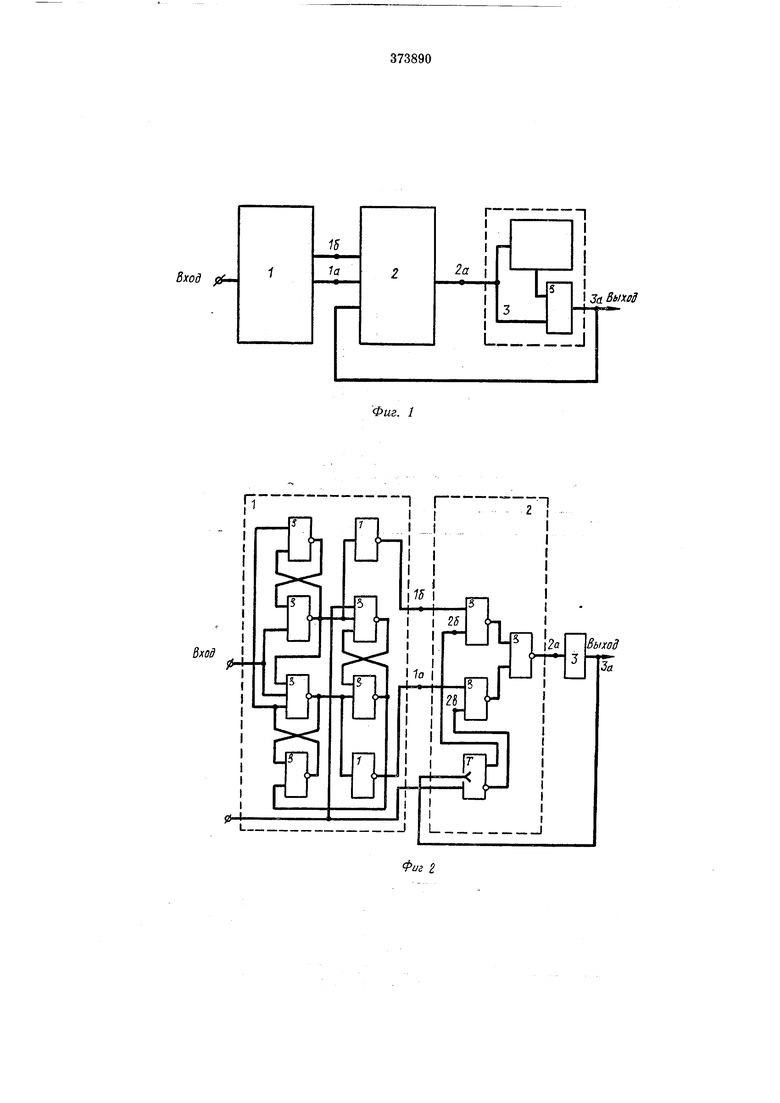

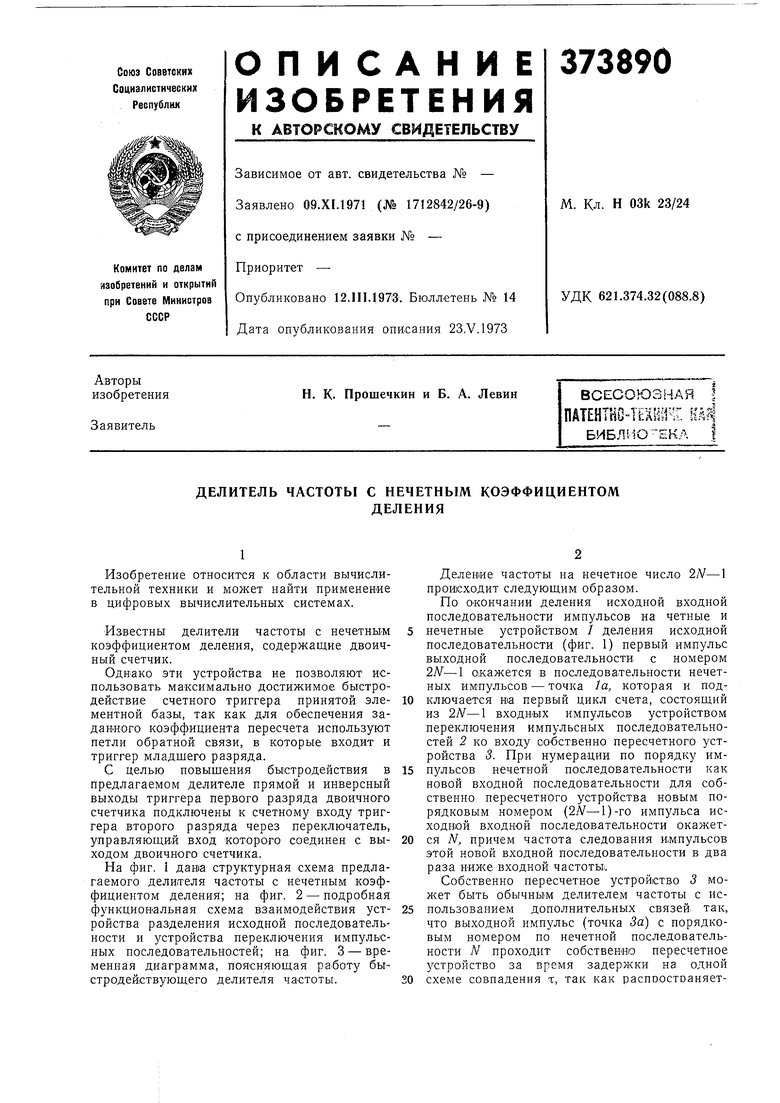

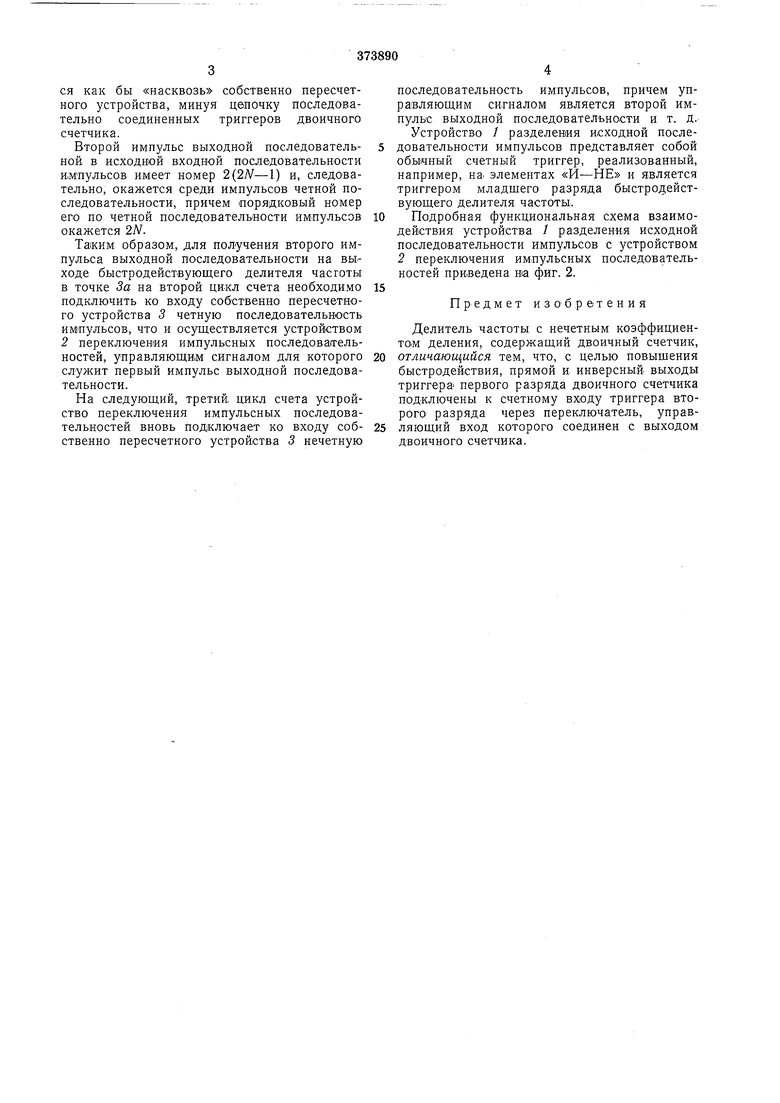

На фиг. 1 дааа структурная схема предлагаемого делителя частоты с нечетным коэффициентом деления; на фиг. 2 - подробная функциональная схема взаимодействия устройства разделения исходной последовательности и устройства переключения импульсных последовательно.стей; на фиг. 3 - временная диаграмма, поясняющая быстродействующего делителя частоты.

Деление частоты на нечетное число 2Л-1 происходит следуюшим образом.

По окончании деления исходной входной последовательности импульсов на четные и нечетные устройством / деления исходной последовательности (фиг. 1) первый импульс выходной последовательности с номером 2Л-1 окажется в последовательности нечетных импульсов - точка 1а, которая и подключается Hia первый цикл счета, состоящий из 2N-1 входных импульсов устройством переключения импульсных последовательностей 2 ко входу собственно пересчетного устройства 3. При нумерации по порядку импульсов нечетной последовательности как новой входной последовательности для собственно пересчетного устройства новым порядковым номером (2Л-1)-го импульса исходной входной последовательности окажется N, причем частота следования импульсов этой новой входной последовательности в два раза входной частоты.

Собственно пересчетное устройство 3 может быть обычным делителем частоты с использованием дополнительных связей так, что выходной импульс (точка За) с порядковым номерам по нечетной последовательности Л проходит собственно пересчетное устройство за время задержки на одной схеме совпадения т, так как распоостоаняется как бы «насквозь собственно пересчетного устройства, минуя цепочку последовательно соединенных триггеров двоичного счетчика.

Второй импульс выходной последовательной в исходной входной последовательности им пульсов имеет номер 2(2N-1) и, следовательно, окажется среди импульсов четной последовательности, причем порядковый номер его по четной последовательности импульсов окажется 2Л.

Таким образом, для получения второго импульса выходной последовательности на выходе быстродействующего делителя частоты в точке За на второй ци-кл счета необходимо подключить ко входу собственно пересчетного устройства 3 четную последовательность импульсов, что и осуществляется устройством 2 переключения импульсных последовательностей, управляющим сигналом для которого служит первый импульс выходной последовательности.

На следующий, третий, цикл счета устройство переключения импульсных последовательностей вновь подключает ко входу собственно пересчетного устройства 5 нечетную

последовательность импульсов, причем управляющим сигналом является второй импульс выходной последовательности и т. д.

Устройство / разделения исходной последовательности импульсов представляет собой обычный счетный триггер, реализованный, например, на элементах «И-НЕ и является триггером младшего разряда быстродействующего делителя частоты.

Подробная функциональная схема взаимодействия устройства / разделения исходной последовательности импульсов с устройством 2 переключения импульсных последовательностей приведена nia фиг. 2.

Предмет изобретения

Делитель частоты с нечетным коэффициентом деления, содержащий двоичный счетчик, отличающийся тем, что, с целью повыщения быстродействия, прямой и инверсный, выходы триггера- первого разряда двоичного счетчика подключены к счетному вх-оду триггера второго разряда через переключатель, управляющий вход которого соединен с выходом двоичного счетчика.

Вход f

За 3i /xffJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с нечетным коэффициентом деления (его варианты) | 1982 |

|

SU1132368A1 |

| Устройство для формирования импульсной последовательности | 1983 |

|

SU1171999A1 |

| Управляемый делитель частоты | 1978 |

|

SU741474A2 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Перестраиваемый делитель частоты | 1977 |

|

SU678672A1 |

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| Управляемый делитель частоты | 1976 |

|

SU658741A1 |

| Делитель частоты следования импульсов | 1981 |

|

SU1001484A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

Вход

Фиг. 1

1

/ 23 2M-Z 2N1 2N 2/r/V-rJ-J 2/2fJ-1j Zl2N-l 1

Авторы

Даты

1973-01-01—Публикация