Изобретение относится к вычислительной технике.

Известные многофункциональные запоминающие устройства, реализующие арифметические и логические оп-ерации, имеют больщое количество оборудования, необходимого для реализадии распространения переносов (цепочка переносов, триггерный регистр числа).

Для повышения надежности предлагаемое устройство дололнительно содержит логический блок, выполненный на мнютоотверстных ферритовых пластинах с двумя отверстиями на разряд с магнитной связью, одн-о из Которых запоминающее, а другое -переключающее, причем оба о.тверстия прошиты разрядной шиной согласно и встречно по отношению к числовой шине, запоминаюшие отверстия предыдущего младшего разряда логического прошиты выходными шинами, а выходы усилителей считыв.ания подключены к входам одноименных разрядных формирователей.

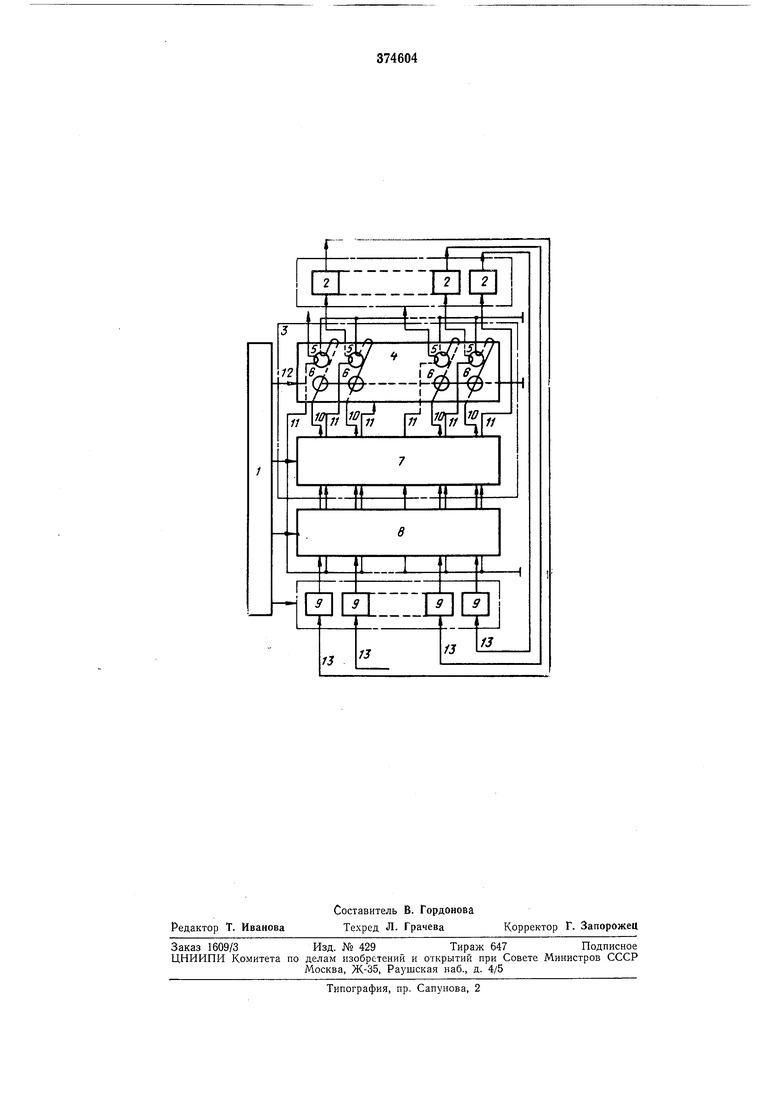

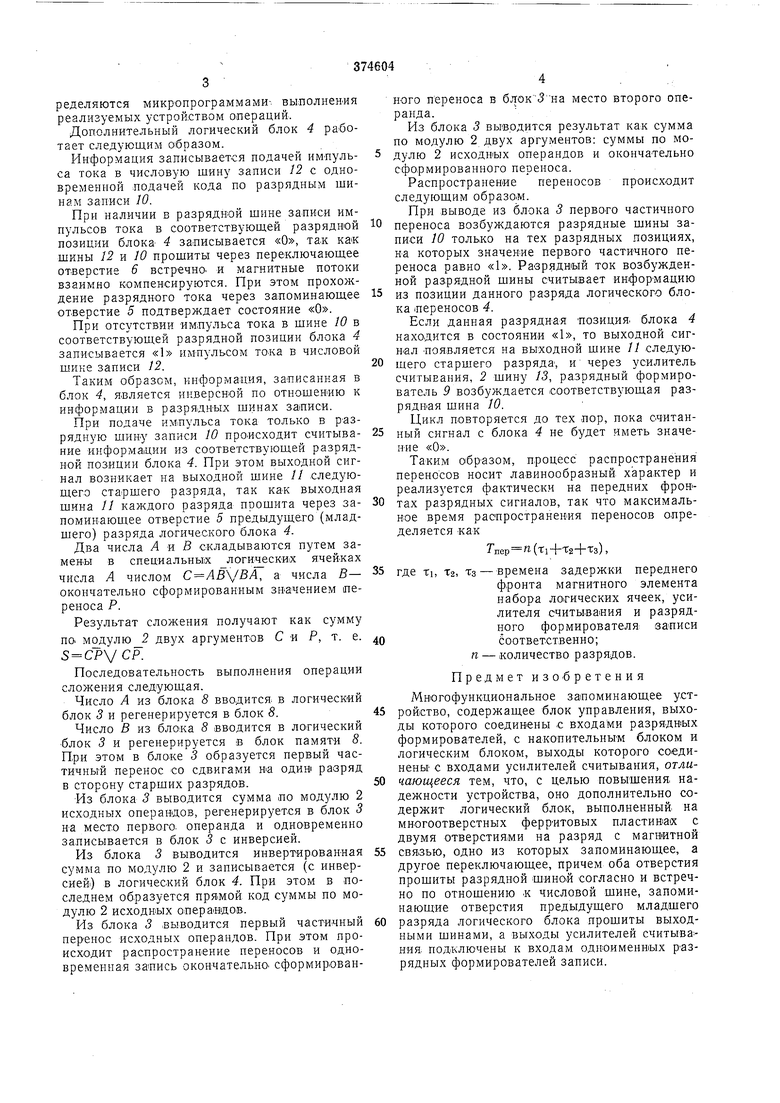

На чертеже изображена схема предлагаемого устройства.

Устройство содержит блок управления }, усилители считывания 2, логический блок 5, содержащий дополнительный Логический блок 4 ва многоотверстпой ферритовой пластине с двумя отверстиями на разряд, одно из

которых запоминающее 5, а другое переключающее 6, и набор логических ячеек 7, накопительный блок 8, разрядные формирователи записи 9, разрядные шины записи 10, выходпые шины //, числовую щину записи 12, шины 13 связи выходов усилителей считывания и входов одноименных разрядов фо.рмирователей.

Каждая разрядная шина записи Ю прошита через соответствующие переключающее 6 и запоминающее 5 отверстия логического блока .переносов 4 согласно и встречно по отношению к числовой щине записи 12.

Выходная шина // каждого разряда прошита через запоминающее отверстие 5 предыдущего разряда блока 4 (на чертеже самый младший разряд справа). Выходы усилителей 2 соединены шинами

связи 13 со входами одноименных разрядных формирователей записи 9.

Шины 10 и // являются общими для блоков 3 и 8. Устройство работает следующим образом.

Блок управления / вырабатывает последовательность сигналов, управляющих работой всех узлов устройства. Все операции выполняются путем организации блоком / последовательности пересылок кодов между ячейками блоков 3 и 8. Эти последовательности onределяются микропрограммами- выполнеиия реализуемых устройством операций.

Дополнительный логический блок 4 ра ботает следующим 01бразом.

Информация записывается подачей им-пульса тока в числовую шину записи 12 с одновременной лодачей кода по разрядным шинам записи 10.

При наличии в разрядной шине записи импульсов тока в соответствующей разрядной позиции блока 4 записывается «О, та-к как шины 12 и 10 прошиты через переключающее отверстие 6 встречно, и магнитные потоки взаимно компенсируются. При этом прохождение разрядного тока через запоминающее отверстие 5 подтверждает состояние «О.

При отсутствии импульса тока в шине 10 в соответствующей разрядной позиции блока 4 записывается «1 импульсом тока в числовой щине записи 12.

Таким образом, информация, записанная в блок 4, является инверсной по отношен ию к информации в разрядных шинах записи.

При подаче импульса тока только в р азрядную шипу записи 10 происходит считывание информации из соответствующей разрядной позиции блока 4. При этом выходной сигнал возникает на выходной шине // следующего старшего разряда, так как выходная щина // каждого разряда прощита через запоминающее отверстие 5 предыдущего (младшего) разряда логического блока 4.

Два числа Л и S складываются путем замены в специальных логич ески1Х ячейках числа А числом а числа В- окончательно сформированным зн-ачением переноса Р.

Результат сложения получают как сумму по. модулю 2 двух аргументов С и Р, т. е. 5 CPVCR

Последовательность выполнения операции сложения следующая.

Число А из блока 8 вводится в логический блок 3 и регенерируется в блок 8.

Число В из блока 8 вводится в логический блок 3 и регенерируется в блок памяти 8. При этом в блоке 3 образуется первый частичный перенос со сдвигами Hia одив разряд в сторону старших разрядов.

Из блока 3 выводится сумма по модулю 2 исходных операндов, регенерируется в блок 3 на место первого, операнда и одновременно записывается в блок 3 с инверсией.

Из блока 3 выводится инвертированная сумма по модулю 2 и записывается (с инверсией) в логический блок 4. При этом в последнем образуется прямой код суммы по модулю 2 исходных операндов.

Из блока .3 выводится первый частичный перенос исходных операндов. При этом происходит распространение переносов и одновременная запись окончательно. сформир.ованного переноса в б.яок5 на место второго операнда.

Из блока 5 выводится результат как сумма по модулю 2 двух аргументов: суммы по модулю 2 исходных операндов и окончательно сформированного переноса.

Распространение переносов происходит следующим образо.м.

При выводе из блока 3 перво.го частичного переноса возбуждаются разрядные щины записи 10 только на тех разрядных позициях, на которых значение первого частичного переноса равно «1. Раврядный ток возбужденной разрядной щины считывает ин|формацию из позиции данного разряда логического блока переносов 4.

Если данная разрядная позиция, блока 4 нахо.дится в состоянии «1, то выходной сигнал .появляется на выходной шине И следующего старшего разряда; и через усилитель считывания, 2 щину /5, разрядный формирователь 9 возбуждается соответствующая разрядная щина 10.

Цикл повторяется до тех пор, пока считанный сигнал с блока 4 не будет иметь значение «О.

Таким Образом, процесс распространения переносов носит лавинообразный характер и реализуется фактически на передних фронтах разрядных сигналов, так что максимальное время распространения переносов о.пределяется .как

7nep n(Ti+T:2-fT3),

где ть Т2, тз -времена задержки переднего фронта магнитного элемента набора логических ячеек, усилителя считывания и разрядного формирователя записи соответственно; п - количество разря.дов.

Предмет изо.бретения

Многофункциональное запоминающее устройство, содержащее блок управления, выходы которого соединены с входами разря.дных формирователей, с накопительным блоком и логическим блоком, выходы которого соединены с входами усилителей считывания, отличающееся тем, что, с целью повышения, надежности устройства, оно дополнительно содержит логический бло.к, выполненный, на многоотверстных ферритовых пластивак с двумя отверстиями на разряд с магнитной связью, одно из которых запоминающее, а другое переключающее, причем оба отверстия прощиты разрядной щино« согласно и встречно по отношению .к числовой шине, запоминающие отверстия предыдущего младшего разряда логического блока прощиты выходными щинами, а выходы усилителей считыва ния. подключены к входам одноименных р азрядных формирователей записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368605A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432495A1 |

| Запоминающее устройство | 1973 |

|

SU481938A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| СЕМ. Кл. G Не 11/06УДК 681.327.66(088.8) | 1973 |

|

SU404129A1 |

| МНОГОКАНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU224589A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Трансформаторное постоянное запоминающее устройство | 1977 |

|

SU733027A1 |

Авторы

Даты

1973-01-01—Публикация